合成実行なしのクリティカル パスの推定

クリティカル パスとは、タイミング遅延が最大になる入力と出力との間を組み合わせたパスです。設計内のクリティカル パスを見つけるには、HDL Coder™ を使用します。クリティカル パスのタイミングを設計で達成すべきターゲット周波数に一致させるには、遅延を追加してクリティカル パスを分割します。追加の遅延により、ターゲット ハードウェア上のレイテンシとレジスタ使用数は増加します。

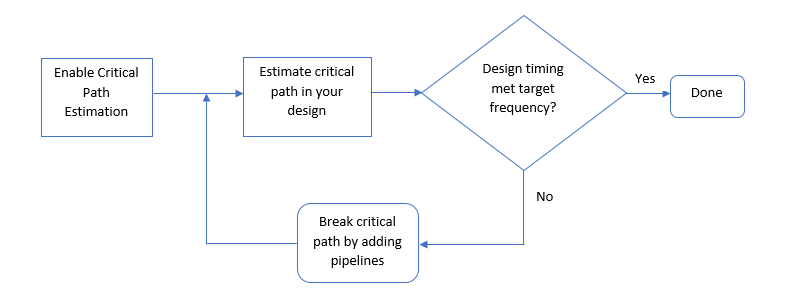

クリティカル パスの可能性が最も高いパスを設計内で簡単に特定するには、クリティカル パスの推定を使用します。合成を実行したり、HDL コードを生成したりする必要はありません。クリティカル パスの推定は、クリティカル パスを検出する反復的プロセスを高速化します。必要とするターゲット周波数と設計のタイミングが一致するまでクリティカル パスが最適化されます。

クリティカル パスの推定は、設計反復プロセスを高速化します。クリティカル パスの推定は、HDL ワークフロー アドバイザーで [FPGA 合成および分析] を実行して、クリティカル パスに注釈付けすることの代替方法です。

クリティカル パスの推定プロセス

HDL Coder は、ターゲット固有のタイミング データベースのタイミング データを使用して静的タイミング解析を実行することにより、推定クリティカル パスを見つけます。関数 genhdltdb を使用して、指定したターゲット デバイス ファミリ、ターゲット デバイス スピード グレード、およびターゲット ツールのタイミング データベースを生成します。既定では、HDL Coder には、以下のターゲット デバイスのタイミング データベースがあります。

Altera® Cyclone V

Intel® Stratix V

Xilinx® Artix®-7、スピード グレード -1

Xilinx Kintex®-7、スピード グレード -1

Xilinx KintexUltraScale™、スピード グレード -1

Xilinx Virtex®-4、スピード グレード -10

Xilinx Virtex-7、スピード グレード -1

Xilinx Zynq®、スピード グレード -1

Xilinx ZynqUltraScale+™、スピード グレード -1

タイミング データベースを作成するため、HDL Coder では、Simulink® ブロック、ブロック アーキテクチャおよびこれらのブロックのサブコンポーネントなどの基本的な設計コンポーネントを特定のターゲット デバイスに対して特徴付けます。

コード ジェネレーターがモデル設計を解析して、タイミング データベース内のブロックとサブコンポーネントに分解します。設計がタイミング データベース内のブロックまたはサブコンポーネントで構成されている場合、コード ジェネレーターはタイミングのクリティカル パスをより正確に推定できます。設計がタイミング データベース以外のコンポーネントを使用する場合は、個別の強調表示スクリプトが生成されて、特徴付けられていないブロックを示します。タイミング データが設計の一部に対して不完全な場合、推定クリティカル パスが実際のクリティカル パスと一致しない可能性があります。

ターゲットのハードウェアがクリティカル パスの推定でサポートされているいずれかのターゲット デバイスである場合、タイミングの数と推定クリティカル パスの精度はより高くなります。ターゲットのハードウェアがサポートされているデバイスではない場合や、同じデバイス ファミリにはない場合でも、クリティカル パスを推定することはできますが、タイミングの数は正確ではなくなる可能性があります。

クリティカル パスの推定の使用

設計のクリティカル パスは、[コンフィギュレーション パラメーター] ダイアログ ボックスまたはコマンド ラインで推定できます。[コンフィギュレーション パラメーター] ダイアログ ボックスでクリティカル パスを推定するには、以下を行います。

クリティカル パスの推定レポートの生成を有効にします。

[アプリ] タブで、[HDL Coder] を選択します。

[HDL コード] タブで、[設定] 、 [レポート オプション] を選択し、[高位のタイミング クリティカル パス レポートを生成] を選択します。

ターゲット デバイスに対して生成されたタイミング データベースのパスを設定します。[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [レポート] ペインで [高位のタイミング クリティカル パス レポートを生成] パラメーターを選択してから、[参照] をクリックしてターゲット フォルダーを選択することで、生成されたタイミング データベースのパスを設定します。

既定では、ターゲット フォルダーには、保存されたタイミング データベースのフォルダーの一部がターゲット構成に基づいて表示されます。[カスタム タイミング データベースのディレクトリ] ボックスが空であるか、ターゲット構成にタイミング データベースがない場合、既定では、HDL Coder は Xilinx Virtex-7、スピード グレード -1 のデバイスのタイミング データベースを使用して、クリティカル パスの推定レポートを生成します。

関数

genhdltdbを使用して、指定したターゲット デバイス ファミリ、ターゲット デバイス スピード グレード、およびターゲット ツールのタイミング データベースを生成することもできます。モデルの HDL コードを生成せずにクリティカル パスの推定レポートを生成するには、[HDL コード生成] 、 [グローバル設定] 、 [詳細設定] タブで、[HDL コードを生成] チェック ボックスをオフにします。

設計のクリティカル パスを推定するために、完全なコード生成プロセスを実行する必要はありません。これにより、特に大規模なモデルにおいて、クリティカル パスの推定にかかる時間が節約されます。

クリティカル パスの推定レポートを生成するには、設計に対して

makehdlを実行します。

HDL Coder は、クリティカル パスの推定レポートを生成し、MATLAB® コマンド ウィンドウに強調表示するスクリプトと強調表示を解除するスクリプトへのリンクを含むメッセージを表示します。

レポートをコマンド ラインで生成するには、以下のコードを使用します。クリティカル パスの推定を行う設計に基づき、変数 modelname および dutname を指定します。関数 hdlset_param を使用して、ターゲット デバイスに対して生成されたタイミング データベースのパスを設定します。クリティカル パスの推定レポートの生成を有効にしているときに、ターゲット デバイスのタイミング データベースのパスを設定しない場合、HDL Coder は、指定されたターゲット デバイス ファミリおよびターゲット デバイス スピード グレードの既定のタイミング データベースを検索します。指定されたターゲット デバイスのタイミング データベースを利用できない場合、既定では、HDL Coder は Xilinx Virtex-7、スピード グレード -1 のデバイスのタイミング データベースを使用して、クリティカル パスの推定レポートを生成します。この例では、sfir_single モデルを使用します。

% Specify model and subsystem names modelname = 'sfir_single'; dutname = 'sfir_single/symmetric_fir'; open_system(modelname) % Disable HDL code generation for faster generation % of critical path estimation report hdlset_param(modelname,'CriticalPathEstimation','on'); hdlset_param(modelname,'GenerateHDLCode','off'); % If design contains single data types, % enable native floating-point support fpconfig = hdlcoder.createFloatingPointTargetConfig('NativeFloatingPoint'); hdlset_param(modelname,'FloatingPointTargetConfig',fpconfig); % Set path of generated timing databases for target device hdlset_param(modelname,'TimingDatabaseDirectory','C:\Work\Database'); % Generate report makehdl(dutname)

criticalpathestimated スクリプトへのリンクをクリックすると、コード ジェネレーターは生成されたモデル内でクリティカル パスを強調表示します。生成されたモデル内に、クリティカル パスのタイミング情報と、そのパス上にあるブロックが表示されます。この図は、Simulink モデルのクリティカル パスに注釈が付けられた部分を示しています。ネイティブの浮動小数点演算子は薄い青で強調表示され、遅延はオレンジで強調表示されます。クリティカル パスの一部であるブロックは濃い青で強調表示され、ブロックの横に注釈としてクリティカル パスの値が示されます。詳細については、生成されたモデルと検証モデルを参照してください。

強調表示をオフにするには、clearhighlighting スクリプトへのリンクをクリックします。

クリティカル パスを最適化するには、パイプライン レジスタを追加して、クリティカル パスを分割します。[浮動小数点の使用] を選択してネイティブ浮動小数点を使用する場合は、[LatencyStrategy] を [Max] に設定してタイミングを改善します。クリティカル パスの推定レポートと、設計のクリティカル パスを強調表示するスクリプトを再生成します。このプロセスを、設計のタイミングが必要とするターゲット周波数に一致するまで繰り返します。

特徴付けられるブロック

Simulink ブロックのサブセットは、固定小数点型と単精度のネイティブ浮動小数点型で特徴付けることができます。これらのブロックは、サポートされる各ターゲット デバイスのタイミング データベースの一部です。コード生成レポートを生成すると、[クリティカル パスの推定] セクションに、特徴付けることができなかったブロックのリストが含まれます。

設計に MATLAB function ブロックがあり、HDL ブロック プロパティ [アーキテクチャ] が [MATLAB Function] に設定されている場合、クリティカル パスの推定時や HDL コードの生成時に、MATLAB function ブロックが特徴付けられていないブロックとしてコード生成レポートに表示されることがあります。MATLAB function ブロックを特徴付けるには、[アーキテクチャ] を [MATLAB Datapath] に設定します。

MATLAB Function ブロックを使用し、[MATLAB Datapath] アーキテクチャを使用してコードを生成するときに、HDL Coder は MATLAB アルゴリズムを生成されたモデルで Simulink ブロック線図に変換します。生成されたモデルでは、クリティカル パスの推定によって MATLAB Function ブロック内、および MATLAB Function ブロック境界を越えた他の Simulink ブロックとの間のクリティカル パスに注釈を付けることができます。MATLAB Datapath アーキテクチャを使用した、MATLAB Function ブロック境界を越えた HDL 最適化も参照してください。

考慮事項

マルチレート モデルのクリティカル パスの推定

クリティカル パスの推定は、設計内の異なるシーケンシャル要素へのクロックゲーティング情報を考慮しません。

モデルに複数のサンプルレートが含まれている場合またはパイプライン レジスタを挿入する速度と面積の最適化を使用している場合、設計はマルチレートになり、設計にマルチサイクル パスが含まれる可能性があります。マルチレート モデルの場合、クリティカル パスの推定では遅いデータ パスと速いデータ パスを同じレートで実行するものとして扱います。設計内の別のデータ パスのクロックレートがより遅い場合、レートがより速いデータ パスがクリティカル パスとして強調表示される場合があります。この問題により、不正確なタイミング結果を報告するクリティカル パスの推定が生じる可能性があります。

推定クリティカル パス情報を検証するには、HDL ワークフロー アドバイザーを開き、ターゲット デバイスの [Generic ASIC/FPGA] ワークフローを [合成結果をもつモデルに注釈を付ける] タスクに対して実行します。

ネイティブ浮動小数点モードでのクリティカル パスの推定

設計に single データ型が含まれており、[浮動小数点の使用] を選択して Native Floating Point モードを使用する場合、クリティカル パスの推定スクリプトは、生成されたモデル内の single 浮動小数点演算子を強調表示することがあります。コード ジェネレーターが single ブロックを強調表示するのは、浮動小数点アルゴリズムには膨大な計算量が必要であるためです。浮動小数点演算子内部のレジスタ間パスがクリティカル パスになることがあります。

その場合、クリティカル パスのタイミングを最適化するには、その演算子に対応する Simulink ブロックで、[LatencyStrategy] を [最大値] に設定します。

半精度データ型を使用する Simulink ブロックはクリティカル パスの推定に使用されません。これらのブロックは 0 ns のタイミング遅延を使用して強調表示されます。

クリティカル パスの推定の不正確性

クリティカル パスの推定は、推定係数を使用して経路による遅延を考慮しようとします。配置配線を実行しないと、経路による遅延を正確に考慮するのは困難です。

HDL Coder は、組み合わせの性質を持つ特徴付けられないブロックを、ゼロ遅延の組み合わせブロックとして推測します。コード ジェネレーターはその他のブロックをレジスタとして扱います。

参考

hdlcoder.FloatingPointTargetConfig | makehdl | genhdltdb | hdlcoder.TimingGenerator