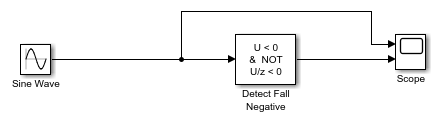

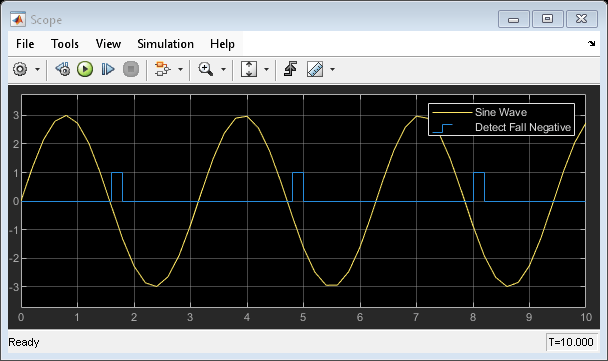

Detect Fall Negative

信号値が厳密に負の値に減少し、前の値が非負のときに、立ち下がりエッジを検出

ライブラリ:

Simulink /

Logic and Bit Operations

説明

Detect Fall Negative ブロックは、入力がゼロ未満かどうか、また前の値がゼロ以上であるかどうかを判断します。

このブロックは離散サンプル時間のみをサポートしています。

例

端子

詳細については、Simulink でサポートされているデータ型を参照してください。

入力

出力

パラメーター

ブロックの特性

データ型 |

|

直達 |

|

多次元信号 |

|

可変サイズの信号 |

|

ゼロクロッシング検出 |

|