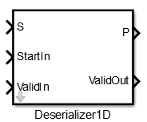

Deserializer1D

スカラー ストリームまたは小さいベクトルからベクトル信号への変換

ライブラリ:

HDL Coder /

HDL Operations

説明

Deserializer1D ブロックは、高速なスカラー ストリームまたはベクトル信号を大きな低速のベクトル信号にバッファリングします。高速な入力信号は、[比] 値および [アイドル サイクル] 値に基づいて低速な信号に変換されます。この変換ではサンプル時間が変化します。また、ベクトルとして出力可能になるまでシリアル化されたデータを収集する必要があるため、出力信号は低速信号の 1 サイクル分遅延します。詳細については次の例を参照してください。

有効な入力信号 ValidIn および開始信号 StartIn に依存するように逆シリアル化を設定できます。[入力有効] ブロック パラメーターおよび [入力開始] ブロック パラメーターが両方選択されている場合、データ収集は ValidIn 信号および StartIn 信号の両方が true のときのみ開始します。次の例を考えます。

[比] が

2、[アイドル サイクル] が0であるため、各出力サイクルは入力信号 2 つ分の長さとなり、すべてのデータ点が考慮される。StartIn 信号および ValidIn 信号が両方とも true のときのみデータ収集を開始するように、[入力有効] および [入力開始] が選択されている。

[出力有効] が選択されている。

最初のサイクルでは、ValidIn および StartIn が true であるため、A および B のデータ収集を開始します。ブロックは次の有効なサイクルで逆シリアル化したベクトルを出力するため、AB ベクトルが次のサイクルの出力です。これは 2 番目のサイクルで C および D に対しても成り立ちます。

3 番目のサイクルでは E から始まり、StartIn が true ですが、ValidIn は true ではありません。E は破棄されます。F では、ValidIn が true ですが StartIn が true ではないため、F も破棄されます。E および F のデータは収集されないため、Deserializer1D は前回サイクルのベクトル CD を出力しますが、ValidOut は false に変化します。

考察する次のシナリオは、StartIn 信号の到着が早すぎる場合です。2 つの StartIn 信号間に十分な長さがなく、比率サイクル全体を収集できない場合、不十分な信号データは破棄されます。次の例を考えます。

[比] が

3であるため、各サイクルは 2 つのセクションの長さとなる。[アイドル サイクル] が

0であるため、データ点はすべて考慮される。StartIn 信号および ValidIn 信号が両方とも true のときのみデータ収集を開始するように、[入力有効] および [入力開始] が選択されている。

[出力有効] が選択されている。

最初のサイクルでは、ValidIn および StartIn が true であるため、A および B のデータ収集を開始できます。しかし、3 つの信号が収集される前に、C で別の StartIn 信号が到着します。StartIn が早く到着したため、A および B が破棄され、最初のサイクルでは有効なベクトルが収集されません。したがって、2 番目のサイクルの出力はゼロのままです。逆シリアル化は、C の StartIn で C、D、E に対して開始されます。このベクトルは、次の有効なサイクルである 3 番目のサイクルの出力となります。同様に、逆シリアル化は F の StartIn で再度開始され、FGH ベクトルが 4 番目のサイクルで出力されます。

最初のサンプリング周期のブロック出力は、[初期条件] パラメーターの値で指定します。