このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

Interval Test

指定した区間内に信号が存在するかどうかを判定

ライブラリ:

Simulink /

Logic and Bit Operations

説明

Interval Test ブロックは、[下限] パラメーターと [上限] パラメーターが指定した値の間に入力が存在する場合に true (1) を出力します。このブロックは、これらの値の外側に入力が存在する場合に false (0) を出力します。入力が [下限] または [上限] に等しいときのこのブロックの出力は、[左閉区間] チェック ボックスと [右閉区間] チェック ボックスのどちらをオンにするかによって決まります。

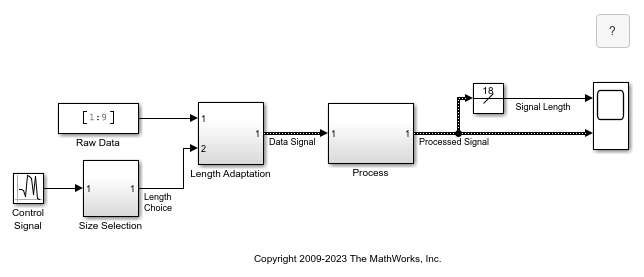

例

端子

入力

入力信号。スカラー、ベクトル、行列または N 次元配列として指定します。

制限

入力信号が列挙型の場合、[上限] 値と [下限] 値は同じ列挙型でなければなりません。

データ型: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated

出力

入力値が指定した区間にあるかどうかを示す出力信号。[出力データ型] は [boolean] または [uint8] として指定できます。

データ型: uint8 | Boolean

パラメーター

このチェック ボックスをオンにすると、このブロックが true (1) を出力する区間内に [上限] が含まれます。

プログラムでの使用

ブロック パラメーター: IntervalClosedRight |

| 型: 文字ベクトル |

値: 'on' | 'off' |

既定の設定: 'on' |

このブロックが true (1) を出力する区間の上限。

プログラムでの使用

ブロック パラメーター: uplimit |

| 型: 文字ベクトル |

| 値: スカラー | ベクトル | 行列 | N 次元配列 |

既定の設定: '0.5' |

このチェック ボックスをオンにすると、このブロックが true (1) を出力する区間内に [下限] が含まれます。

プログラムでの使用

ブロック パラメーター: IntervalClosedLeft |

| 型: 文字ベクトル |

値: 'on' | 'off' |

既定の設定: 'on' |

このブロックが true (1) を出力する区間の下限。

プログラムでの使用

ブロック パラメーター: lowlimit |

| 型: 文字ベクトル |

| 値: スカラー | ベクトル | 行列 | N 次元配列 |

既定の設定: '-0.5' |

出力データ型を boolean または uint8 として指定します。

プログラムでの使用

ブロック パラメーター: OutDataTypeStr |

| 型: 文字ベクトル |

値: 'boolean' | 'uint8' |

既定の設定: 'boolean' |

ブロックの特性

データ型 |

|

直達 |

|

多次元信号 |

|

可変サイズの信号 |

|

ゼロクロッシング検出 |

|

拡張機能

C/C++ コード生成

Simulink® Coder™ を使用して C および C++ コードを生成します。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加のコンフィギュレーション オプションがあります。

| アーキテクチャ | 説明 |

|---|---|

Module (既定値) | サブシステムとそのサブシステム内のブロックのコードを生成します。 |

BlackBox | ブラック ボックス インターフェイスを生成します。生成された HDL コードには、サブシステムの入力/出力端子定義のみ含まれます。したがって、モデル内のサブシステムを使用して、手動作成された既存の HDL コードへのインターフェイスを生成できます。 サブシステムのブラックボックス インターフェイスの生成は、クロック信号を使用しない Model ブロック インターフェイスの生成と似ています。 |

| 生成されたコードからサブシステムを削除します。シミュレーションでサブシステムを使用できますが、HDL コード内では "ノーオペレーション" として扱います。 |

[BlackBox] アーキテクチャについて、端子名をカスタマイズして、外部コンポーネントのインターフェイスの属性を設定できます。ブラック ボックスまたは HDL コシミュレーション インターフェイスのカスタマイズ (HDL Coder)を参照してください。

| 一般 | |

|---|---|

| AdaptivePipelining | 合成ツール、ターゲット周波数、乗算器の語長に基づくパイプラインの自動挿入。既定の設定は |

| ClockRatePipelining | パイプライン レジスタを低速のデータ レートではなく高速のクロック レートで挿入します。既定の設定は |

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

| DistributedPipelining | パイプライン レジスタの分散、またはレジスタのリタイミング。既定の設定は |

| DSPStyle | 乗算器のマッピングの合成属性。既定の設定は |

| FlattenHierarchy | 生成された HDL コードからサブシステム階層を削除します。既定の設定は |

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| SharingFactor | 単一の共有リソースにマッピングされる、機能的に等価なリソースの数。既定の設定は 0 です。リソース共有 (HDL Coder)も参照してください。 |

| StreamingFactor | 時間多重化されてシリアルのスカラー データ パスに変換される、パラレル データ パスの数、またはベクトルの数。既定値は 0 であり、パラレル データ パスがそのまま実装されます。ストリーミング (HDL Coder)も参照してください。 |

このブロックが DUT でない場合、[ターゲット仕様] タブのブロック プロパティ設定は無視されます。HDL ワークフロー アドバイザーで、IP コア生成ワークフローを使用すると、これらのターゲット仕様のブロック プロパティ値はモデルに保存されます。hdlset_param を使用してターゲット仕様のブロック プロパティ値を指定した場合、HDL ワークフロー アドバイザーを開くと、フィールドに対応する値が設定されています。

| ターゲット仕様 | |

|---|---|

| AdditionalTargetInterfaces | 追加のターゲット インターフェイス。文字ベクトルとして指定します。 このブロック プロパティをモデルで保存するには、インターフェイスを追加する DUT 端子に対応する IP コア生成ワークフローの [ターゲット インターフェイスを設定] タスクで [さらに追加] を選択します。これで、[Add New Target Interfaces] ダイアログ ボックスでさらにインターフェイスを追加できます。インターフェイスのタイプ、追加のインターフェイスの数、それぞれの追加のインターフェイスの一意の名前を指定します。 値: 例: |

| ProcessorFPGASynchronization | プロセッサ/FPGA 同期モード。文字ベクトルで指定します。 このブロック プロパティをモデルに保存する場合は、IP コア生成ワークフローの [ターゲット インターフェイスを設定] タスクで [プロセッサ/FPGA 同期] を指定します。 値: 例: |

| TestPointMapping | このブロック プロパティをモデルに保存するには、IP コア生成ワークフローの [ターゲット インターフェイスを設定] タスクで、テスト ポイント端子のターゲット プラットフォーム インターフェイスへのマッピングを指定します。 値: 例: |

| TunableParameterMapping | このブロック プロパティをモデルに保存するには、IP コア生成ワークフローの [ターゲット インターフェイスを設定] タスクで、調整可能なパラメーター端子のターゲット プラットフォーム インターフェイスへのマッピングを指定します。 値: 例: |

| AXI4RegisterReadback | このブロック プロパティをモデルに保存するには、IP コア生成ワークフローの [RTL コードと IP コアの生成] タスクにおいて、AXI4 下位書き込みレジスタでの再読み取りを有効にするかどうかを指定します。詳細については、AXI4 レジスタ インターフェイスの生成のための設計のモデル化 (HDL Coder)を参照してください。 値: |

| AXI4SlaveIDWidth | このブロック プロパティをモデルに保存するには、IP コア生成ワークフローの [RTL コードと IP コアの生成] タスクで [AXI4 スレーブ ID の幅] 設定を使用して、DUT IP コアを接続する AXI マネージャー インターフェイスの数を指定します。詳細については、DUT AXI4 スレーブ インターフェイスにアクセスするためのリファレンス設計での複数の AXI Master インターフェイスの定義 (HDL Coder)を参照してください。 値: |

| RegisterInterfaceReadPipeline | このブロック プロパティをモデルに保存するには、[IP コア生成] ワークフローの [RTL コードと IP コアの生成] タスクで [レジスタ インターフェイスの読み取りパイプライン] 設定を使用して、読み取りアドレス デコーダーのパスに挿入するパイプライン ステージの数を指定します。詳細については、AXI4 レジスタ インターフェイスの生成のための設計のモデル化 (HDL Coder)を参照してください。 値: |

| GenerateDefaultAXI4Slave | このブロック プロパティをモデルに保存するには、IP コア生成ワークフローの [RTL コードと IP コアの生成] タスクで、既定の AXI4 下位インターフェイスの生成を無効にするかどうかを指定します。 値: |

| IPCoreAdditionalFiles | 設計内のブラック ボックスの Verilog® ファイル、SystemVerilog ファイル、または VHDL® ファイル。各ファイルの絶対パスを指定し、ファイル名はセミコロン (;) で区切ります。 このプロパティは HDL ワークフロー アドバイザーの [追加ソース ファイル] フィールドで設定できます。 値: 例: |

| IPCoreName | IP コア名。文字ベクトルとして指定します。 このプロパティは HDL ワークフロー アドバイザーの [IP コア名] フィールドで設定できます。このプロパティを既定値に設定すると、HDL ワークフロー アドバイザーは DUT の名前に基づいて IP コア名を作成します。 値: 例: |

| IPCoreVersion | IP コア バージョン数。文字ベクトルで指定します。 このプロパティは、HDL ワークフロー アドバイザーの [IP コア バージョン] フィールドで設定できます。このプロパティを既定値に設定すると、HDL ワークフロー アドバイザーで IP コア バージョンが設定されます。 値: 例: |

| IPDataCaptureBufferSize | FPGA Data Capture のバッファー サイズ。文字ベクトルとして指定します。FPGA Data Capture を使用して、FPGA での実行時の設計内の信号を観察します。 バッファー サイズは、128*2^n の値を使用します。ここで n は整数です。既定では、バッファー サイズは 128 (n=0) です。n の最大値は 13 であり、バッファー サイズの最大値が 1048576 (=128*2^13) であることを意味します。 値: 例: |

PLC コード生成

Simulink® PLC Coder™ を使用して構造化テキスト コードを生成します。

固定小数点の変換

Fixed-Point Designer™ を使用して固定小数点システムの設計とシミュレーションを行います。

バージョン履歴

R2006a より前に導入

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)