このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

AXI4 スレーブ インターフェイスの生成のための設計のモデル化

軽量データ転送を実行したり、制御レジスタにアクセスしたりするには、AXI4 スレーブ インターフェイスを使用します。AXI4 スレーブ インターフェイスには、AXI4 および AXI4-Lite インターフェイスが含まれています。HDL Coder™ ソフトウェアを使用すると、モデルに AXI4 または AXI4-Lite プロトコルを実装する必要はありません。HDL IP コアで AXI4 または AXI4-Lite インターフェイスが生成されます。

設計をモデル化するときに、AXI4 スレーブ インターフェイスにマッピングするデータ端子を指定します。次に、HDL Coder がデータ端子をメモリマップド レジスタにマッピングし、端子のアドレス オフセットを割り当てます。

考慮事項

DUT 端子の AXI4 または AXI4-Lite インターフェイスへのマッピングに関して、以下を考慮してください。

設計内のすべてのスカラー端子、ベクトル端子、またはバス端子を AXI4 または AXI4-Lite インターフェイスのいずれかにマッピングできます。

同じ設計で一部の DUT 端子を AXI4 インターフェイスにマッピングし、その他の DUT 端子を AXI4-Lite インターフェイスにマッピングすることはできません。

AXI4 スレーブ インターフェイスへのスカラー端子のマッピング

DUT インターフェイス端子でスカラー データ型を使用する場合、インターフェイス端子を AXI4 または AXI4-Lite インターフェイスに直接マッピングできます。コード ジェネレーターは AXI4 インターフェイスにマッピングする各データ端子に一意のアドレスを割り当てます。

スカラー端子を AXI4-Lite インターフェイスにマッピングする方法を示す例の場合、モデル hdlcoder_led_blinking を開きます。

openExample('hdlcoder/IPCoreGenWorkflowWithAMicroBlazeProcessorKC705Example',... 'supportingFile','hdlcoder_led_vector.slx')

このモデルでは、サブシステム led_counter はハードウェア サブシステムです。これは、FPGA ボード上の LED を点滅させるカウンターをモデル化します。2 つの入力端子 Blink_frequency および Blink_direction は LED の点滅頻度および方向を決定する制御端子です。サブシステム led_counter の外側にあるすべてのブロックはソフトウェア実装用です。

Simulink® では、Slider Gain ブロックまたは Manual Switch ブロックを使用してハードウェア サブシステムの入力値を調整できます。組み込みソフトウェアでは、AXI インターフェイスのアクセス可能なレジスタに書き込むことで、ARM® プロセッサが生成された IP コアを制御します。ハードウェア サブシステムの出力ポートは、LED ハードウェアに接続します。出力端子 Read_back を使用してデータを読み取りプロセッサに戻すことができます。

IP Core Generation ワークフローを実行するとき、[ターゲット インターフェイスを設定] タスクで、端子 Blink_frequency、Blink_direction および AXI4-Lite インターフェイスに対する Read_back マップが表示されます。

この例の詳細については、次を参照してください。

ベクトル端子の AXI4 スレーブ インターフェイスへのマッピング

DUT インターフェイス端子でベクトル データ型を使用する場合、インターフェイス端子を AXI4 または AXI4-Lite インターフェイスに直接マッピングできます。コード ジェネレーターは一意のアドレスを AXI4 インターフェイスにマッピングする各データ端子に割り当てます。

ベクトル端子をマッピングするとき、HDL Coder は各端子のストローブ レジスタを使用して、IP コア アルゴリズム ロジックとの同期を保持します。入力端子について、ストローブ レジスタは一連のシャドー レジスタのイネーブル信号を制御します。これにより、IP コア アルゴリズム ロジックは更新されたベクトル要素を同時に確認できます。出力端子について、ストローブ レジスタは読み取られるベクトル データが同期的に取得されていることを確認します。

ベクトル端子を AXI4-Lite インターフェイスにマッピングする方法を示す例の場合、モデル hdlcoder_led_vector を開きます。

open_system('hdlcoder_led_vector')

このモデルでは、サブシステム DUT が LED の点滅アルゴリズムを実装し、このサブシステムにはベクトルの出力端子があります。IP Core Generation ワークフローを実行するとき、[ターゲット インターフェイスを設定] タスクに、入力端子と出力端子の AXI4-Lite インターフェイスへのマップが表示されます。

詳細については、IP Core Generation Workflow with a MicroBlaze Processorを参照してください。

AXI4 スレーブ インターフェイスへの double データ型と 32 ビットを超えるデータのマッピング

DUT 端子が double データ型や幅が 32 ビットを超えるデータ型をもつ場合、HDL Coder では次のように処理します。

AXI4 または AXI4-Lite インターフェイスのレジスタ幅に合わせてデータを個々の 32 ビット ワードに分割します。

各 32 ビット ワードを個々のアドレスに割り当てます。結果の開始アドレスと終了アドレスは、IP コアの生成レポートの [Register Address Mapping] セクションで確認できます。

DUT の境界でデータを同期するために追加のストローブ レジスタを作成します。ストローブ ロジックの動作はベクトル端子のストローブ レジスタと同じです。ベクトル端子の処理方法の詳細については、ベクトル端子の AXI4 スレーブ インターフェイスへのマッピングを参照してください。

ビット幅が 32 ビットを超えるデータが HDL Coder でどのように分割されて個々のアドレスにマッピングされるかを説明します。このモデル例には、3 つの入力端子と 3 つの出力端子があります。

入力/出力端子 1:

uint64データ型をもつスカラー。入力/出力端子 2:

ufix45_En10データ型をもつスカラー。入力/出力端子 3: 64 ビットのデータ型をもつ 3 要素のベクトル。

次のイメージは、入力端子と出力端子に対応するデータ型をもつ DUT の例を示しています。各端子は AXI4 インターフェイスにマッピングされています。

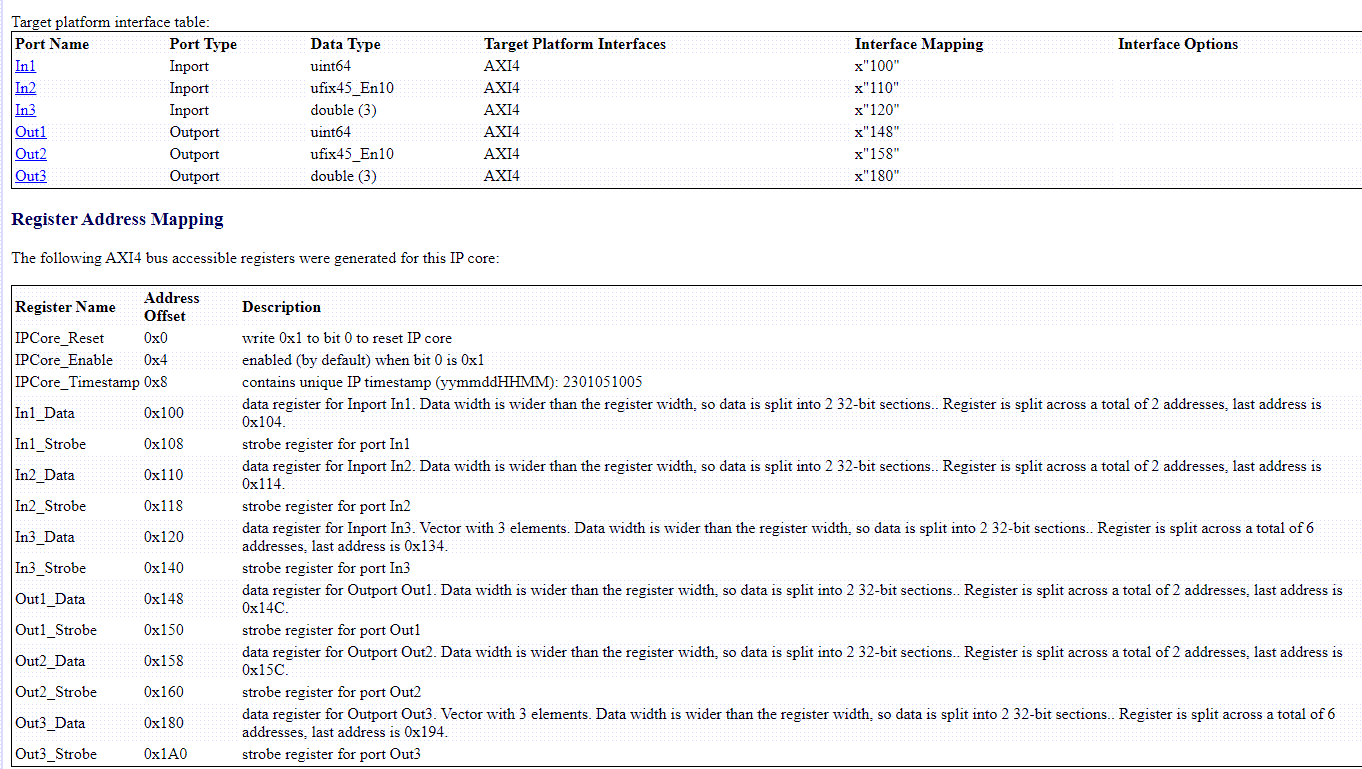

この DUT を処理する際、HDL Coder では、データを 32 ビット ワードに変換し、それぞれの 32 ビット ワードを特定のアドレスにマッピングします。次のイメージは、生成された IP コア レポートのターゲット インターフェイス構成と [Register Address Mapping] セクションを示したものです。[Register Address Mapping] セクションに、ビット幅が 32 ビットを超えるデータについて、開始アドレス、32 ビット ワードの数、および最終レジスタ アドレスが記載されています。

入力端子 1 では、64 ビットのデータが 2 つの 32 ビット ワードに分割されています。2 つのワードのマッピング先のアドレスは 0x100 と 0x104 です。ビット 0 ~ 31 が 0x100 にマッピングされ、ビット 32 ~ 63 が 0x104 にマッピングされています。出力端子 1 は、アドレス 0x148 と 0x14C に分割されています。

入力端子 2 では、45 ビットのデータが 2 つの 32 ビット ワードに分割されています。2 つのワードのマッピング先のアドレスは 0x110 と 0x114 です。ビット 0 ~ 31 が 0x110 にマッピングされ、ビット 32 ~ 63 が 0x114 にマッピングされています。出力端子 2 は、アドレス 0x158 と 0x15C に分割されています。

入力端子 3 では、各ベクトル要素が 2 つの 32 ビット ワードに分割されています。その結果、ベクトル全体では 32 ビット ワードが合計で 6 つになっています。6 つのワードのマッピング先のアドレスは 0x120、0x124、0x128、0x12C、0x130、および 0x134 です。

最初のベクトル要素のビット 0 ~ 31 が 0x120 にマッピングされています。

最初のベクトル要素のビット 32 ~ 63 が 0x124 にマッピングされています。

2 番目のベクトル要素のビット 0 ~ 31 が 0x128 にマッピングされています。

2 番目のベクトル要素のビット 32 ~ 63 が 0x12C にマッピングされています。

3 番目のベクトル要素のビット 0 ~ 31 が 0x130 にマッピングされています。

3 番目のベクトル要素のビット 32 ~ 63 が 0x134 にマッピングされています。

出力端子 3 は 6 つの 32 ビット ワードに分割されています。6 つのワードのマッピング先のアドレスは 0x180、0x184、0x188、0x18C、0x190、0x194 です。

AXI4 スレーブ インターフェイスへの複素数データ型のマッピング

DUT 端子が複素数データ型をもつ場合、HDL Coder では次のように処理します。

複素数データの実数部と虚数部を抽出し、それらを 2 つの別々の要素に変換します。

それらの要素を 2 つの連続するメモリ アクセスに割り当てます。送信する複素数データの実数部を低い方のアドレスに格納し、それに続くアドレスに虚数部を格納します。IP コアの生成レポートの [Register Address Mapping] セクションに開始アドレスと終了アドレスが指定されます。

DUT の境界でデータを同期するために追加のストローブ レジスタを作成します。ストローブ ロジックの動作はベクトル端子のストローブ レジスタと同じです。ベクトル端子の詳細については、ベクトル端子の AXI4 スレーブ インターフェイスへのマッピングを参照してください。

ビット幅が 32 ビットを超える複素数ベクトルのデータやデータ型については、単一のストローブを使用してすべてのデータ要素を同期します。

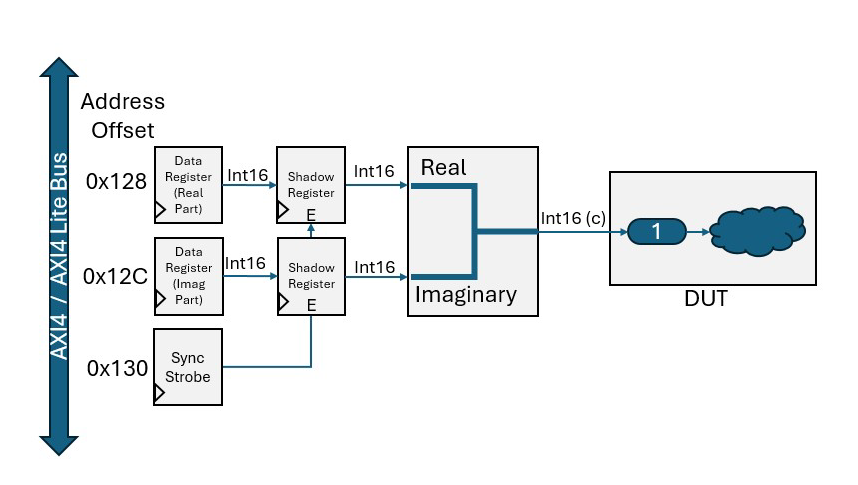

たとえば、ビット幅が 32 ビット未満の複素数スカラー データをもつ DUT 端子の場合、HDL Coder は各データ端子の実数部と虚数部を抽出し、それらを 2 要素ベクトルに変換します。その後、HDL Coder は各要素にアドレスを割り当てます。次のイメージは、int16 データ型をもつ複素数スカラーに対するこのプロセスを示しています。HDL Coder は、16 ビットの複素信号を 2 つの 32 ビット ワードに分割し、その 2 つのワードをアドレス 0x128 および 0x12C にマッピングします。この場合、実数部のビット 0 ~ 15 が 0x128 にマッピングされ、虚数部のビット 0 ~ 15 が 0x12C にマッピングされます。ストローブ レジスタで一連のシャドウ レジスタのイネーブル信号が制御されます。これにより、更新された実数部と虚数部の信号を IP コア アルゴリズム ロジックで同時に確認できます。出力端子について、複素数データが同期的に取得されていることがストローブ レジスタで確認され、実数部と虚数部が同期されます。

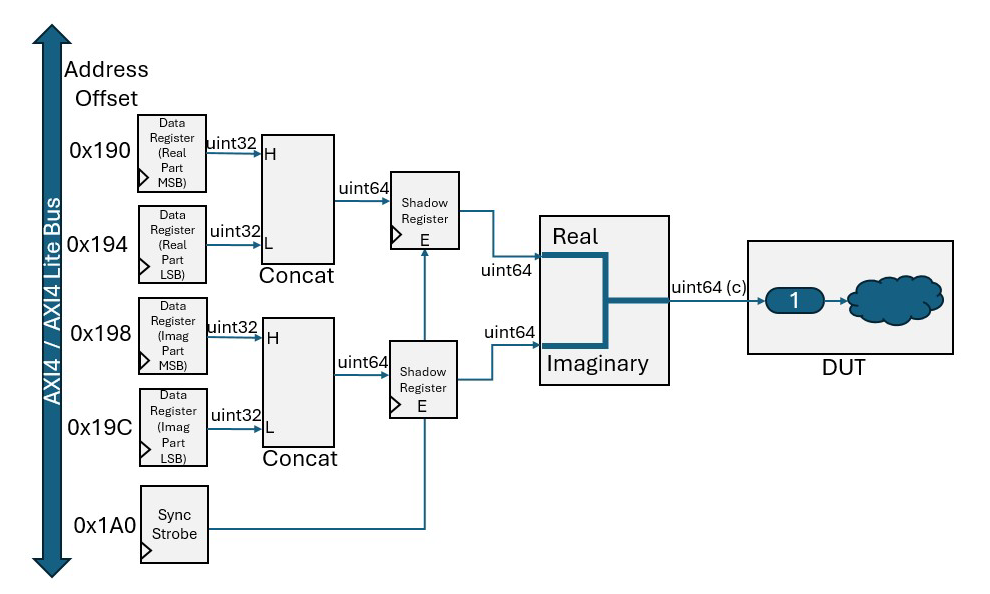

ビット幅が 32 ビットを超える複素数スカラー データをもつ DUT 端子の場合、HDL Coder は実数部と虚数部の要素を AXI4 または AXI4-Lite インターフェイスのレジスタ幅に合わせて 32 ビット ワードに分割します。次のイメージは、uint64 データ型をもつ複素数スカラーを示しています。HDL Coder は、64 ビットの複素信号を 4 つの 32 ビット ワードに分割し、その 4 つのワードをアドレス 0x190、0x194、0x198、および 0x19C にマッピングします。この場合、実数部のビット 0 ~ 31 が 0x190 にマッピングされ、実数部のビット 32 ~ 63 が 0x194 にマッピングされます。虚数部のビット 0 ~ 31 は 0x198 にマッピングされ、虚数部のビット 32 ~ 63 は 0x19C にマッピングされます。単一のストローブですべてのデータ要素が同期されます。

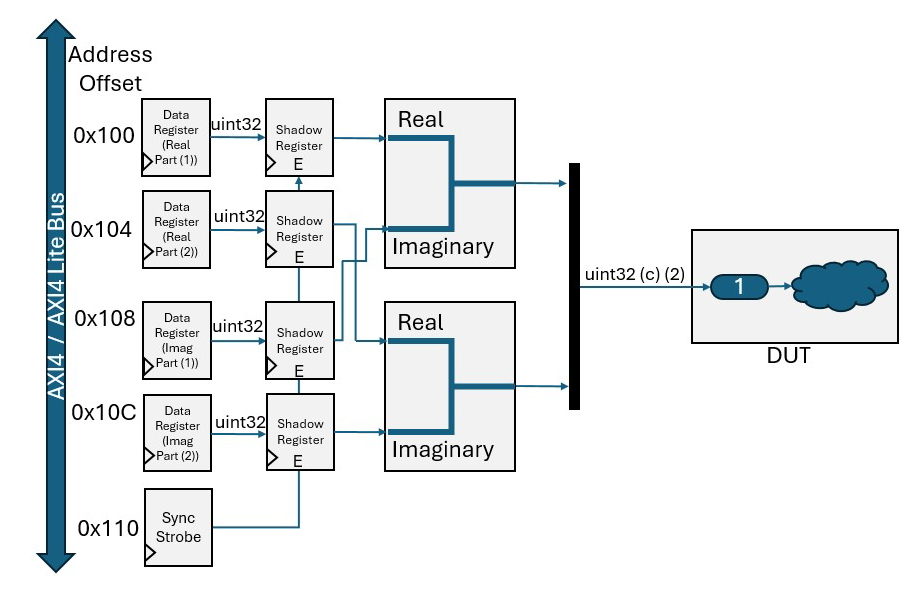

複素数ベクトルをもつ DUT 端子の場合、HDL Coder は各ベクトル要素を実数部と虚数部の要素に分割してから、それらの各要素をさらに AXI4 または AXI4-Lite インターフェイスのレジスタ幅に合わせて 32 ビット ワードに分割します。次のイメージは、それぞれが uint32 データ型をもつ 2 要素の複素数ベクトルを示しています。この場合、最初のベクトル要素の実数部のビット 0 ~ 31 が 0x100 にマッピングされ、2 番目のベクトル要素の実数部のビット 0 ~ 31 が 0x104 にマッピングされます。最初のベクトル要素の虚数部のビット 0 ~ 31 は 0x108 にマッピングされ、2 番目のベクトル要素の虚数部のビット 0 ~ 31 は 0x10C にマッピングされます。ストローブ レジスタで実数部と虚数部が同期されます。

出力端子について、読み取るデータの同期的な取得がストローブ レジスタで制御されます。

AXI4 スレーブ インターフェイスへのバス データ型のマッピング

DUT インターフェイス端子でバス データ型を使用する場合、インターフェイス端子を AXI4 または AXI4-Lite インターフェイスに直接マッピングできます。

バス データ型の端子を AXI スレーブ インターフェイスにマッピングすると、HDL Coder は各バス要素に一意のアドレスを割り当てます。HDL Coder は、バス端子を独立したスカラーおよびベクトル端子のグループとして扱います。HDL Coder がバス要素にアドレスを割り当てると、別個のレジスタとして扱われ、アドレスは連続しません。ターゲット インターフェイス テーブルのバス端子のアドレスを変更すると、最初の要素のアドレスのみが変更されます。

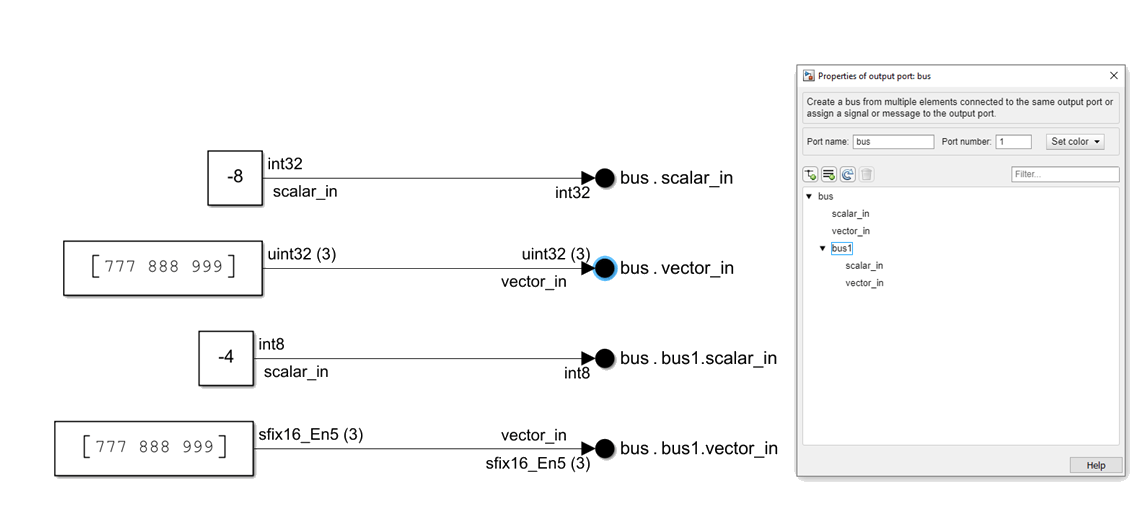

バス要素のモデル化

バス要素をモデル化するには、Bus Creator ブロックを使用するか、Bus Element ブロックを使用してバス端子を作成します。

Bus Creator ブロックを使用してバス要素をモデル化します。

Bus Element ブロックを使用してバス要素をモデル化します。

詳細については、Map Bus Data Types to a Register Interfaceを参照してください。

AXI4 スレーブ レジスタの初期値の指定

IP Core Generation ワークフローまたは Simulink Real-Time FPGA I/O ワークフローを実行するときに、AXI4 スレーブ レジスタにマッピングされる入力端子の初期値を指定できます。次のターゲット インターフェイスにマッピングするときの初期値を指定できます。

AXI4

AXI4-Lite

PCIe

調整可能なパラメーター端子を AXI4 スレーブ レジスタにマッピングするときは、初期値は指定できません。既定では、初期値はゼロです。非ゼロの値を指定するには、次を実行します。

ターゲット プラットフォーム インターフェイス テーブルで入力 DUT 端子を AXI4 スレーブ インターフェイスにマッピングするときに、[Options] ボタンが [Interface Options] 列に表示されます。

[Options] ボタンをクリックしてから、[RegisterInitialValue] を指定します。

指定された値は、DUT Inport ブロックで [ターゲット仕様] タブの HDL ブロック プロパティ [IOInterfaceOptions] として保存されます。たとえば、DUT 入力端子を AXI4-Lite インターフェイスにマッピングし、[RegisterInitialValue] を 5 に設定してから、[ターゲット インターフェイスを設定] タスクを実行します。その入力端子の [IOInterfaceOptions] プロパティには値 {'RegisterInitialValue','5'} が保存されます。

IOInterfaceOptions の値を表示するには、DUT 端子への絶対パスが hdlcoder_led_blinking/led_counter/LED である場合、次を入力します。

hdlget_param('hdlcoder_led_blinking/led_counter/LED',... 'IOInterfaceOptions')

スカラー端子の初期値を指定します。

hdlset_param('hdlcoder_led_blinking/led_counter/LED', ... 'IOInterfaceOptions', {'RegisterInitialValue','5'});

バスの初期値を設定するには、フィールド名がバス要素名に一致する struct を指定します。以下に例を示します。

MATLAB® ワークスペースで定義されている変数を使用して初期値を指定することもできます。以下に例を示します。

bus1_initialvalue = struct('scalar_in1',1,'scalar_in2',2,'scalar_in3',3,'scalar_in4',4,'vector_in',[1 3])

AXI4 スレーブ インターフェイスの値の読み戻し

IP Core Generation ワークフローの実行時に、AXI4 スレーブ インターフェイスを使用して、AXI4 スレーブ レジスタに書き込まれる値を読み戻すことができます。たとえば、ARM プロセッサの Linux® コンソールで devmem コマンドを使用して、AXI4 スレーブ レジスタに書き込まれる値を読み戻すことができます。HDL Verifier™ がインストールされている場合、AXI Manager IP を使用して値を読み戻すことができます。

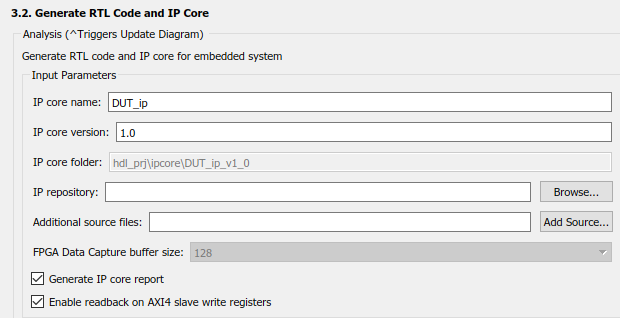

この機能を使用するには、IP Core Generation ワークフローの [RTL コードと IP コアの生成] タスクで、[AXI4 スレーブ書き込みレジスタで再読み取りを有効にする] チェック ボックスをオンにして、[RTL コードと IP コアの生成] タスクを実行します。

このタスクを実行すると、HDL Coder はモデルで有効にした読み戻し設定を保存します。DUT サブシステムの HDL ブロック プロパティの [ターゲット仕様] タブの [IP コア パラメーター] セクションに、パラメーター [AXI4RegisterReadback] が on に設定されていることがわかります。HDL ワークフロー アドバイザー実行をスクリプトにエクスポートする場合、hdlset_param を使用するとモデルに保存されたこの設定が表示されます。

hdlset_param('hdlcoder_led_vector/DUT', 'AXI4RegisterReadback', 'on');

これらの例では、PuTTy™ などのプログラムを使用する Linux コンソールで devmem コマンドを使用することで、読み戻しの値を使用する方法を示します。

スカラー端子を AXI4 インターフェイスにマッピングする際に値を読み戻すには、最初に値を AXI4 レジスタに書き込んでから値を読み戻します。IP コアの生成レポートで AXI4 レジスタのメモリ アドレスを確認できます。

ベクトル端子を AXI4 インターフェイスにマッピングする際に値を読み戻すには、最初に AXI4 レジスタに書き込み、ストローブ レジスタ アドレスに 0x1 を書き込んでから値を読み戻します。IP コアの生成レポートで AXI4 レジスタおよびストローブ レジスタのメモリ アドレスを確認できます。

レジスタ インターフェイスでのタイミングの最適化

R2024b 以降

モデルに複数の出力レジスタが含まれていて、複数の AXI4 スレーブ レジスタからデータを読み戻す場合、読み戻しロジックが合成周波数に影響することがあります。ビットストリームの作成後に、タイミング クロージャを満たさずにクリティカル パスが読み取りアドレス デコーダーにある場合や、合成の実行前にデコーダーのアーキテクチャを単一のマルチプレクサーから複数のマルチプレクサーに変換する場合は、[レジスタ インターフェイスの読み取りパイプライン] パラメーターを調整することでタイミングを最適化できます。

[レジスタ インターフェイスの読み取りパイプライン] を非ゼロの値に設定すると、指定したパイプライン レジスタをもつ均衡化されたマルチプレクサー ツリーが HDL Coder で生成され、デコーダーのアーキテクチャが単一のマルチプレクサーから複数のマルチプレクサーに変換されます。既定値はゼロであり、単一のマルチプレクサーになります。パラメーターを非ゼロの値に設定すると、最大読み取りレジスタ アドレスに基づいて HDL Coder でマルチプレクサー ツリーのレベル数が決定され、アドレス空間が均等に分割されます。結果として得られるレベル数が指定したパイプラインの値に満たない場合は、[レジスタ インターフェイスの読み取りパイプライン] パラメーターで指定されたパイプライン レジスタの数と一致するように、最適化によって追加のパイプライン レジスタがマルチプレクサー ツリーの最後に配置されます。[レジスタ インターフェイスの読み取りパイプライン] パラメーターは以下で設定できます。

HDL Coder ワークフロー アドバイザーのタスク [3.2. RTL コードと IP コアの生成]。

IP コア エディターの [Interface Settings] タブ。

MATLAB コマンド ライン (

hdlset_paramを使用してRegisterInterfaceReadPipelineパラメーターを設定)。DUT の [HDL ブロック プロパティ]

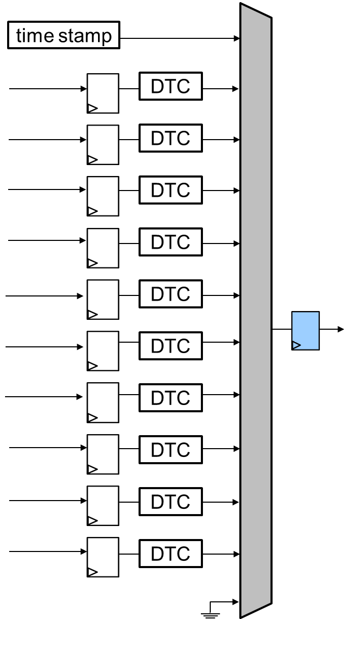

たとえば、次のイメージは、10 個の読み取り端子がある DUT で [レジスタ インターフェイスの読み取りパイプライン] をゼロに設定した場合に、パイプラインがゼロの単一レベルのマルチプレクサーが HDL Coder でどのように生成されるかを示しています。

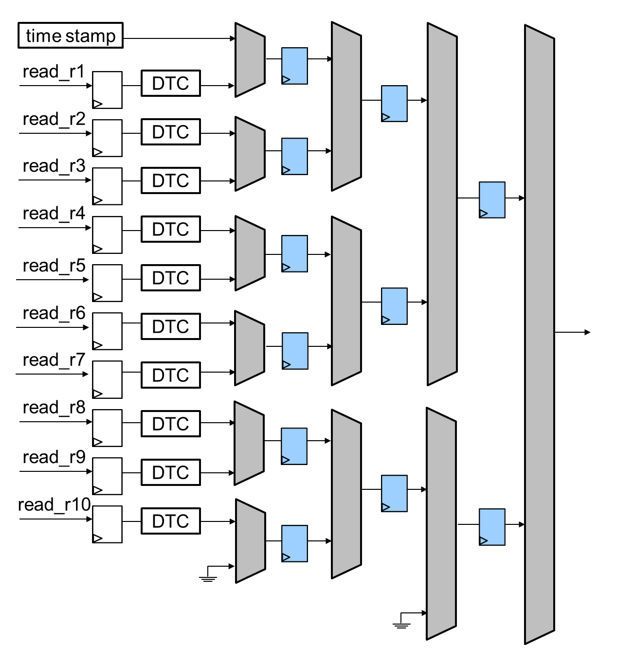

[レジスタ インターフェイスの読み取りパイプライン] を 3 に設定すると、HDL Coder で 4 レベルのマルチプレクサー ツリーが作成され、マルチプレクサーの各レベルの間にパイプラインが挿入されます。

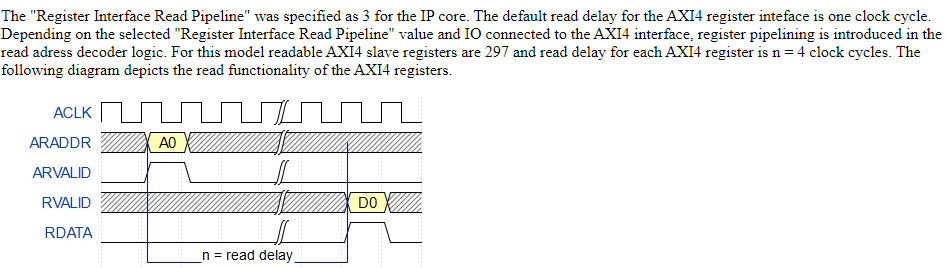

AXI4 レジスタ インターフェイスの既定の読み取り遅延は 1 クロック サイクルです。[レジスタ インターフェイスの読み取りパイプライン] に別の値を指定すると、各 AXI4 レジスタ インターフェイスの読み取り遅延が n クロック サイクルになります。ここで、"n" はレジスタ インターフェイスの読み取りパイプライン数に 1 を加えた数になります。IP コア レポートにタイミング図と情報が表示されます。

R2024b よりも前に作成されたモデルの IP コアを生成する場合は、[AXI4 スレーブの端子とパイプライン レジスタの比率] の値が非ゼロであれば、HDL Coder により [レジスタ インターフェイスの読み取りパイプライン] は 0 に設定されます。

制限

AXI4 スレーブ インターフェイスでは、読み取りと書き込みの同時トランザクションはサポートされません。

同じ設計内で一部の DUT 端子を AXI4-Lite インターフェイスにマッピングし、それ以外を AXI4 インターフェイスにマッピングすることはできません。

AXI4 スレーブ インターフェイスでトランザクションを受け入れるには、AXI4 プロトコルの書き込みストローブ信号が完全にアサートされた状態 (すべて High) でなければなりません。書き込みストローブが完全にアサートされていない状態で、生成された IP コアの AXI4 スレーブ インターフェイスに対する書き込みトランザクションが AXI4 Master で開始されると、AXI4 スレーブ インターフェイスでトランザクションが破棄されます。