Intel FPGA および SoC デバイス

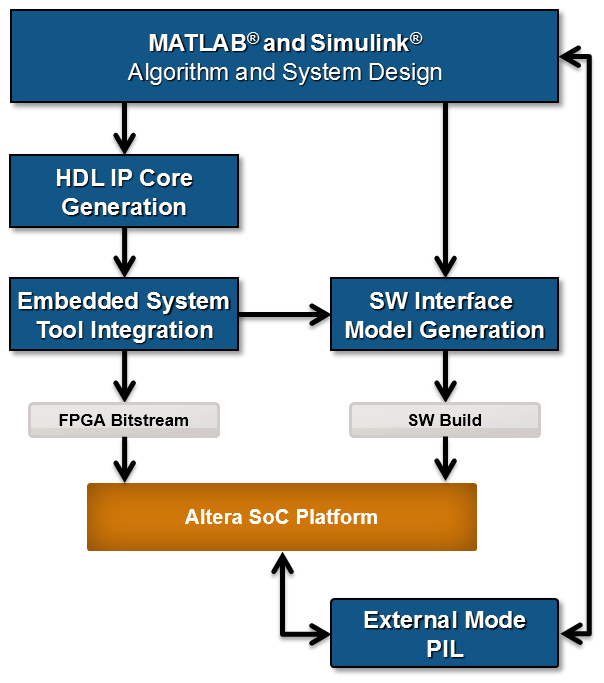

HDL Coder™ で IP コアを生成して Qsys プロジェクトに組み込み、Intel ハードウェアをプログラムできます。Embedded Coder® を使用すると、組み込みソフトウェアを生成してビルドし、ARM® プロセッサで実行できます。SoC プラットフォーム向けのハードウェア ソフトウェア協調設計ワークフローを参照してください。

設計を Intel FPGA および SoC デバイスに展開するには、HDL Coder Support Package for Intel FPGA and SoC Devices をインストールしなければなりません。インストールについては、HDL Coder でサポートされているハードウェアを参照してください。

HDL Coder Support Package for Intel FPGA and SoC Devices では、Intel Qsys を使用して FPGA 設計に統合できる IP コアの生成がサポートされています。Embedded Coder Support Package for Intel SoC Devices と組み合わせて使用することで、このソリューションでは C および HDL コード生成を使用して Intel SoC をプログラムできます。ハードウェア ソフトウェア協調設計ワークフローはシミュレーション、プロトタイピング、検証、および実装にまたがります。

| デバイス ファミリ | ボード | 使用可能なリファレンス設計 |

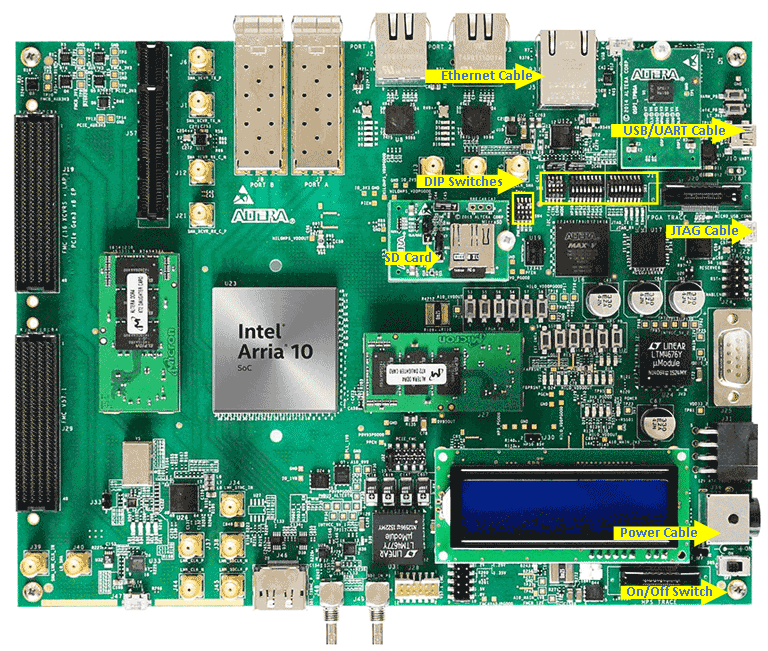

Arria® 10 SoC | Intel Arria 10 SoC 開発キット | |

Cyclone® V | Cyclone V SoC 開発キット - Rev.C | |

Cyclone V SoC 開発キット - Rev.D | ||

Arrow SoCKit 開発ボード | ||

Arria 10 | Arria 10 GX FPGA 開発キット | PCIe AXI Manager with External DDR4 Memory Access (Requires HDL Verifier) JTAG AXI Manager with External DDR4 Memory Access (Requires HDL Verifier) |

Intel MAX® 10 | Arrow® DECA MAX 10 FPGA 評価キット | AXI Manager - Ethernet (Requires HDL Verifier) (HDL Verifier) |

メモ

新しいハードウェアにサポートを拡張するには、カスタム ハードウェアへの IP コアの展開を参照してください。

カテゴリ

- セットアップと構成

サードパーティの EDA ツールおよびサポートされるハードウェアで使用するサポート パッケージをダウンロードしてインストールする

- ハードウェア ソフトウェア協調設計入門

生成された HDL コードをターゲット ハードウェア プラットフォームに展開する

- IP コアおよびビットストリームの生成

スタンドアロンの Intel FPGA ボードおよび SoC デバイスに展開する HDL コードを含む HDL IP コアおよびビットストリームを生成する