このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

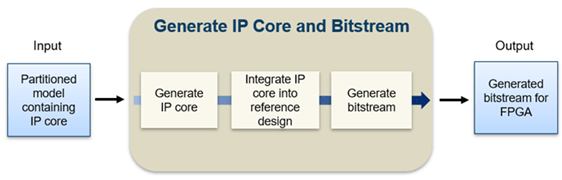

IP コアおよびビットストリームの生成

スタンドアロンの Intel® FPGA ボードおよび SoC デバイスに展開する HDL コードを含む HDL IP コアおよびビットストリームを生成する

IP コアは、特定の関数 (通常はアルゴリズム) を実装する共有可能で再利用可能な HDL コンポーネントです。IP コアは、IP コア定義ファイル、アルゴリズムについて生成された HDL コード、レジスタ アドレス マップを含む C ヘッダー ファイル、および IP コア レポートで構成されます。

HDL ワークフロー アドバイザーで IP Core Generation ワークフローを使用することによって、HDL Coder™ は、IP コアを Vivado® プロジェクトに統合するための HDL ソース コードと C ヘッダー ファイルを含む IP コアを生成してから、ターゲット ハードウェアをプログラムできます。ターゲット プラットフォームに応じて、IP コアを既定のリファレンス設計またはカスタム リファレンス設計に統合し、FPGA ハードウェアに展開するビットストリームを生成できます。入力は、Simulink® モデルまたは MATLAB® 関数の設計された IP コアです。出力は HDL Coder によって IP コアから生成されたビットストリームです。

カテゴリ

- カスタム IP コアの生成

既定のシステム リファレンス設計またはボードに登録されたカスタム リファレンス設計への展開用に DUT から HDL IP コアを生成する

- リファレンス設計の統合と展開

生成された IP コアを既定のシステム リファレンス設計に統合する

- カスタム ボードとリファレンス設計

Intel SoC デバイス用のカスタム リファレンス設計またはカスタム ボードを定義して登録する