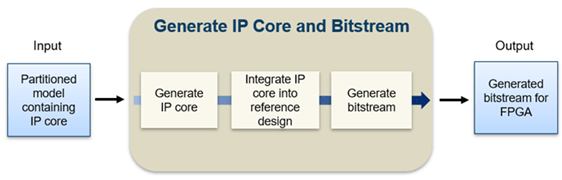

IP コアおよびビットストリームの生成

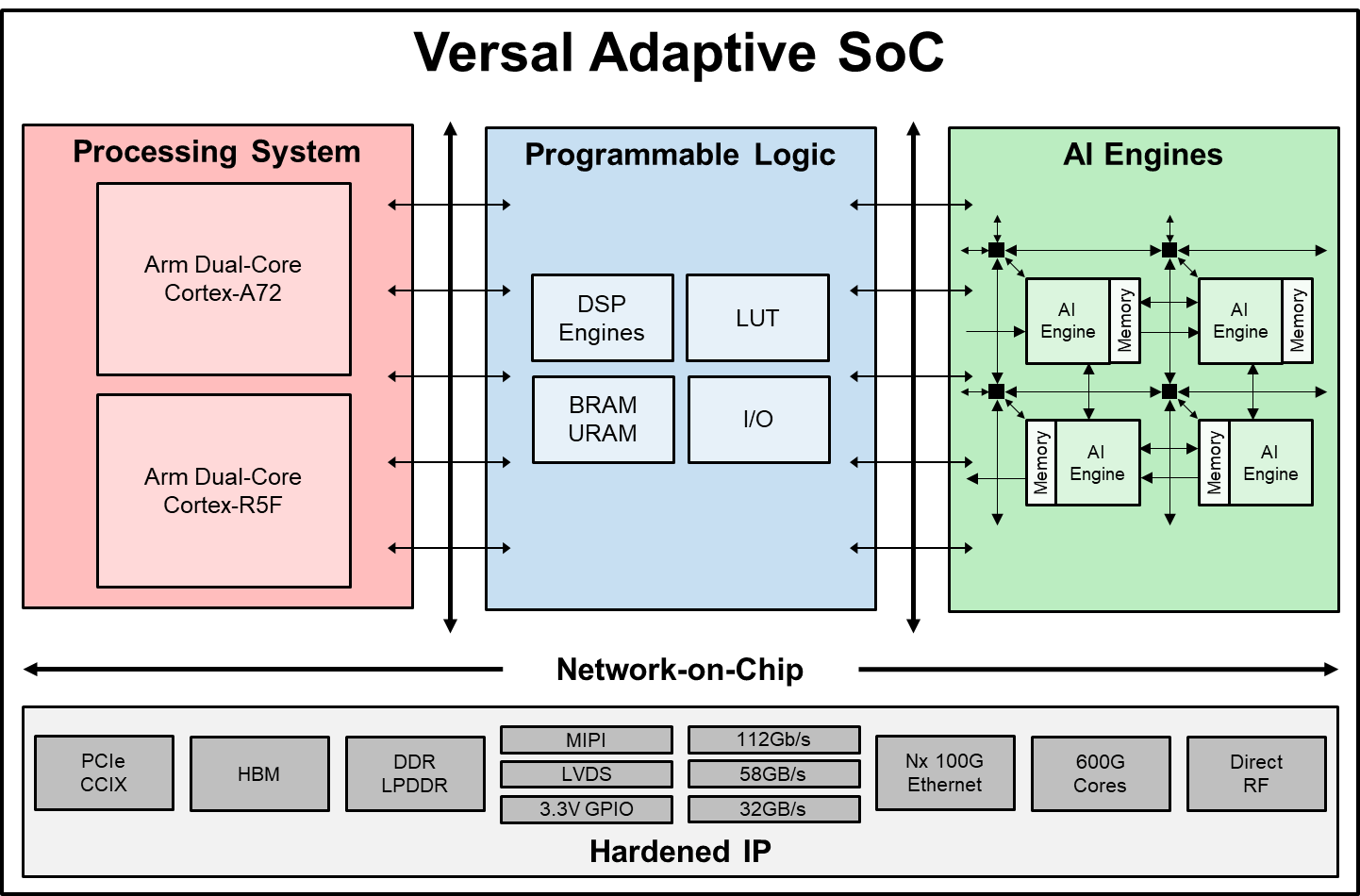

スタンドアロン FPGA ボード、Speedgoat® I/O モジュール、Xilinx® Zynq®-7000 プラットフォーム、Intel® SoC デバイスまたは Microchip SoC デバイスに展開する HDL コードを含む HDL IP コアおよびビットストリームを生成する

IP コアは、特定の関数 (通常はアルゴリズム) を実装する共有可能で再利用可能な HDL コンポーネントです。IP コアは、IP コア定義ファイル、アルゴリズムについて生成された HDL コード、レジスタ アドレス マップを含む C ヘッダー ファイル、および IP コア レポートで構成されます。

HDL ワークフロー アドバイザーで IP Core Generation ワークフローを使用することによって、HDL Coder™ は、IP コアを Vivado®、Qsys または Libero® プロジェクトに統合するための HDL ソース コードと C ヘッダー ファイルを含む IP コアを生成してから、ターゲット ハードウェアをプログラムできます。ターゲット プラットフォームに応じて、IP コアを既定のリファレンス設計またはカスタム リファレンス設計に統合し、FPGA ハードウェアに展開するビットストリームを生成できます。入力は、Simulink® モデルまたは MATLAB® 関数の設計された IP コアです。出力は HDL Coder によって IP コアから生成されたビットストリームです。

ワークフローの詳細については、FPGA および SoC ハードウェアをターゲットにする方法の概要を参照してください。

クラス

hdlcoder.WorkflowConfig | Configure HDL code generation and deployment workflows |

トピック

IP コアの生成

- カスタム IP コアの生成

HDL ワークフロー アドバイザーを使用し、モデルまたはアルゴリズムからカスタム IP コアを生成します。 - カスタム IP コア レポート

既定では、カスタム IP コアの生成時に HTML カスタム IP コア レポートが生成されます。 - ボードに依存しない HDL IP コアの Simulink モデルからの生成

HDL ワークフロー アドバイザーを開いて Simulink モデルのIP Core Generationワークフローを実行する際、汎用の Xilinx プラットフォーム、汎用の Intel プラットフォーム、汎用の Microchip プラットフォームなどの汎用プラットフォームを指定できます。 - MATLAB アルゴリズムからのボードに依存しない IP コアの生成

MATLAB からボードに依存しない IP コアを生成する - 複数の AXI4-Stream および AXI4 Master インターフェイスを使用した HDL IP コアの生成

DUT 端子を複数の AXI4-Stream、AXI4-Stream Video、および AXI4 Master インターフェイスにマッピングする方法を学習する。 - グローバル リセット信号の IP コア クロック領域への同期

HDL Coder がグローバル リセット信号を IP コア クロック領域に同期するためのロジックを自動的に挿入する方法を説明します。 - スタンドアロン FPGA デバイス向けの IP コアの生成ワークフロー

スタンドアロン FPGA デバイスを使用した IP コアの生成ワークフローの使用方法および IP コアのリファレンス設計への組み込み方法を学習します。 - Generate Board-Independent HDL IP Core for Xilinx Platforms

Integrate generated IP core into a Xilinx Vivado project. (R2024b 以降)

Xilinx Zynq リファレンス設計

- Default System Reference Design for AMD SoC Device

Learn about the default system reference design for AMD® SoC device and using the reference design. - Default System with AXI4-Stream Interface Reference Design

Learn about how to use the default system with AXI4-Stream Interface reference design and its requirements. - Default Video System Reference Design

Learn about the default video system reference design and its requirements. - Default System with External DDR Memory Access Reference Design

Learn about the default system with external DDR3, DDR4, LPDDR4 and shared memory access reference design and its requirements.

Intel SoC リファレンス設計

- Default System Reference Design for Intel SoC Devices

Learn about the default system reference design and using the reference design for Intel SoC Devices. - Default System with External DDR4 Memory Access Reference Design

Learn about the default system with external DDR3 memory access reference design and its requirements.

Microchip SoC リファレンス設計

- Default System Reference Design

Learn about the default system reference design and using the reference design.

リファレンス設計の統合

- リファレンス設計の合成を高速化するための IP キャッシュ

IP キャッシュを使用し、Out-Of-Context ワークフローを使用してリファレンス設計の合成時間を高速化します。 - IP コアの生成ワークフローと Simulink Real-Time FPGA I/O ワークフローでのタイミング エラーの解決

Vivado ベースのボードでの IP コアの生成ワークフローまたは Simulink Real-Time FPGA I/O ワークフローの [FPGA ビットストリームのビルド] ステップにおけるタイミング エラーを解決します。