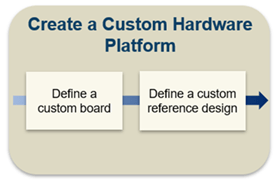

カスタム ハードウェア プラットフォームの作成

生成された IP コアを、カスタムのボードおよびリファレンス設計を定義することにより、ターゲット SoC デバイス、Speedgoat® I/O モジュール、またはスタンドアロン FPGA ボードに統合する

HDL Coder™ は、限られた数の既存のターゲット ハードウェアをサポートしています。ラピッド プロトタイピングには既存のボードで機能しますが、量産には通常、カスタム プラットフォームが必要となります。カスタム プラットフォームを作成し、Xilinx® Vivado® IP インテグレーターまたは Intel® Qsys を含むスタンドアロン FPGA ボードまたは SoC プラットフォームに IP コアを統合します。

MATLAB® で独自のカスタム リファレンス設計を作成し、HDL Coder を使用して IP コアをリファレンス設計に統合できます。

ワークフローの詳細については、FPGA および SoC ハードウェアをターゲットにする方法の概要を参照してください。

クラス

hdlcoder.Board | SoC カスタム ボードを記述するボード登録オブジェクト |

hdlcoder.ReferenceDesign | SoC リファレンス設計を記述するリファレンス設計登録オブジェクト |

関数

トピック

ボードとリファレンス設計

- ボードおよびリファレンス設計の登録システム

ボードおよびリファレンス設計の定義と登録のシステム。 - カスタム ボードの登録

カスタム SoC ボードのインターフェイスと属性の定義ボードを定義すると、HDL ワークフロー アドバイザーの IP コアの生成ワークフローを使用して、それをターゲットとすることができます。 - カスタム リファレンス設計の登録

カスタム SoC リファレンス設計のインターフェイスと属性を定義します。リファレンス設計を定義し登録すると、HDL ワークフロー アドバイザーの IP コアの生成ワークフローを使用して、それをターゲットとすることができます。 - カスタム リファレンス設計のためのカスタム パラメーターおよびコールバック関数の定義

カスタム リファレンス設計のカスタム パラメーターおよびカスタムのコールバック関数の定義方法を学習します。 - リファレンス設計のパラメーターに基づいたリファレンス設計の動的なカスタマイズ

CustomizeReferenceDesignFcnメソッドを使用して、リファレンス設計を動的にカスタマイズする方法を学習する。 - カスタム リファレンス設計に対する IP リポジトリの定義と追加

IP リポジトリを作成し、カスタム リファレンス設計に対するリポジトリに IP モジュールを追加する方法を確認します。 - DUT AXI4 スレーブ インターフェイスにアクセスするためのリファレンス設計での複数の AXI Master インターフェイスの定義

カスタム リファレンス設計で複数の AXI Master インターフェイスを指定して HDL DUT IP AXI4 スレーブ インターフェイスにアクセスする方法について説明します。 - 複数の AXI4-Stream および AXI4 Master インターフェイスを使用した HDL IP コアの生成

DUT 端子を複数の AXI4-Stream、AXI4-Stream Video、および AXI4 Master インターフェイスにマッピングする方法を学習する。 - Dynamically Create Reference Design with Master Only or Slave Only AXI4-Stream Interface

This example illustrates how to customize the reference design dynamically by using a callback function based on the reference design parameter options. Also, this example shows how you can customize the number of AXI4-Stream interface channels in your reference design to be Only AXI4-Stream Master interface, Only AXI4-Stream Slave interface or both the interfaces. - リファレンス設計の合成を高速化するための IP キャッシュ

IP キャッシュを使用し、Out-Of-Context ワークフローを使用してリファレンス設計の合成時間を高速化します。 - Generate Device Tree for IP Core

Generate device tree files that include the HDL Coder generated IP core. - Export Custom Reference Design from SoC Model (SoC Blockset)

Use thesocExportReferenceDesignfunction to export a custom reference design from an SoC Blockset™ model. - Export Custom Reference Design (SoC Blockset)

This example shows how to export a custom reference design from an SoC model by using the Soc Blockset™socExportReferenceDesignfunction. After creating the custom reference design, use the HDL Workflow Advisor tool from HDL Coder™ to integrate an IP core into the reference design.

特定のハードウェア プラットフォーム

- Zynq ワークフロー用のカスタムのボードとリファレンス設計の定義

この例では、Zynq® ワークフローでカスタムのボードとリファレンス設計を定義して登録する方法を示します。 - MathWorks Buildroot を使用したカスタム Zynq ボードに対する Xilinx Zynq Linux イメージの作成

この例では、MathWorks® Buildroot システムを使用して、Zynq® ワークフロー内で Linux® オペレーティング システムが搭載された Zynq® カスタム ボードを開始するための Zynq® Linux® イメージを作成する方法を説明します。 - Intel SoC ワークフロー用のカスタムのボードとリファレンス設計の定義

この例では、HDL Coder™ Intel® SoC ワークフローでカスタムのボードとリファレンス設計を定義して登録する方法を示します。 - Define Custom Board and Reference Design for Microchip Workflow

This example shows how to define and register a custom board and reference design for a blinking LED model in the Microchip workflow of the HDL Workflow Advisor. You use a SmartFusion2® board, but you can define and register a custom board or a custom reference design for other Microchip platforms. - Define Custom Board and Reference Design for Microchip Pure FPGA Platforms

This example shows how to define and register a Pure FPGA boards and reference design for a LED blinking model in the IP Core Generation workflow of the HDL Workflow Advisor. You use a Microchip PolarFire® board, but you can define and register a custom board or a custom reference design for other Microchip platforms. - Zynq ボードのオーディオ システム用のリファレンス設計のオーサリング

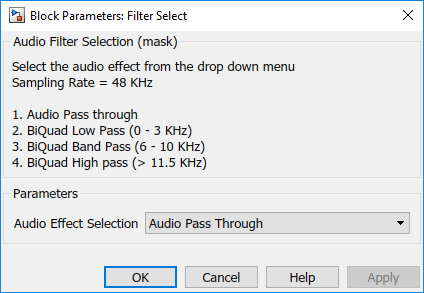

この例では、Zynq® ボードでオーディオ アルゴリズムを実行してオーディオ入出力にアクセスするリファレンス設計を作成する方法を示します。 - ZYBO ボードのオーディオ システム用のリファレンス設計のオーサリング

この例では、ZYBO™ Z7-10 ボードでオーディオ アルゴリズムを実行してオーディオ入出力にアクセスするリファレンス設計を作成する方法を示します。 - Intel ボードのオーディオ システム用のリファレンス設計のオーサリング

この例では、Intel® Arrrow® SoC ボードでオーディオ アルゴリズムを実行してオーディオ入出力にアクセスするリファレンス設計を作成する方法を示します。

関連情報

トラブルシューティング

IP コアの生成ワークフローと Simulink Real-Time FPGA I/O ワークフローでのタイミング エラーの解決

Vivado ベースのボードでの IP コアの生成ワークフローまたは Simulink Real-Time FPGA I/O ワークフローの [FPGA ビットストリームのビルド] ステップにおけるタイミング エラーを解決します。