複数の AXI4-Stream チャネルを使用した IP コアの生成

次の例は、オーディオ リファレンス設計を使用して、複数の AXI4-Stream チャネルを使用するオーディオ システムをモデル化し、ZedBoard™ に展開する方法を示しています。

はじめに

この例では、複数の AXI4-Stream チャネルと高度な AXI4-Stream 信号 Ready および TLAST を使用してスペクトログラムをもつプログラム可能なオーディオ フィルターをモデル化します。一方の AXI4-Stream チャネルがフィルターとオーディオ コーデック間でデータを転送します。もう一方の AXI4-Stream チャネルは Processing System と連動して、フィルター係数をプログラミングし、スペクトログラム データを解析するホスト コンピューターに転送します。

次に IP Core Generation ワークフローを実行して HDL IP コアを生成し、オーディオ リファレンス設計を使用してアルゴリズムを ZedBoard に展開できます。

システム アーキテクチャ

次の図は、システムの高度なアーキテクチャを示しています。

Audio Codec IPs では、オーディオ コーデックを構成し、ZedBoard とオーディオ コーデック間でオーディオ データを転送します。HDL Coder™ で生成された Audio Processing IP は、フィルター処理およびスペクトル解析を実行します。DMA IP は、Processing System と FPGA 間で AXI4-Stream データを転送します。MM2S DMA IP を通じて Processing System から送信されたストリーム データは、FPGA 上のフィルター係数をプログラムします。S2MM DMA IP を通じて Processing System で受信したストリーム データには、FPGA 上で計算されたスペクトログラム データが含まれます。Processing System は、AXI4-Lite インターフェイスを使用して、重み曲線をスペクトル解析用にも構成します。

前提条件

この例では、複数のストリーミング チャネルを使用するようにライブ入力例のオーディオ フィルターを拡張します。単一のストリーミング チャネルを使用する例については、Zynq ボードへのオーディオ フィルターの実装を参照してください。

この例を実行するには、次のソフトウェアとハードウェアをインストールして設定していなければなりません。

HDL Coder Support Package for AMD® FPGA and SoC Devices

Embedded Coder® Support Package for AMD® SoC Devices

Vivado® Design Suite の最新バージョン (HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアを参照)

ZedBoard

ZedBoard を設定するには、Simulink モデルからの IP コアの生成入門の例の「Set up Zynq hardware and tools」セクションを参照してください。以下に示すように ZedBoard で、モバイルまたは MP3 プレーヤーのオーディオ入力を LINE IN ジャックに接続し、イヤフォンまたはスピーカーをHPH OUT ジャックに接続します。

オーディオ処理アルゴリズムのモデル化

モデル hdlcoder_audio_filter_multistream を開きます。

open_system('hdlcoder_audio_filter_multistream') set_param('hdlcoder_audio_filter_multistream', 'SimulationCommand', 'Update')

モデルには、オーディオ処理対象の DUT サブシステム、オーディオをシミュレートするためのソースおよび Sink ブロック、Processing System と FPGA 間でストリーム データを転送する DMA 用プラント モデルが含まれています。

レートの考慮事項

FPGA で実行されているオーディオ アプリケーションの場合、FPGA クロック レートはオーディオのサンプルレートの数倍の速さになります。FPGA クロック レートとオーディオ データのサンプルレートの比率は、オーバーサンプリング係数です。この例では、オーバーサンプリング係数は、Repeat ブロックと Upsample ブロックを使用してモデル化されます。

FPGA クロック レートで設計をモデル化すると、アイドル クロック サイクルを利用し、各種コンポーネントを再利用することで、ターゲット ハードウェアのプラットフォームでリソースの使用率を最適化できます。この例に示しているオーディオ アプリケーションは、オーディオ サンプルレート 48kHz と FPGA クロック レート 96MHz を使用します。この例の オーバーサンプリング係数 は 2000 です。"オーバーサンプリング係数" の値をこのように大きくすると、Simulink® シミュレーションの速度が大幅に遅くなります。

シミュレーション時間を削減するには、オーバーサンプリング係数設定を使用せずに、設計に必要とされる最小のオーバーサンプリング係数で設計をモデル化できます。設計に対して最小限必要なオーバーサンプリング係数 は、オーディオ フィルターの長さ (1001) で判断できます。この値を使用すると、シミュレーション時間は半分に短縮され、シリアル フィルター ロジックのデータ サンプル間に十分なアイドル サイクルが提供されます。

オーディオ フィルター

DUT サブシステム内では、FIR フィルターが、オーディオ コーデック AXI4-Stream チャネルからデータを処理します。フィルター係数が MATLAB® で生成されて、Processing System と連動する 2 つ目の AXI4-Stream インターフェイスを使用してプログラミングされます。フィルターされたオーディオ出力はオーディオ コーデックにストリーミングして戻されます。

オーディオ フィルターは、FIR フィルターの完全なシリアル実装です。このフィルター構造は、大きなオーバーサンプリング係数を必要とするオーディオ アプリケーションに最適です。フィルターは各チャネルに積和 (MAC) 演算を使用します。また、このフィルターは RAM ブロックを使用して、データ遅延線と係数のソースも実装します。この実装では、高次フィルターのスライス ロジック使用率が高くならないようにして面積を節約します。

スペクトル アナライザー

オーディオ信号は、FIR フィルターを通過した後にスペクトル アナライザーに供給されます。スペクトル アナライザーは、フィルターされた信号の FFT を計算して、重み付け関数を適用し、結果を dBm に変換します。AXI4-Lite インターフェイスを No-weighting、A-weighting、C-weighting、または K-weighting として使用することで、実行する重み付けのタイプをプログラミングできます。実際の重み付け関数は、Audio Toolbox™ 関数 weightingFilter を使用して生成されたルックアップ テーブルを使用して実装されます。

AXI4-Stream インターフェイスのモデル化

モデルには 2 つの AXI4-Stream インターフェイスが含まれます。一方の AXI4-Stream インターフェイスがオーディオ コーデックと通信します。もう一方の AXI4-Stream インターフェイスは DMA を通じて Processing System と通信します。オーディオ コーデック インターフェイスには、Data 信号と Valid 信号のみ必要です。一方、DMA インターフェイスは、さらに AXI4-Stream プロトコルの Ready 信号と TLAST 信号を使用します。

AXI4-Stream モデリングで使用される信号の詳細については、AXI4-Stream インターフェイス生成向けのモデル設計を参照してくだい。

Ready 信号

AXI4-Stream インターフェイスでは、Ready 信号を使用してバック プレッシャーに適用または応答します。モデルは、FPGA から Processing System への AXI4-Stream マスター チャネルで Ready 信号を使用して、DMA からバック プレッシャーに応答します。下流の DMA は、さらに多くのスペクトログラム サンプルを受信できない場合、AXI4-Stream マスター チャネル上で入力 Ready 信号をデアサートします。スペクトログラム サンプルが破棄されないようにするために、Ready 信号がアサートして DMA がサンプルを再び受信できるようになったことを示すまで、モデルはデータを FIFO にバッファーします。

Processing System から FPGA までの AXI4-Stream スレーブ チャネルはバック プレッシャーを適用する必要がないため、その Ready 信号は常にアサートされます。オーディオ コーデックは、バック プレッシャーを処理せず、その Ready 信号をいずれのチャネルでも使用しません。AXI4-Stream モデリングでの Ready 信号の詳細については、Ready 信号 (オプション)を参照してください。

TLAST 信号

TLAST 信号はフレームの最後のサンプルを示すために使用されます。モデルは、AXI4-Stream スレーブ チャネルで、フィルター係数の完全なセットを受信したインジケーターとして TLAST 信号を使用します。AXI4-Stream マスター チャネルでは、TLAST 信号は、スペクトル アナライザー フレームの終わりを示すために使用されます。AXI4-Stream モデリングでの TLAST 信号の詳細については、TLAST 信号 (オプション)を参照してください。

ZedBoard のモデルのカスタマイズ

このモデルを ZedBoard に実装するには、最初に ZedBoard でオーディオ入力を受信し、処理されたオーディオを ZedBoard に送り返すリファレンス設計が Vivado に含まれていなければなりません。ZedBoard でオーディオ コーデックと連携するリファレンス設計を作成する方法の詳細については、ペリフェラル チップとのインターフェイスをとるためのカスタム リファレンス設計の作成を参照してください。この例では、Processing System と通信するための DMA IP を追加して、その例のリファレンス設計を拡張しています。

リファレンス設計では、左右のチャネルのオーディオ データが組み合わされて単一チャネルが形成されます。単一チャネルは、左チャネルが下位 24 ビットで、右チャネルが上位 24 ビットで形成されます。上記の Simulink モデルでは、CODEC_data_in が左右のチャネルに分割されます。フィルター処理は各チャネルで個別に実行されます。チャネルが連結されて、CODEC_data_out 用の単一チャネルが作成されます。

AXI4-Stream インターフェイスを使用した HDL IP コアの生成

次に、HDL ワークフロー アドバイザーを起動し、Zynq ハードウェア ソフトウェア協調設計ワークフローを使用して、この設計を Zynq ハードウェアに展開します。詳しい手順については、Xilinx Zynq プラットフォームの HW/SW 協調設計ワークフロー入門の例を参照してください。

1. MATLAB コマンド ウィンドウでhdlsetuptoolpathコマンドを使用して Vivado 合成ツール パスを設定します。コマンドを実行するときに独自の Vivado インストール パスを使用します。

hdlsetuptoolpath('ToolName', 'Xilinx Vivado', ... 'ToolPath', vivadopath);

2. 次のコマンドを使用して、IP リポジトリ フォルダーと ZedBoard 登録ファイルの両方を MATLAB パスに追加します。

example_root = (hdlcoder_amd_examples_root) cd (example_root) addpath(genpath('ipcore')); addpath(genpath('ZedBoard'));

3. DUT サブシステム hdlcoder_audio_filter_multistream/DUT から HDL ワークフロー アドバイザーを開くか、モデルの [Launch HDL Workflow Advisor] ボックスをダブルクリックします。

このモデル例では、ZedBoard のターゲット インターフェイスの設定は既に保存されているため、タスク 1.1 ~ 1.3 の設定は自動的に読み込まれます。モデルのターゲット インターフェイス設定の保存の詳細については、「Save Target Hardware Settings in Model」の例を参照してください。

4. [ターゲット デバイスおよび合成ツールを設定] を実行します。

このタスクでは、[ターゲット ワークフロー] に [IP Core Generation] が選択され、[ターゲット プラットフォーム] に [ZedBoard] が選択されています。

5. [ターゲットのリファレンス設計を設定] タスクを実行します。[リファレンス設計] として [Audio system with DMA Interface] が選択されます。

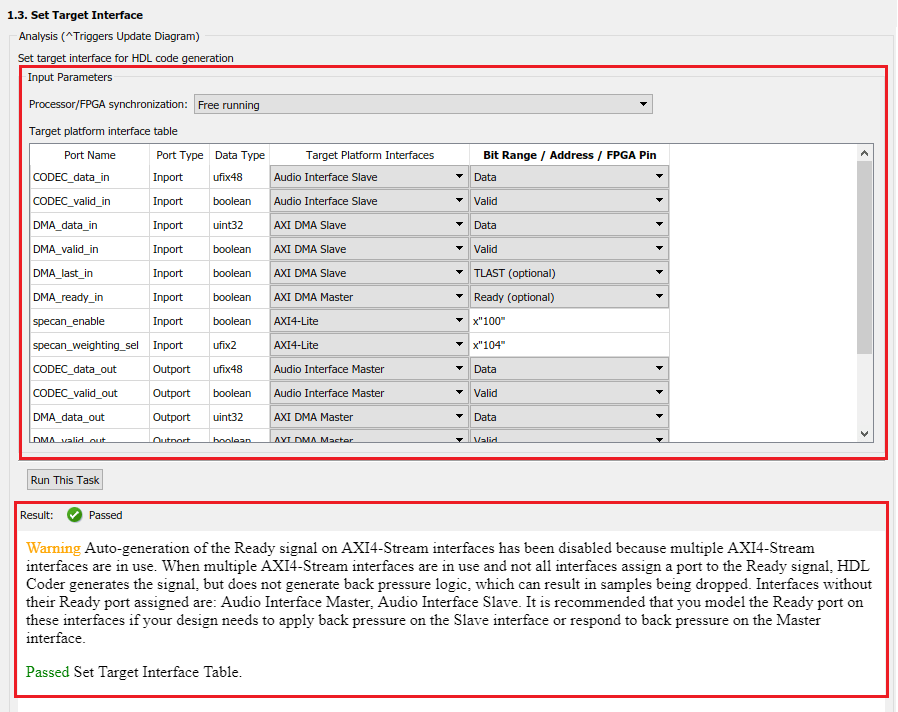

6. [ターゲット インターフェイスを設定] タスクを実行します。

このタスクでは、DUT サブシステムの端子が IP コア インターフェイスにマッピングされます。オーディオ コーデック端子は Audio インターフェイスにマッピングされ、DMA 端子は AXI DMA インターフェイスにマッピングされます。これらはどちらも AXI4-Stream インターフェイスです。AXI4-Stream インターフェイスはマスター/スレーブ モードで通信します。このモードでは、マスター デバイスがデータをスレーブ デバイスに送信します。したがって、データ端子が入力端子の場合は、AXI4-Stream Slave インターフェイスに割り当てられ、データ端子が出力端子の場合は、AXI4-Stream Master インターフェイスに割り当てられます。これに対する例外は Ready 信号です。AXI4-Stream Master Ready 信号はモデルに対する入力で、AXI4-Stream Slave Ready 信号はモデルの出力になります。スペクトル アナライザーの制御端子は AXI4-Lite にマッピングされます。

このタスクを実行すると、Ready 信号の自動生成が無効であること、および Audio インターフェイスは Ready 端子を割り当てないことの警告が示されます。バック プレッシャーは既に考慮されているため、この設計の警告を無視できます。つまり、設計で FIFO を使用することで DMA インターフェイスのバック プレッシャーに対処しています。オーディオ コーデック インターフェイスでは、バック プレッシャーは適用できないため、Ready 信号ロジックは必要ありません。

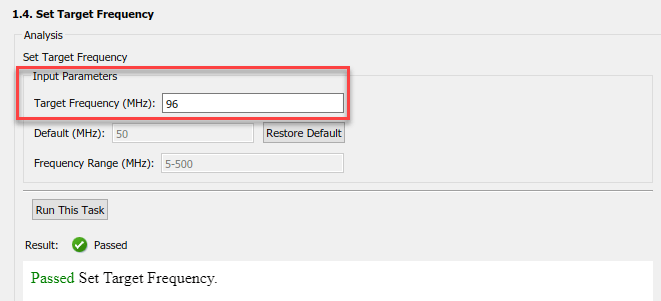

7. [ターゲット周波数を設定] タスクで、[ターゲット周波数 (MHz)] を 96 に設定します。このタスクを実行します。

このターゲット周波数値により、オーバーサンプリング係数は、48kHz のオーディオ サンプルレートに相対的な偶数の整数となります。

8. [RTL コードと IP コアの生成] タスクを右クリックして [選択したタスクまで実行] を選択します。

生成された IP コア レポート内の IP コアについては、レジスタ アドレス マッピングおよびその他のドキュメントを参照してください。

AXI4-Stream Audio に互換するリファレンス設計への IP の統合

次に、HDL ワークフロー アドバイザーで、[組み込みシステムの統合] タスクを実行して、生成された HDL IP コアを Zynq ハードウェアに展開します。

1. [プロジェクトを作成] タスクを実行します。

このタスクでは、生成された IP コアが Audio System with AXI DMA Interface リファレンス設計に挿入されます。最初の図に表示されているように、このリファレンス設計には、ZedBoard で送受信される内外のストリーミング オーディオ データを処理する IP と、Processing System で送受信されるストリーミング データ用の IP が含まれます。生成されたプロジェクトは、完全な ZedBoard 設計です。プロジェクトには、生成された DUT アルゴリズムの IP であるアルゴリズム部分と、リファレンス設計であるプラットフォーム部分が含まれます。

2. [結果] ペインのリンクをクリックして、生成された Vivado プロジェクトを開きます。Vivado ツールで、[Open Block Design] をクリックして Zynq 設計図を表示します。これには、生成された HDL IP コア、その他のオーディオ処理、および Zynq プロセッサが含まれます。

3. HDL ワークフロー アドバイザーで、残りのタスクを実行してソフトウェア インターフェイス モデルを生成し、FPGA ビットストリームを作成およびダウンロードします。[ターゲット デバイスをプログラム] タスクで Download プログラミング メソッドを選択して、FPGA ビットストリームを Zynq ボード上の SD カードにダウンロードします。これで、Zynq ボードの電源をオフ/オンすると、設計が自動的に再読み込みされます。

FPGA ファブリックでパラメーターを調整するための ARM 実行可能ファイルの生成

[ソフトウェア インターフェイス モデルを生成] タスクで、ソフトウェア インターフェイス モデルが生成されます。

生成されたモデルで、AXI4-Lite ドライバー ブロックが自動的に追加されます。ただし、AXI4-Stream ドライバー ブロックは自動的に生成できません。このドライバー ブロックは、ソフトウェア側にベクトル入力が必要ですが、DMA DUT 端子はスカラー端子です。正しいドライバー ブロックを使用したソフトウェア インターフェイス モデルの更新方法の詳細については、AXI-Stream インターフェイスを使用した IP コアの生成を参照してください。

この例では、更新されたソフトウェア インターフェイス モデルを使用します。このモデルを開くには、次を実行します。

open_system('hdlcoder_audio_filter_multistream_sw');

パラメーターを調整するには、次のようにします。

1. モデル ツールストリップの [ハードウェア] タブにある [監視と調整] ボタンをクリックします。Embedded Coder は、モデルを構築し、ARM® 実行可能ファイルを ZedBoard ハードウェアにダウンロードして実行し、モデルを実行中の実行可能ファイルに接続します。モデルの実行中に、さまざまなパラメーターを調整できます。

2. Filter Select ブロックの [フィルター タイプ] ブロック パラメーターを使用してフィルターのタイプを選択できます。Signal Processing Toolbox™ から関数 fir1 を使用して、このブロックでフィルター係数が計算されます。係数は、MM2S DMA IP を通じて通信する、AXI4-Stream IIO Write ブロックを通じて Processing System から FPGA へ送信されます。

3. スペクトル アナライザーで使用される重み曲線は、Weighting Curve Select ブロックの [曲線] ブロック パラメーターを使用して選択できます。選択内容は、AXI4-Lite インターフェイスを使用して Processing System から FPGA に送信されます。

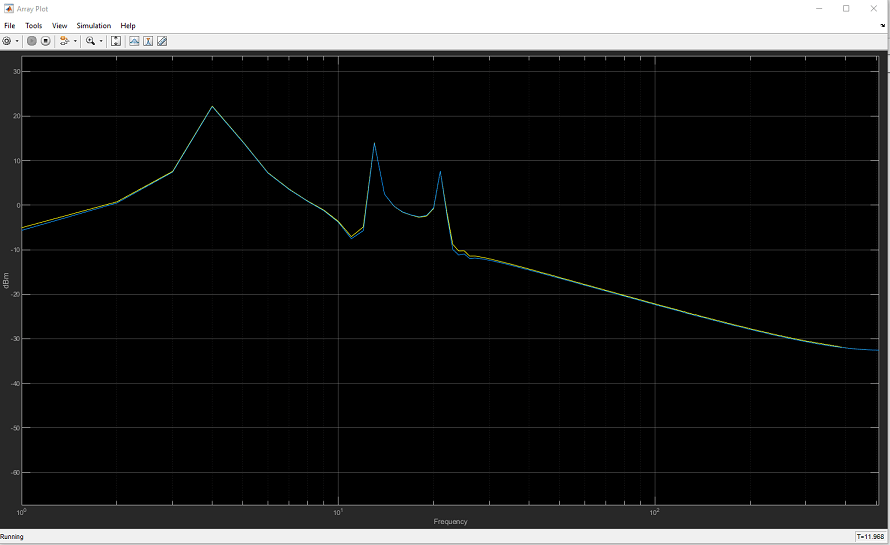

4. スペクトル アナライザー出力は、配列プロットに表示できます。別のフィルター タイプを選択するか、重み曲線を変更し、スペクトル データの変化を確認します。

フィルター処理されたオーディオ出力は、ZedBoard の HPH OUT ジャックにイヤフォンまたはスピーカーを接続して聴くことができます。