ペリフェラル チップとのインターフェイスをとるためのカスタム リファレンス設計の作成

この例では、Zynq® ボードでオーディオ アルゴリズムを実行してオーディオ入出力にアクセスするリファレンス設計を作成する方法を示します。

はじめに

この例では、オーディオ入力を ZedBoard から受け取り、何らかの処理を実行してから、処理されたオーディオ データを ZedBoard に送り返すリファレンス設計を作成します。HDL ワークフロー アドバイザーを使用してペリフェラル インターフェイスの IP コアも生成します。

ZedBoard でオーディオ処理を実行するには、次の 2 つのプロトコルが必要です。

ZedBoard の ADAU1761 オーディオ コーデック チップを設定するための I2C。

デジタル化されたオーディオ データをコーデック チップと Zynq ファブリックの間でストリーミングするための I2S。

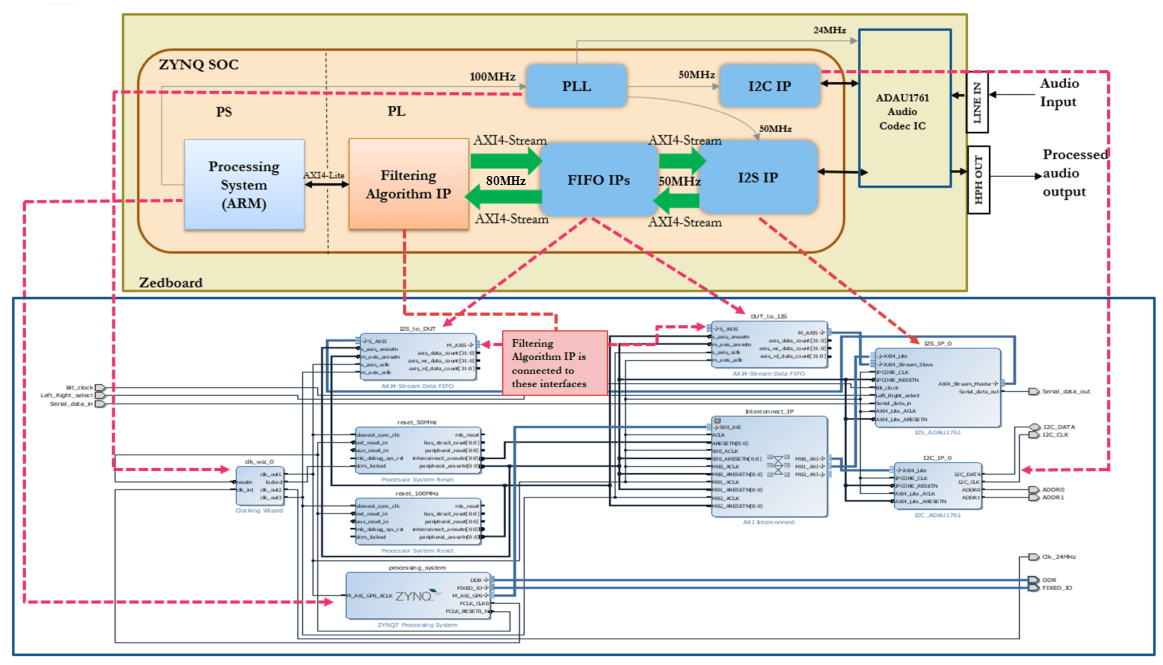

上記の図は、リファレンス設計が Filtering Algorithm IP でどのように使用されるかを示すアーキテクチャの概要図です。I2S IP は 50 MHz の周波数で動作しますが、それよりも高い周波数で Filtering Algorithm IP を実行する場合もあります。この周波数は、HDL ワークフロー アドバイザーの手順 1.4 で制御されます。この例では、フィルターは 80 MHz で動作するものと仮定します。I2S IP と Filtering Algorithm IP で動作周波数が異なるため、クロック ドメイン クロッシングに対処するために FIFO が必要になります。Filtering Algorithm IP は、選択されたフィルターのタイプに応じて、着信オーディオ データの周波数範囲をフィルター処理し、フィルター処理されたオーディオ データを出力として渡します。上記の図において、Filtering Algorithm IP は Simulink でモデル化するメインのアルゴリズムです。FIFO IP は Vivado で提供されますが、I2C IP と I2S IP は作成する必要があります。ここで、ユーザーには 3 つの選択肢があり、(a) 事前にパッケージ化された IP (ある場合) を使用するか、(b) Simulink でモデル化し、IP コア生成ワークフローを使用して IP コアを生成するか、(c) 古い形式の HDL コードを使用します。古い形式の HDL コードから IP を作成するには、Simulink モデルを使用して HDL コードをブラック ボックス化し、そのモデルから IP コアを生成します。FIFO IP は、50 MHz の着信オーディオ データと 80 MHz で実行されるフィルター IP の間のクロック ドメイン クロッシングに対処します。I2C、I2S、PLL、FIFO の各 IP と Processing System でリファレンス設計の一部が形成されます。

上記のリファレンス設計を作成するために使用される手順は次のとおりです。

ペリフェラル インターフェイスの IP コアを生成

Vivado でカスタム オーディオ コーデック リファレンス設計を作成

リファレンス設計定義ファイルを作成

リファレンス設計を検証

1. HDL ワークフロー アドバイザーを使用してペリフェラル インターフェイスの IP コアを生成

この例の場合は次のようになります。

I2C IP は、Stateflow ブロックを使用してモデル化し、トライステート バッファーの古い形式の VHDL コードも使用して開発されます。

I2S IP は、Simulink でモデル化して開発されます。

1.1 I2C IP の作成

オーディオ コーデック ADAU1761 を設定するための I2C IP の作成については、Stateflow を使用して作成された I2C コントローラー モデルからの IP コアの生成の記事を参照してください。

1.2 I2S IP の作成

Simulink で、I2S プロトコルを実装する MATLAB 関数を含むモデルを設計します。

modelname = 'hdlcoder_I2S_adau1761';

open_system(modelname);

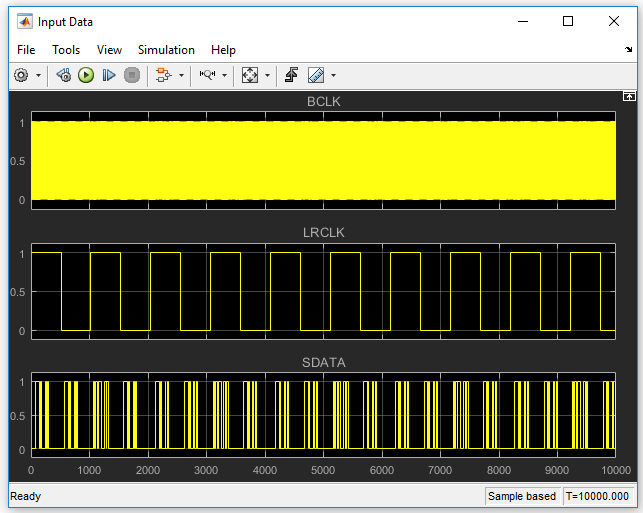

モデルでテスト ベンチを作成して、コーデックからの着信オーディオ データを再現します。

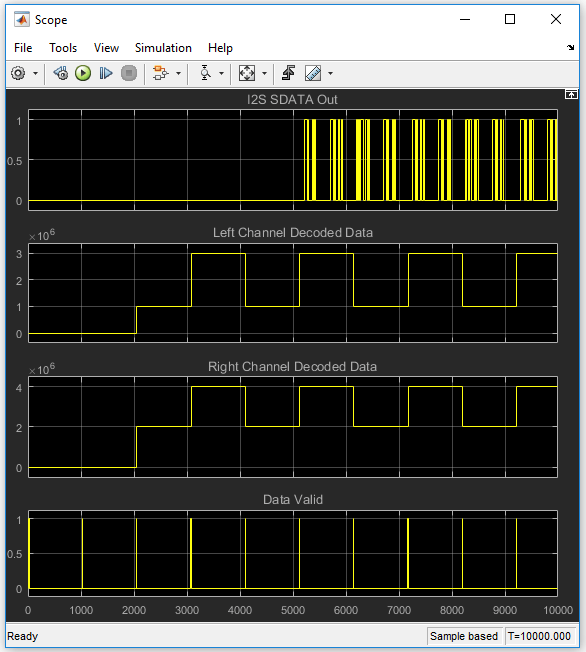

このデータを I2S の演算を実行する Subsystem ブロックにフィードします。スコープで Subsystem の出力を検証します。

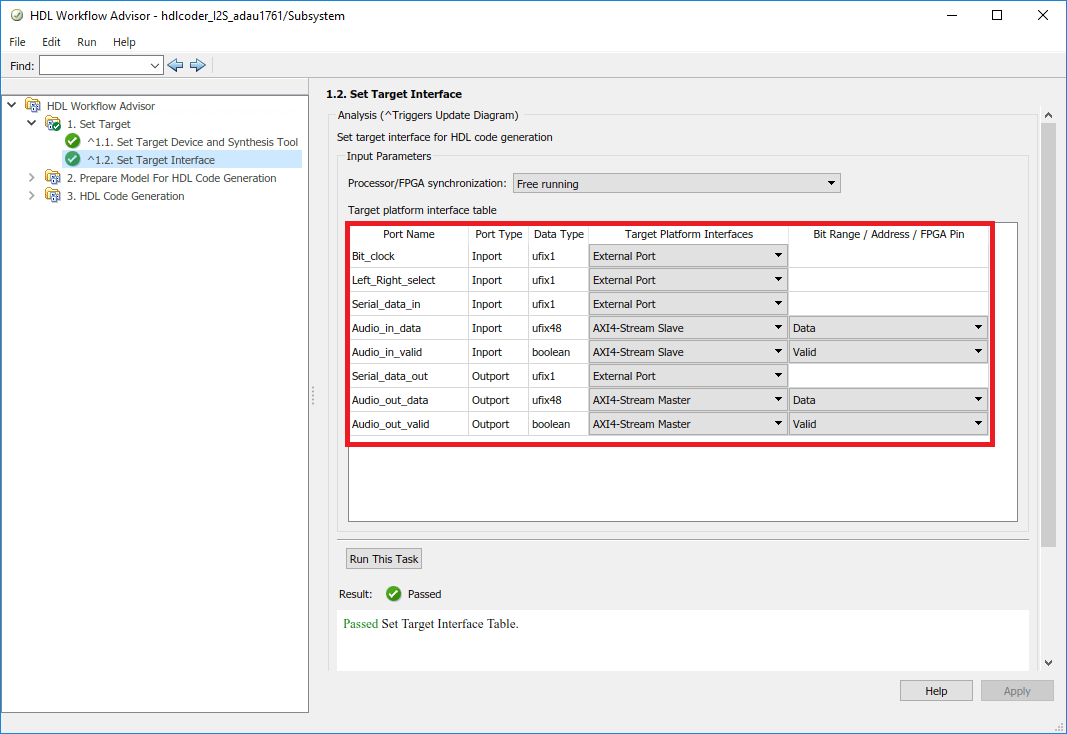

DUT サブシステムから HDL ワークフロー アドバイザーを起動します。タスク 1.1 では、前に生成された I2C IP と同じ設定にします。タスク 1.2 では、ターゲット プラットフォーム インターフェイスを次のように設定します。

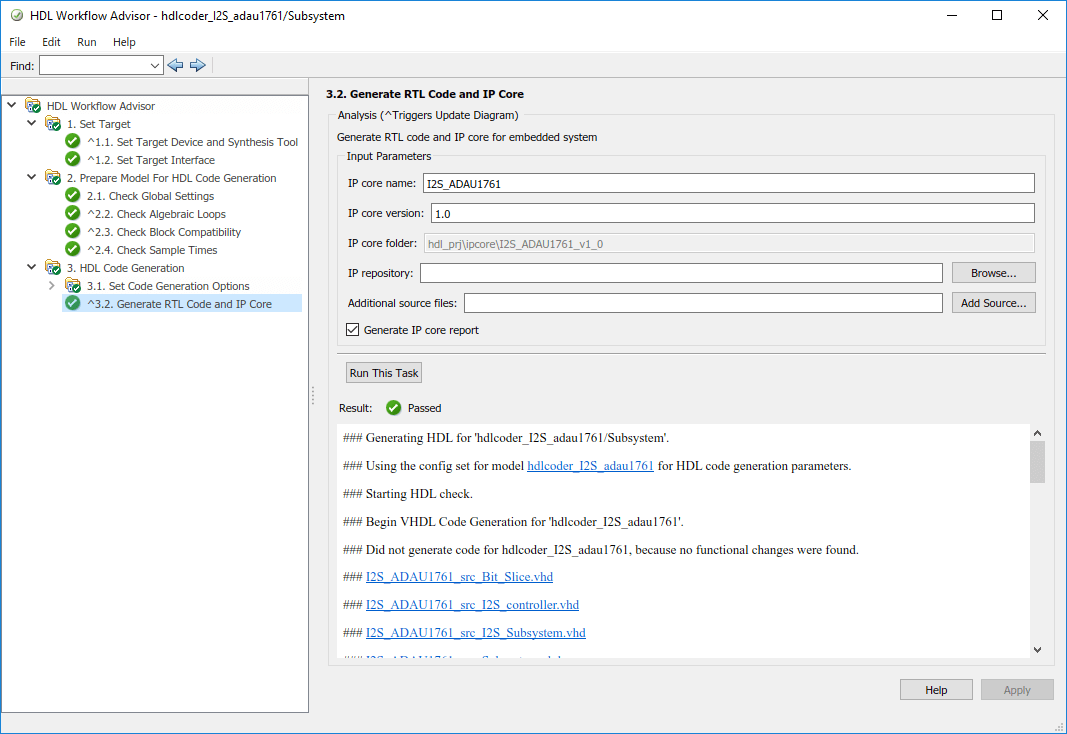

タスク 3.2 を実行し、IP コアを生成します。

2. Vivado でカスタム オーディオ コーデック リファレンス設計を作成

I2C、I2S、および FIFO の各 IP は、カスタム リファレンス設計に組み込まれます。カスタム リファレンス設計の作成については、AMD ワークフロー用のカスタムのボードとリファレンス設計の定義の「Create and export a custom reference design using Xilinx Vivado」の節を参照してください。

このカスタム リファレンス設計を作成する際の主な注意点は次のとおりです。

ZedBoard のオーディオ コーデック チップの演算について、その理論を理解していなければなりません。

FIFO は、構成に応じて既定値に設定されます。

HDL ワークフロー アドバイザーを使用して生成される IP コアでは、IPCORE_CLK と AXI4_Lite_ACLK を同じクロック ソースに接続します。

Vivado でブロック設計を検証するときは、未接続の端子に関するものを除き、重大な警告がないことを確認します。

このリファレンス設計では、オーディオ コーデックはマスター モードで動作するように設定されます。

Zynq Soc のリファレンス設計と ZedBoard のオーディオ コーデックの間で実行される信号は次のとおりです。

"Bit_clock" は、サンプリング周波数、チャネルあたりのビット数、チャネル数の積です。マスター モードでオーディオ コーデックによって駆動されます。この例では、サンプリング周波数は 48 KHz、チャネル数は 2、チャネルあたりのビット数は 24 です。

"Left_right_select" は、左のオーディオ チャネルのデータと右のオーディオ チャネルのデータを区別します。ビット クロックと同期しています。

"Serial_data_in" は、コーデックからのアナログからデジタルに変換されたオーディオ データです。

"Serial_data_out" は、アナログ方式に変換するためにコーデックに送られるデジタル オーディオ データです。

"I2C_CLK" と "I2C_DATA" は、標準の I2C 信号です。

"ADDR0" と "ADDR1" は、I2C アドレス ビットです。

"Clk_24MHz" は、コーデックで必要な 24 MHz クロック信号です。

この例で作成されるカスタム オーディオ コーデック リファレンス設計は次のようになります。

3. リファレンス設計定義ファイルを作成

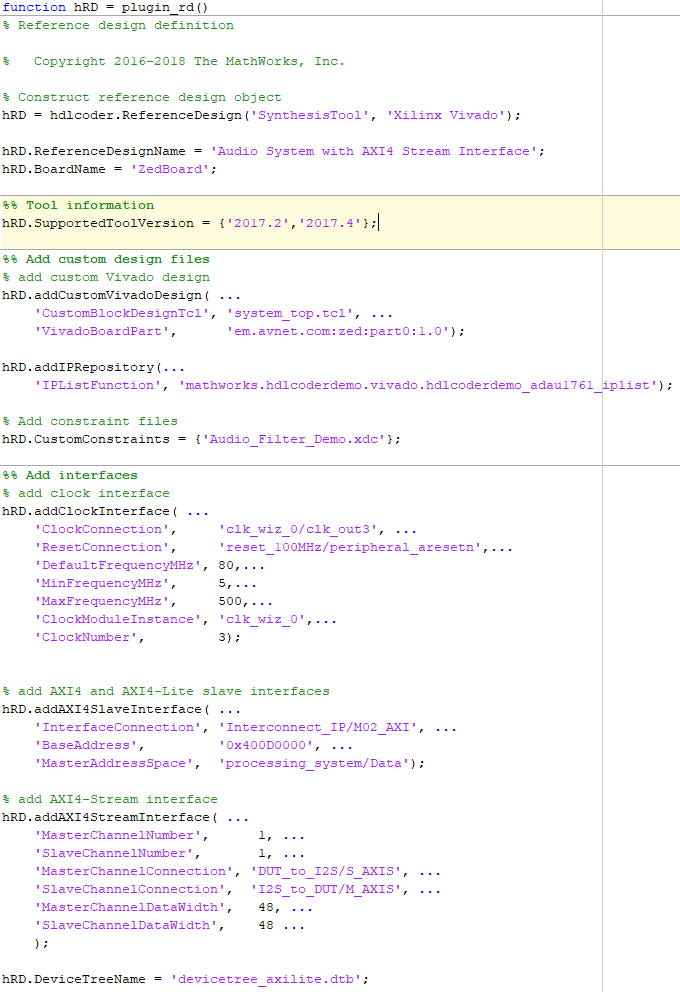

次のコードは、上記のリファレンス設計に対する ZedBoard リファレンス設計定義ファイル plugin_rd.m の内容を記述したものです。カスタム ボードを定義して登録する方法の詳細については、AMD ワークフロー用のカスタムのボードとリファレンス設計の定義の例を参照してください。

次のコマンドを使用して、"Zedboard" フォルダーを MATLAB パスに追加します。

example_root = (hdlcoder_amd_examples_root)

cd (example_root)

addpath(genpath('ZedBoard'));

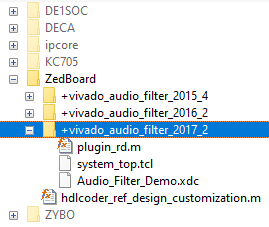

IP コア ファイル、XDC ファイル、plugin_rd ファイルなど、リファレンス設計に必要なすべてのファイルを MATLAB パスの "ZedBoard" フォルダー内に次の階層を使用して追加します。ユーザーが生成した IP コア ファイルは +vivado フォルダーに含めます。plugin_rd.m、tcl ファイル、および xdc ファイルは、+vivado_audio_filter_2017_2 フォルダーのようなリファレンス設計プラグイン フォルダーに含めます。

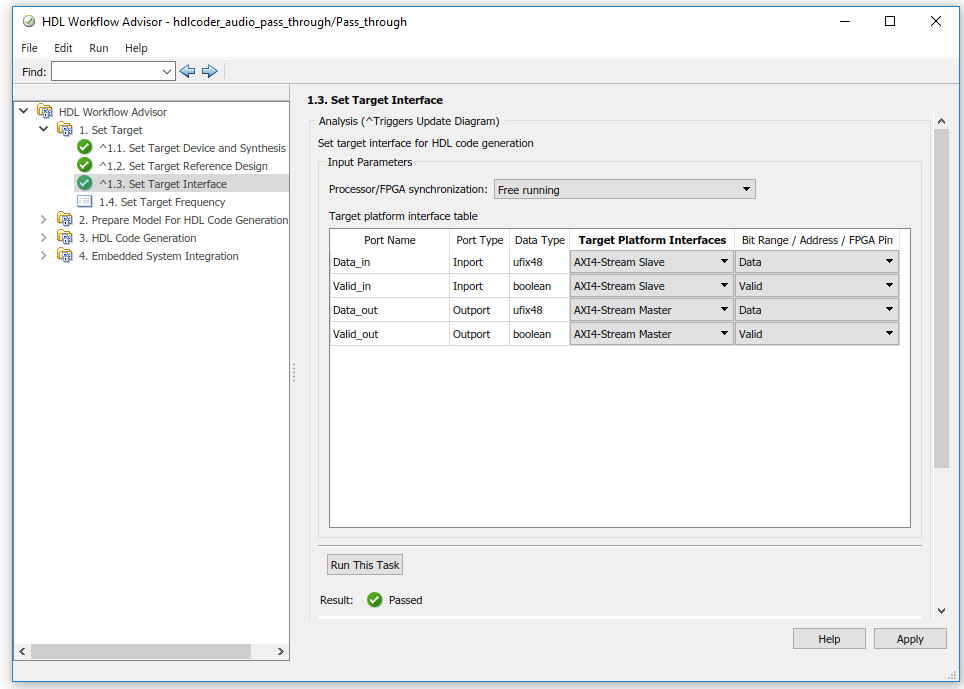

4. リファレンス設計を検証

リファレンス設計とリファレンス設計内のインターフェイスが想定どおりに機能することを確認するには、アルゴリズム IP を介してオーディオの送信のみを行う Simulink モデルを設計し、リファレンス設計と統合して ZedBoard でテストします。ユーザーにオーディオ ループ バックが聞こえなければなりません。

modelname = 'hdlcoder_audio_pass_through';

open_system(modelname);

モデル内のインターフェイスを次のように選択します。

モデルから IP コアを生成してオーディオ コーデック リファレンス設計に統合する方法については、Zynq ボードへのオーディオ フィルターの実装の例を参照してください。