AMD ワークフロー用のカスタムのボードとリファレンス設計の定義

この例では、Zynq® ワークフローでカスタム ボードとカスタム リファレンス設計を定義して登録する方法を示します。

はじめに

Zynq ワークフローの HDL ワークフロー アドバイザーで、Digilent® Zybo Z7-10 または Zybo Z7-20 Zynq の開発ボードとカスタム リファレンス設計を登録できます。

この例では Zybo Z7-10/Zybo Z7-20 Zynq ボードを使用していますが、それ以外の Zynq プラットフォーム用の他のカスタム ボードとカスタム リファレンス設計も定義して登録できます。

要件

HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアにリストされている、サポート対象バージョンの Xilinx Vivado Design Suite

Digilent® Zybo Z7-10/Zybo Z7-20 Zynq™ 開発ボードとアクセサリ キット

HDL Coder Support Package for AMD FPGA and SoC Devices

メモ: この例では、Digilent® Zybo Z7-10 または Zybo Z7-20 Zynq-7000 ARM/FPGA SoC トレーナー ボードを使用します。この例は、他の Zynq プラットフォーム用のカスタムのボードとリファレンス設計を作成する際の基準として使用できます。

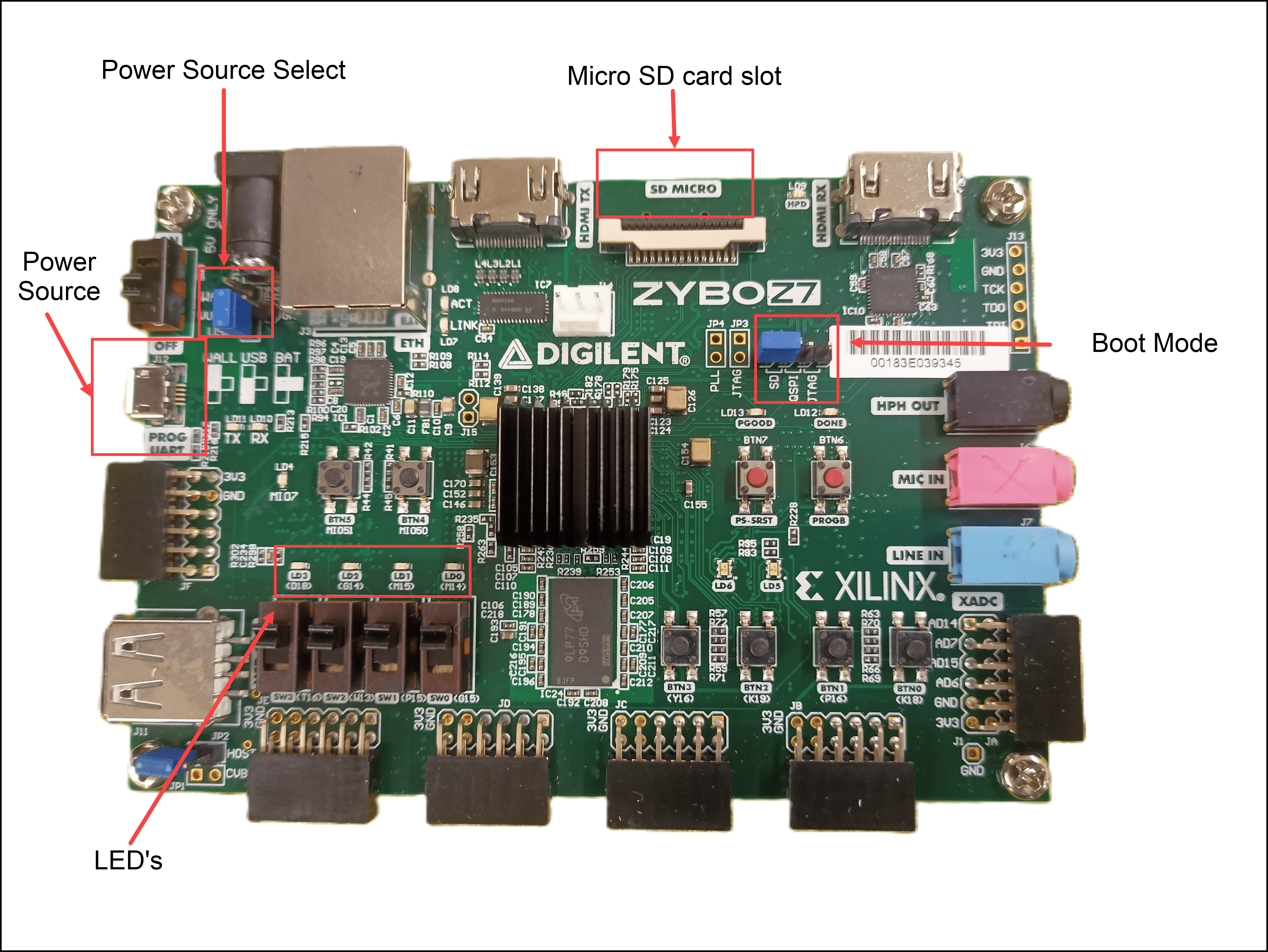

Zybo ボードの設定

Zybo ボードの機能について理解するには、Zybo Z7 ボードのリファレンス マニュアルを参照してください。

1. ボードを設定します。

Zybo Z7-10

Zybo Z7-20

2. USB COM ポートのデバイス ドライバーがコンピューターに適切にインストールされていることを確認します。

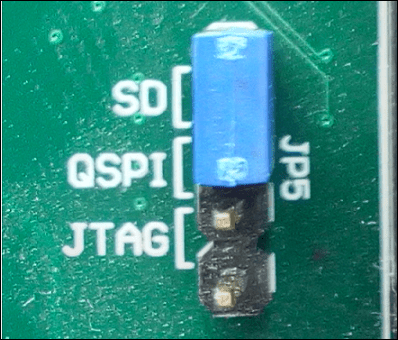

3. JP5 ブート モード ジャンパーで、コネクタ J4 に接続された microSD カードからの Zynq Linux イメージの読み込みを有効にするように構成します。

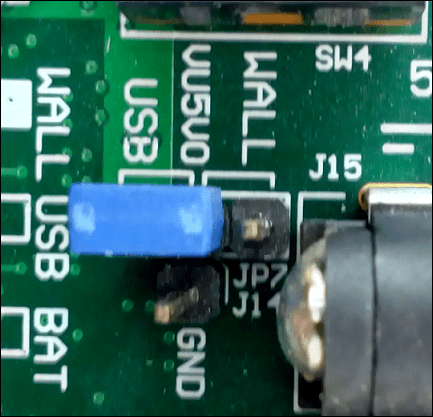

4. JP7 電源選択ジャンパーで、電源として USB を使用するように構成します。

5. Zybo ボード上の共有 UART/JTAG USB ポートをコンピューターに接続します。

6. イーサネット ケーブルを使用して Zybo Z7-10 または Zybo Z7-20 ボードをコンピューターに接続します。Zybo Z7-10 と Zybo Z7-20 の既定の IP アドレスは 192.168.1.101 です。

7. 使用しているボードに応じて Zybo Z7-10 Linux イメージまたは Zybo Z7-20 Linux イメージをダウンロードし、zip アーカイブを展開して内容を microSD カードにコピーし、microSD カードをコネクタ J4 に挿入します。HDL Coder IP コア用のカスタム Linux イメージのビルドに従って Linux イメージをビルドすることもできます。

8. hdlsetuptoolpathコマンドを使用して Xilinx Vivado ツール パスを設定します。

hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath', vivadopath);

コマンドを実行するときに独自の Xilinx Vivado インストール パスを使用します。

9. 次のコマンドを使用して Zynq ハードウェア接続を設定します。

h = zynq();

Xilinx Vivado を使用したカスタム リファレンス設計の作成とエクスポート

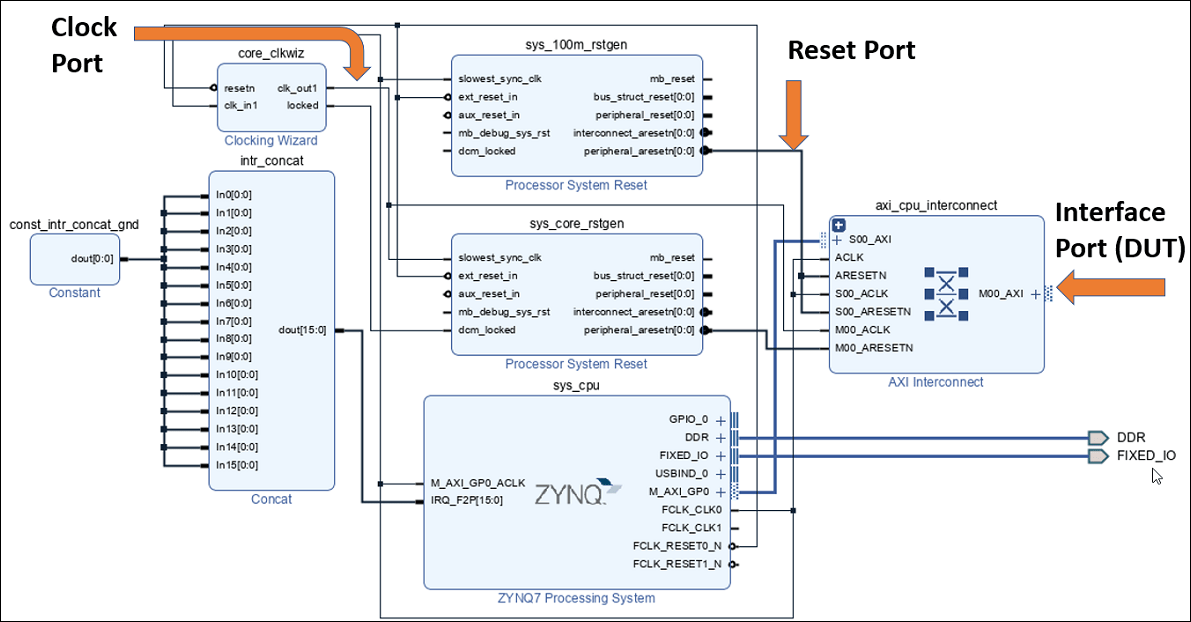

リファレンス設計は SoC 設計の構造全体を取得したもので、さまざまなコンポーネントやそれらの相互接続を定義します。HDL Coder の SoC ワークフローで生成される IP コアがリファレンス設計と統合され、SoC ボードのプログラミングに使用されます。次の図は、リファレンス設計、HDL IP コア、および SoC ボードの関係を示しています。

Xilinx Vivado IP Integrator 環境を使用して簡単なリファレンス設計を作成してエクスポートするには、次の手順に従います。IP Integrator ツールの詳細については、Xilinx のドキュメンテーションを参照してください。

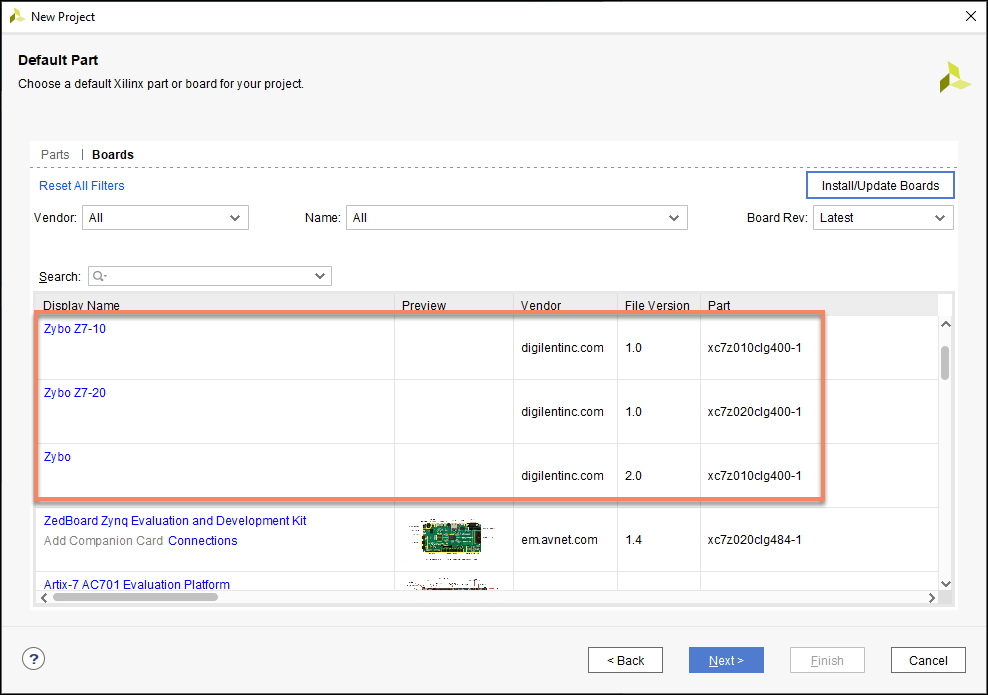

1. ボードのパーツ "Z********************************ybo Z7-10" または "Zybo Z7-20" を既定のボードとして使用して空の Xilinx Vivado RTL プロジェクトを作成します。

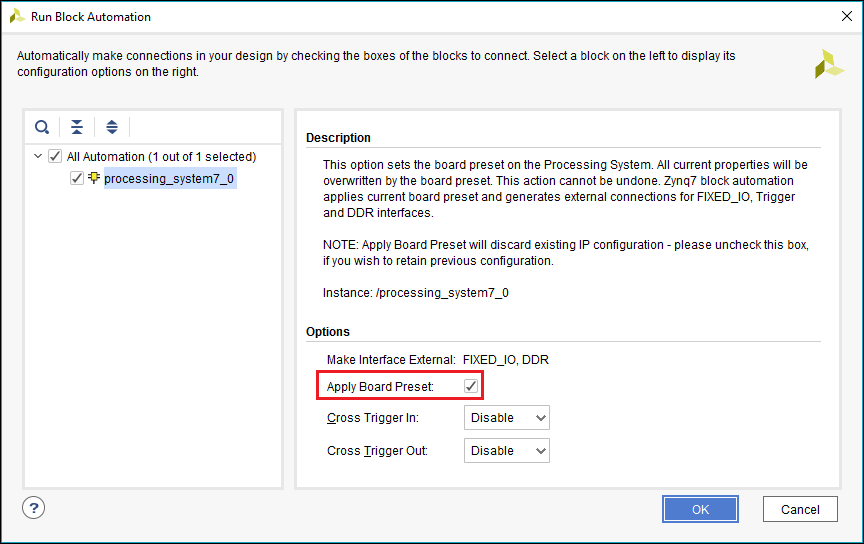

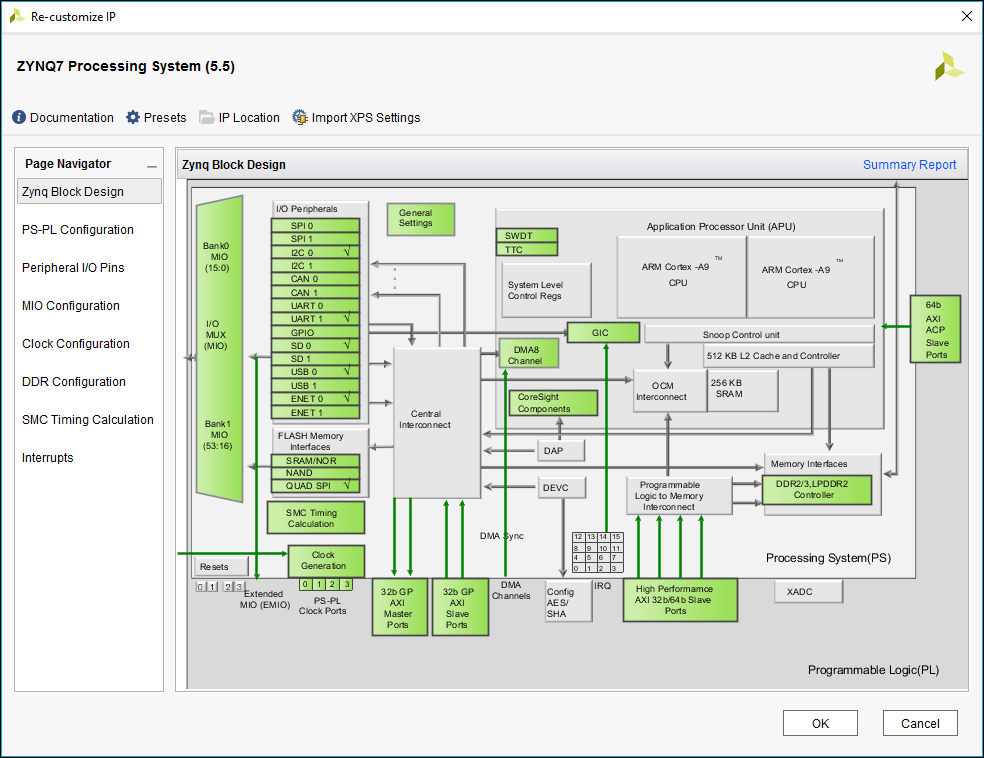

2. 空のブロック設計を作成し、"Z********************************YNQ7 Processing System" IP ブロックを追加します。ブロック オートメーションを実行して Zybo Z7-10 または Zybo Z7-20 のボード プリセットを設定します。これには、ZYNQ7 プロセッシング システム IP の MIO コンフィギュレーション、クロック コンフィギュレーション、および DDR コンフィギュレーションに関連するパラメーターが含まれます。

ボード プリセットを適用したため、Zybo ボード定義に従って MIO のペリフェラルがマークされています。

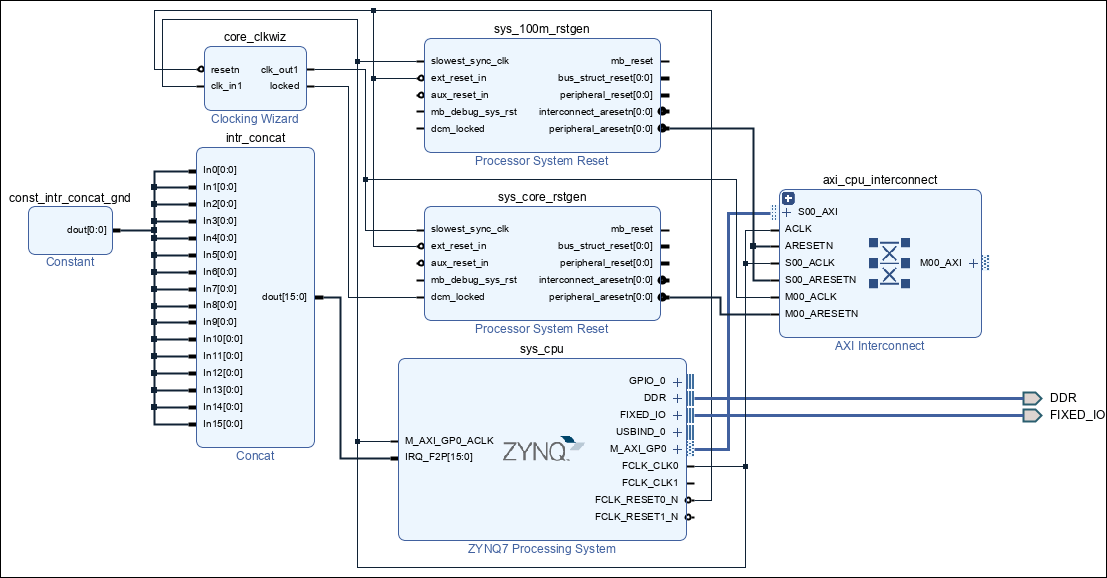

3. ブロック設計を完了します。

ブロック設計には HDL IP コアに関する情報は含まれないことに注意してください。

4. [File]、[Export]、[Export Block Design] を選択して、完成したブロック設計を Tcl スクリプト design_led.tcl としてエクスポートします。

エクスポートした Tcl スクリプト (design_led.tcl) でカスタム リファレンス設計が構成されます。この Tcl スクリプトを HDL Coder の SoC ワークフローで使用して、ブロック設計を再作成し、生成された HDL IP コアを Xilinx Vivado プロジェクトのブロック設計と統合します。これで、Xilinx Vivado を使用したカスタム リファレンス設計の作成とエクスポートのプロセスは完了です。

HDL ワークフロー アドバイザーでの Zybo Z7-10 または Zybo Z7-20 ボードの登録

このプロセスには、ボード登録ファイルとボード定義ファイルの作成が含まれます。

1. ボード登録ファイルを作成します。

ボード登録ファイルを hdlcoder_board_customization.m という名前で作成し、MATLAB パスに追加します。

ボード登録ファイルにはボート プラグインのリストが含まれます。ボード プラグインは、ボード定義ファイルとボードに関連付けられたすべてのリファレンス設計プラグインを格納する MATLAB パッケージ フォルダーです。

次のコードは、HDL ワークフロー アドバイザーで Zybo ボードを登録するためのボード プラグイン ZyboZ710Registration と ZyboZ720Registration を含むボード登録ファイルの内容を記述したものです。

function r = hdlcoder_board_customization % Board plugin registration file % 1. Any registration file with this name on MATLAB path will be picked up % 2. Registration file returns a cell array pointing to the location of % the board plugins % 3. Board plugin must be a package folder accessible from MATLAB path, % and contains a board definition file

r = { ...

'ZyboZ710Registration.plugin_board', ...

'ZyboZ720Registration.plugin_board'

};

end

2. ボード定義ファイルを作成します。

ボード定義ファイルには SoC ボードに関する情報が格納されます。

Zybo Z7-10

次のコードは、ボード プラグイン フォルダー ZyboZ710Registration 内にある Zybo ボード定義ファイル plugin_board.m の内容を記述したものです。

FPGA I/O ピンの位置 ('FPGAPin') と規格 ('IOSTANDARD') に関する情報は、Digilent の Web サイトの Zybo マスター制約ファイルから取得されます。

プロパティ BoardName で、HDL ワークフロー アドバイザーでの Zybo Z7-10 ボードの名前を ZYBO Z7-10 と定義しています。

function hB = plugin_board() % Board definition

% Construct board object

hB = hdlcoder.Board;

hB.BoardName = 'ZYBO Z7-10';

% FPGA device information hB.FPGAVendor = 'Xilinx'; hB.FPGAFamily = 'Zynq'; hB.FPGADevice = 'xc7z010'; hB.FPGAPackage = 'clg400'; hB.FPGASpeed = '-1';

% Tool information hB.SupportedTool = {'Xilinx Vivado'};

% FPGA JTAG chain position

hB.JTAGChainPosition = 2;

%% Add interfaces % Standard "External Port" interface hB.addExternalPortInterface( ... 'IOPadConstraint', {'IOSTANDARD = LVCMOS33'});

% Custom board external I/O interface hB.addExternalIOInterface( ... 'InterfaceID', 'LEDs General Purpose', ... 'InterfaceType', 'OUT', ... 'PortName', 'LEDs', ... 'PortWidth', 4, ... 'FPGAPin', {'M14', 'M15', 'G14', 'D18'}, ... 'IOPadConstraint', {'IOSTANDARD = LVCMOS33'});

hB.addExternalIOInterface( ... 'InterfaceID', 'Push Buttons', ... 'InterfaceType', 'IN', ... 'PortName', 'PushButtons', ... 'PortWidth', 4, ... 'FPGAPin', {'K18', 'P16', 'K19', 'Y16'}, ... 'IOPadConstraint', {'IOSTANDARD = LVCMOS33'});

hB.addExternalIOInterface( ... 'InterfaceID', 'Slide switches ', ... 'InterfaceType', 'IN', ... 'PortName', 'SlideSwitches', ... 'PortWidth', 4, ... 'FPGAPin', {'G15', 'P15', 'W13', 'T16'}, ... 'IOPadConstraint', {'IOSTANDARD = LVCMOS33'});

Zybo Z7-20

次のコードは、ボード プラグイン フォルダー ZyboZ720Registration 内にある Zybo ボード定義ファイル plugin_board.m の内容を記述したものです。

プロパティ BoardName で、HDL ワークフロー アドバイザーでの Zybo Z7-20 ボードの名前を ZYBO Z7-20 と定義しています。

function hB = plugin_board() % Board definition % Copyright 2024 The MathWorks, Inc. % Construct board object hB = hdlcoder.Board; hB.BoardName = 'ZYBO Z7-20'; % FPGA device information hB.FPGAVendor = 'Xilinx'; hB.FPGAFamily = 'Zynq'; hB.FPGADevice = 'xc7z020'; hB.FPGAPackage = 'clg400'; hB.FPGASpeed = '-1'; % Tool information hB.SupportedTool = {'Xilinx Vivado'}; % FPGA JTAG chain position hB.JTAGChainPosition = 2; %% Add interfaces % Standard "External Port" interface hB.addExternalPortInterface( ... 'IOPadConstraint', {'IOSTANDARD = LVCMOS33'}); % Custom board external I/O interface hB.addExternalIOInterface( ... 'InterfaceID', 'LEDs General Purpose', ... 'InterfaceType', 'OUT', ... 'PortName', 'LEDs', ... 'PortWidth', 4, ... 'FPGAPin', {'M14', 'M15', 'G14', 'D18'}, ... 'IOPadConstraint', {'IOSTANDARD = LVCMOS33'}); hB.addExternalIOInterface( ... 'InterfaceID', 'Push Buttons', ... 'InterfaceType', 'IN', ... 'PortName', 'PushButtons', ... 'PortWidth', 4, ... 'FPGAPin', {'K18', 'P16', 'K19', 'Y16'}, ... 'IOPadConstraint', {'IOSTANDARD = LVCMOS33'}); hB.addExternalIOInterface( ... 'InterfaceID', 'Slide switches ', ... 'InterfaceType', 'IN', ... 'PortName', 'SlideSwitches', ... 'PortWidth', 4, ... 'FPGAPin', {'G15', 'P15', 'W13', 'T16'}, ... 'IOPadConstraint', {'IOSTANDARD = LVCMOS33'}); % LocalWords: ZYBO Zynq xc Vivado JTAG IOSTANDARD LVCMOS

これで、HDL ワークフロー アドバイザーでのカスタム ボード プラグインの登録のプロセスは完了です。引き続き、次のセクションに進み、HDL ワークフロー アドバイザーで前に作成したカスタム リファレンス設計を登録できます。

HDL ワークフロー アドバイザーでのカスタム リファレンス設計の登録

このセクションでは、HDL ワークフロー アドバイザーでカスタム リファレンス設計を登録する方法について説明します。このプロセスには、カスタム リファレンス設計登録ファイルとカスタム リファレンス設計定義ファイルの作成が含まれます。

1. リファレンス設計登録ファイルを作成します。

SoC ボードに関連付けられたリファレンス設計プラグインのリストを格納するリファレンス設計登録ファイルを hdlcoder_ref_design_customization.m という名前で作成します。

リファレンス設計プラグインは、リファレンス設計定義ファイルと SoC 設計プロジェクトに関連付けられたすべてのファイルを格納する MATLAB パッケージ フォルダーです。リファレンス設計登録ファイルには、関連付けられたボードの名前も含める必要があります。

Zybo Z7-10

次のコードは、ボード ZYBO Z7-10 に関連付けられたリファレンス設計プラグイン ZyboZ710Registration.Vivado2020_2 および ZyboZ710Registration.Vivado2022_1 を含む Zybo リファレンス設計登録ファイルの内容を記述したものです。プラグインは、MATLAB パスで登録している Vivado ツールのバージョンに応じたものになります。サポートされている Vivado のバージョンを直接示すフォルダー名ではない可能性があることに注意してください。現在、次に示すように 2 つのカスタム リファレンス設計のサポートがあります。

function [rd, boardName] = hdlcoder_ref_design_customization % Reference design plugin registration file % 1. The registration file with this name inside of a board plugin folder % will be picked up % 2. Any registration file with this name on MATLAB path will also be picked up % 3. The registration file returns a cell array pointing to the location of % the reference design plugins % 4. The registration file also returns its associated board name % 5. Reference design plugin must be a package folder accessible from % MATLAB path, and contains a reference design definition file

rd = {

'ZyboZ710Registration.Vivado2020_2.plugin_rd', ...

'ZyboZ710Registration.Vivado2022_1.plugin_rd', ...

'ZyboZ710Registration.Vivado_Audio_filter_2020_2.plugin_rd', ...

'ZyboZ710Registration.Vivado_Audio_filter_2022_1.plugin_rd'

};

boardName = 'ZYBO Z7-10'; end

Zybo Z7-20

次のコードは、ボード ZYBO Z7-20 に関連付けられたリファレンス設計プラグイン ZyboZ720Registration.Vivado2023_1 を含む Zybo リファレンス設計登録ファイルの内容を記述したものです。プラグインは、MATLAB パスで登録している Vivado ツールのバージョンに応じたものになります。ZYBO Z7-20 ボードのサポートは Xilinx Vivado ツール version 2023.1 を使用して新たに追加されたため、フォルダー名に Vivado2023_1 が含まれています。

function [rd, boardName] = hdlcoder_ref_design_customization % Reference design plugin registration file % 1. The registration file with this name inside of a board plugin folder % will be picked up % 2. Any registration file with this name on MATLAB path will also be picked up % 3. The registration file returns a cell array pointing to the location of % the reference design plugins % 4. The registration file also returns its associated board name % 5. Reference design plugin must be a package folder accessible from % MATLAB path, and contains a reference design definition file % Copyright 2024 The MathWorks, Inc. rd = { 'ZyboZ720Registration.Vivado2023_1.plugin_rd', ... }; boardName = 'ZYBO Z7-20'; end % LocalWords: plugins Zybo Vivado ZYBO

2. リファレンス設計定義ファイルを作成します。

リファレンス設計定義ファイルは、カスタム リファレンス設計と HDL Coder の SoC ワークフローで生成される HDL IP コアの間のインターフェイスを定義します。

Zybo Z7-10

次のコードは、リファレンス設計プラグイン ZyboZ710Registration.Vivado2022_1 内にあるボード ZYBO Z7-10 に関連付けられた Zybo Z7-10 リファレンス設計定義ファイル plugin_rd.m の内容を記述したものです。プロパティ ReferenceDesignName で、HDL ワークフロー アドバイザーでのリファレンス設計の名前を Demo system と定義しています。

function hRD = plugin_rd() % Reference design definition

% Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado');

hRD.ReferenceDesignName = 'Demo system'; hRD.BoardName = 'ZYBO Z7-10';

% Tool information hRD.SupportedToolVersion = {'2022.1','2023.1'};

% add custom Vivado design hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'design_led.tcl', ... 'VivadoBoardPart','digilentinc.com:zybo-z7-10:part0:1.0');

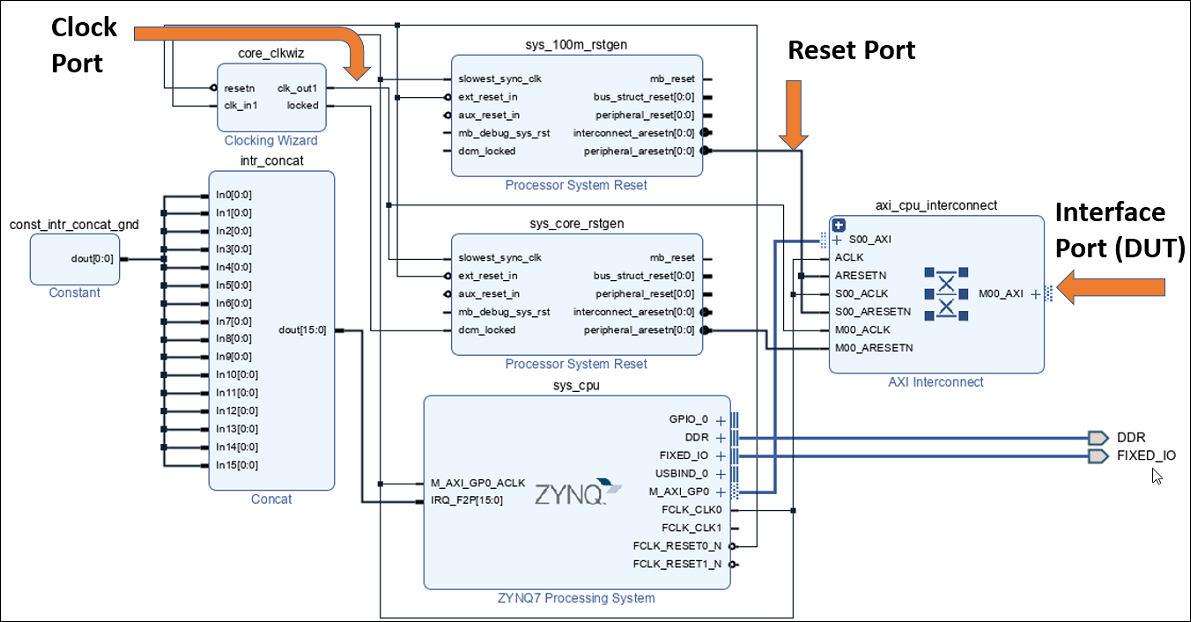

%% Add interfaces % add clock interface hRD.addClockInterface( ... 'ClockConnection', 'core_clkwiz/clk_out1', ... 'ResetConnection', 'sys_core_rstgen/peripheral_aresetn');

% add Register interfaces hRD.addRegisterInterface( ... 'InterfaceConnection', 'axi_cpu_interconnect/M00_AXI', ... 'BaseAddress', '0x40010000', ... 'MasterAddressSpace', 'sys_cpu/Data');

hRD.DeviceTreeName = 'devicetree_axilite.dtb';

リファレンス設計プラグインには、SoC 設計プロジェクト ファイルも含める必要があります。

Zybo リファレンス設計プラグイン フォルダー ZyboZ710Registration.Vivado2022_1 に、前に Xilinx Vivado プロジェクトからエクスポートした Tcl スクリプト design_led.tcl を含める必要があります。Zybo リファレンス設計定義ファイル plugin_rd.m で、SoC 設計プロジェクト ファイルを次のステートメントで識別します。

hRD.addCustomVivadoDesign('CustomBlockDesignTcl', 'design_led.tcl');

さらに、plugin_rd.m で、カスタム リファレンス設計と HDL IP コアの間のインターフェイス接続を次のステートメントで定義します。

hRD.addClockInterface( ... 'ClockConnection', 'core_clkwiz/clk_out1', ... 'ResetConnection', 'sys_core_rstgen/peripheral_aresetn'); hRD.addRegisterInterface( ... 'InterfaceConnection', 'axi_cpu_interconnect/M00_AXI', ... 'BaseAddress', '0x40010000', ... 'MasterAddressSpace', 'sys_cpu/Data');

メモ: AXI4 インターフェイスの 'BaseAddress' は、'MasterAddressSpace' にある有効なアドレスでなければなりません。カスタム リファレンス設計に含まれる他のアドレスベースのペリフェラルと競合するアドレスを使用してはなりません。

Zybo Z7-20

次のコードは、リファレンス設計プラグイン ZyboZ720Registration.Vivado2023_1 内にあるボード ZYBO Z7-20 に関連付けられた Zybo Z7-20 リファレンス設計定義ファイル plugin_rd.m の内容を記述したものです。プロパティ ReferenceDesignName で、HDL ワークフロー アドバイザーでのリファレンス設計の名前を Demo system と定義しています。

function hRD = plugin_rd() % Reference design definition % Copyright 2024 The MathWorks, Inc. % Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); hRD.ReferenceDesignName = 'Demo system'; hRD.BoardName = 'ZYBO Z7-20'; % Tool information hRD.SupportedToolVersion = {'2023.1'}; % add custom Vivado design hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'design_led.tcl', ... 'VivadoBoardPart', 'digilentinc.com:zybo-z7-20:part0:1.1'); %% Add interfaces % add clock interface hRD.addClockInterface( ... 'ClockConnection', 'core_clkwiz/clk_out1', ... 'ResetConnection', 'sys_core_rstgen/peripheral_aresetn'); % add Register interfaces hRD.addRegisterInterface( ... 'InterfaceConnection', 'axi_cpu_interconnect/M00_AXI', ... 'BaseAddress', '0x40010000', ... 'MasterAddressSpace', 'sys_cpu/Data'); hRD.DeviceTreeName = 'devicetree_axilite.dtb'; % LocalWords: Vivado ZYBO Tcl tcl digilentinc zybo wiz proc aresetn AXI axi % LocalWords: devicetree axilite dtb

Zybo ボードの SoC ワークフローの実行

カスタムのボードとリファレンス設計の登録システムを使用して、Zybo Z7-10/Zybo Z7-20 ボード上の LED を点滅させる HDL IP コアを生成します。使用する必要なファイルは ZYBO フォルダーにあります。

1. Zybo ボード登録ファイルを MATLAB パスに追加します。

example_root = (hdlcoder_amd_examples_root)

cd (example_root)

addpath(genpath('ZYBO'));

2. LED の点滅を実装する Simulink モデルを開きます。

open_system('hdlcoder_led_blinking_4bit');

3. hdlcoder_led_blinking_4bit/led_counter サブシステムを選択します。[アプリ] タブで、[HDL Coder] をクリックします。[HDL コード] タブの [アシスタンス] セクションで、[ワークフロー アドバイザー] をクリックして HDL ワークフロー アドバイザーを開きます。

4. [ターゲットを設定]、[ターゲット デバイスおよび合成ツールを設定] タスクで、[ターゲット ワークフロー] として [IP Core Generation] を選択します。[ターゲット プラットフォーム] のドロップダウン リストに ZYBO Z7-10 が表示されます。[ターゲット プラットフォーム] として ZYBO Z7-10 を選択します。[ターゲット プラットフォーム] として ZYBO Z7-20 を選択することもできます。このボードに対するサポートが HDL Coder Support Package for AMD FPGA and SoC Devices で新たに提供されています。

5. [このタスクを実行] をクリックして [ターゲット デバイスおよび合成ツールを設定] タスクを完了します。

6. [ターゲットを設定]、[ターゲットのリファレンス設計を設定] タスクで、[リファレンス設計] フィールドにカスタム リファレンス設計 Demo system が表示されます。Demo system を選択し、[このタスクを実行] をクリックします。

7. タスク 1.3 の [ターゲット インターフェイスを設定] で、接続を選択し、[このタスクを実行] をクリックします。

8. IP コアを生成して IP コアの生成レポートを表示するには、Simulink モデルからの IP コアの生成入門の "Generate an HDL IP core using the HDL Workflow Advisor" セクションに記載されている手順 3 と手順 4 に従います。

9. リファレンス設計に IP コアを統合して Vivado プロジェクトを作成するには、Simulink モデルからの IP コアの生成入門の "Integrate the IP core with the Xilinx Vivado environment" セクションに記載されている手順 1 に従います。

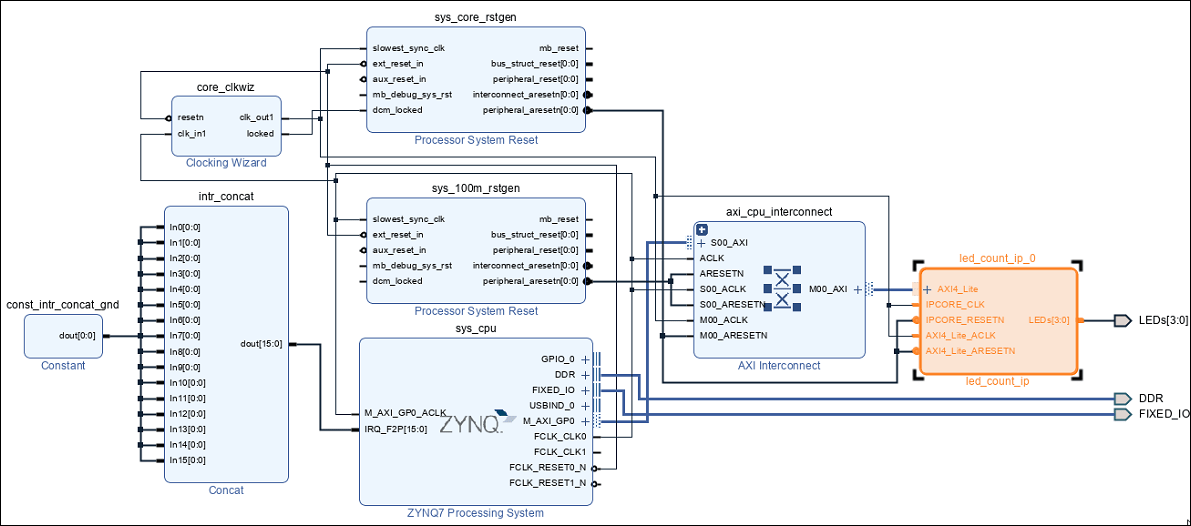

10. [組み込みシステムの統合] の [プロジェクトを作成] タスクが完了したら、SoC ワークフローで作成された Xilinx Vivado プロジェクトを確認します。次の図は、HDL IP コアを強調表示した SoC プロジェクトのブロック設計を示しています。カスタム リファレンス設計と HDL IP コアの関係をさらに詳しく理解するには、このブロック設計をカスタム リファレンス設計のエクスポート時に使用した前のブロック設計と比較します。

11. Simulink モデルからの IP コアの生成入門の例の "Integrate the IP core with the Xilinx Vivado environment" セクションに記載されている手順 2、3、4 にそれぞれ従って、ソフトウェア インターフェイス モデルを生成し、FPGA ビットストリームを生成し、ターゲット デバイスをプログラムします。

12. ビットストリームの読み込み後、Zybo Z7-10 または Zybo Z7-20 ボード上の LED が点滅を開始します。Zynq ARM プロセッサでソフトウェア インターフェイス モデルを実行して LED の点滅頻度および方向を制御できます。生成されたソフトウェア インターフェイス モデルから LED の点滅頻度および方向を制御するには、Simulink モデルからの IP コアの生成入門の例の "Generate a software interface model" セクションを参照してください。

まとめ

この例では、HDL ワークフロー アドバイザーで Zynq ワークフロー用のカスタム ボードを定義して登録する方法を示します。この例では、Xilinx Vivado を使用したカスタム リファレンス設計の作成とエクスポート、および HDL ワークフロー アドバイザーでのリファレンス設計の登録のプロセスについても説明しています。