このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

Intel ボードへのオーディオ フィルターの実装

この例では、次の方法について説明します。

ローパスおよびバンドパス フィルターを使用するオーディオ システムをモデル化する

オーディオ リファレンス設計を使用して Intel® ボードに実装する

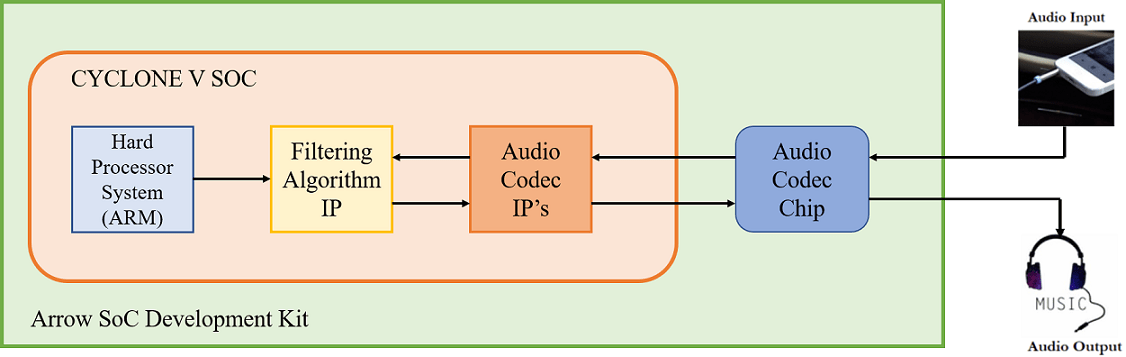

この例の目的は、Arrow SoC Development Kit のライン入力からオーディオ入力を受け取り、FPGA で処理してから、処理されたオーディオをスピーカーに送ることです。上の図は、このようなシステムの高度なアーキテクチャを示しています。ペリフェラルとのインターフェイスやアナログ信号とデジタル信号の間の変換には、オーディオ コーデックを使用します。Audio Codec IPs は、オーディオ コーデックの構成、および Intel SoC とオーディオ コーデックの間でのオーディオ データの転送に使用されます。フィルター IP は、オーディオの処理に使用されます。ARM プロセッサは、使用するフィルターのタイプ (ローパスまたはバンドパス) を制御するために使用されます。

はじめる前に

この例を実行するには、次のソフトウェアとハードウェアをインストールして設定していなければなりません。

HDL Coder™ Support Package for Intel FPGA and SoC Devices

Embedded Coder® Support Package for Intel SoC Devices

HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアにリストされている、サポートされているバージョンの Intel Quartus® Prime Standard

Intel SoC Embedded Design Suite

Arrow SoC Development Kit

Arrow SoC Development Kit を設定するには、Get Started with IP Core Generation for Intel SoC Devicesの例の「Set up Intel SoC hardware and tools」セクションを参照してください。以下に示すように Arrow SoC で、モバイルまたは MP3 プレーヤーのオーディオ入力を "LINE IN" ジャックに接続し、イヤフォンまたはスピーカーを "LINE OUT" ジャックに接続します。

はじめに

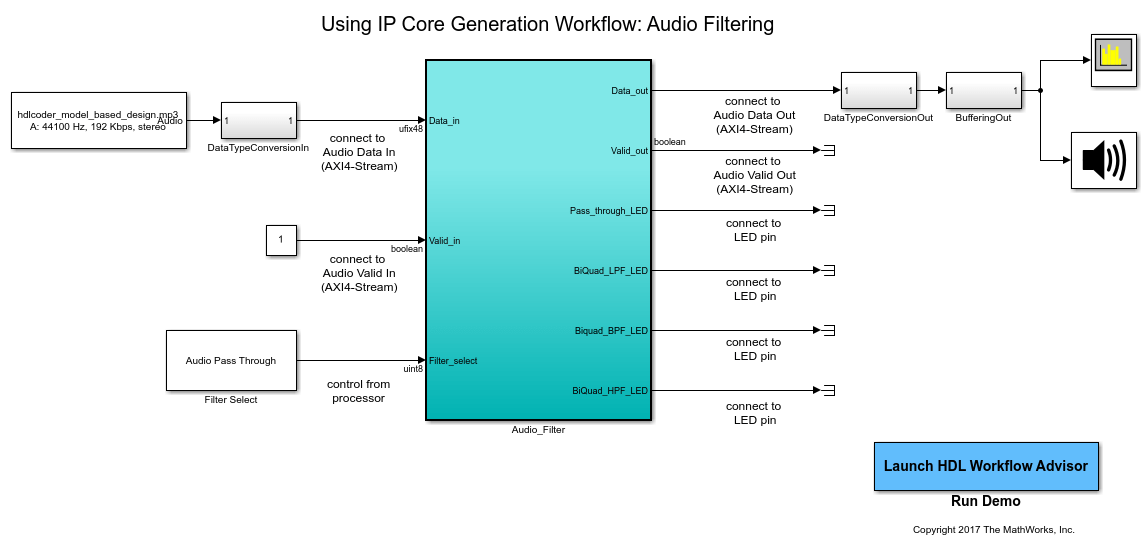

次のモデルでは、DUT サブシステム Audio_filter への入力としてオーディオ ファイルが使用されます。このモデルを Simulink でシミュレートすると、処理されたオーディオ エフェクトが Audio Device Writer ブロックを通じて聞こえ、フィルター処理されたオーディオ出力のスペクトログラムが Spectrum Analyzer ブロックで表示されます。

modelname = 'hdlcoder_audio_filter_biquad';

open_system(modelname);

ローパスおよびバンドパス フィルターを使用するシステムのモデル化

フィルター係数は、MATLAB 関数を使用して生成するか、Simulink で生成されます。このモデルでは、filterDesigner (DSP System Toolbox)ツールを使用して各タイプのフィルターのフィルター係数が生成されます。その後、それらのフィルター係数がエクスポートされて MATLAB ファイルとして保存されます。これらのフィルター係数が Simulink でのフィルターの設計に使用されます。このモデルでは、対応するフィルター係数に応じて、Simulink® の離散 IIR フィルター ブロックが双二次ローパスまたはバンドパス フィルターとして使用されます。

このモデルは、モデルを Simulink でシミュレートしてテストできます。Spectrum Analyzer で表示される周波数の範囲と Audio Device Writer ブロックを通じて聞こえるオーディオ エフェクトが、選択したフィルターのタイプに応じて変わるはずです。オーディオ入力に対して実行するフィルター処理のタイプは、Filter Select ブロックを使用して選択されます。

Arrow SoC Development Kit のモデルのカスタマイズ

このモデルを Arrow SoC に実装するには、Arrow SoC でオーディオ入力を受け取り、処理されたオーディオ データを Arrow SoC から送信するリファレンス設計を Qsys で最初に作成しなければなりません。オーディオ フィルター モデルを統合するリファレンス設計を作成する方法の詳細については、基本的な Intel 評価ボードのオーディオ システム リファレンス設計の作成の例を参照してください。

リファレンス設計では、左右のチャネルのオーディオ データが組み合わされて単一チャネルが形成されます。下位 24 ビットを左チャネル、上位 24 ビットを右チャネルとして連結されます。上記の Simulink モデルでは、Data_in が左右の 2 つのチャネルに分割されます。それらの振幅が 2 つに分けられ、2 つのチャネルが一緒に追加されて単一チャネルが形成されます。このチャネルでフィルター処理が実行されます。

Data_in と Valid_in は AXI4-Stream 信号です。Data_in は処理するデータを格納し、Valid_in はイネーブル信号として動作します。各フィルターは Arrow SoC の LED にマッピングされており、そのフィルターがオンとオフのどちらであるかが視覚的に示されます。

"FilterSelect" 入力は AXI4 インターフェイスで制御されます。

AXI4-Stream インターフェイスを使用した HDL IP コアの生成

次に、HDL ワークフロー アドバイザーを起動し、Intel® ハードウェア ソフトウェア協調設計ワークフローを使用して、この設計を Intel ハードウェアに展開します。詳しい手順については、Get Started with IP Core Generation for Intel SoC Devicesの例を参照してください。

1. MATLAB コマンド ウィンドウでhdlsetuptoolpathコマンドを使用して Intel Quartus 合成ツール パスを設定します。コマンドを実行するときに独自の Intel Quartus インストール パスを使用します。以下に例を示します。

hdlsetuptoolpath('ToolName', 'Altera Quartus II', 'ToolPath', quartuspath);

2. 次のコマンドを使用して、IP リポジトリ フォルダーと Arrow SoC Development Kit 登録ファイルの両方を MATLAB パスに追加します。

example_root = (hdlcoder_intel_examples_root) cd (example_root) addpath(genpath('ipcore')); addpath(genpath('ArrowSoC'));

3. DUT サブシステム hdlcoder_audio_filter_biquad/Audio_filter から HDL ワークフロー アドバイザーを開始するか、モデルの [Launch HDL Workflow Advisor] ボックスをダブルクリックします。

タスク 1.1 では、[ターゲット ワークフロー] で [IP Core Generation] を選択し、[ターゲット プラットフォーム] で Arrow SoC Development Kit を選択します。

タスク 1.2 では、[リファレンス設計] で Audio System with AXI4 Stream Interface が選択されます。

リファレンス設計と Filtering Algorithm IP の間のオーディオ データの転送には、AXI4-Stream インターフェイスが使用されます。AXI4-Stream インターフェイスにはデータ (Data) に加え、データ有効 (Valid)、バック プレッシャー (Ready)、データの境界 (TLAST) などの制御信号が含まれます。AXI4-Stream IP コアの生成には、少なくとも Data 信号と Valid 信号が必要です。タスク 1.3 では、次の図に示すように [ターゲット プラットフォーム インターフェイス テーブル] が読み込まれます。オーディオ データ ストリーム端子 "Valid_in"、"Data_in"、"Valid_out"、および "Data_out" が AXI4-Stream インターフェイスにマッピングされ、"Pass_through_LED"、"BiQuad_LPF_LED"、"BiQuad_BPF_LED" が Arrow SoC 上の LED にマッピングされ、制御パラメーター端子 "Filter_select" が AXI4 インターフェイスにマッピングされます。

AXI4-Stream インターフェイスはマスター/スレーブ モードで通信します。このモードでは、マスター デバイスがデータをスレーブ デバイスに送信します。したがって、データ端子が入力端子である場合、これを AXI4-Stream スレーブ インターフェイスに割り当て、データ端子が出力端子である場合、これを AXI4-Stream マスター インターフェイスに割り当てます。

3. タスク 3.2 [RTL コードと IP コアの生成] を右クリックして、[選択したタスクまで実行] を選択し、IP コアを生成します。生成された IP コア レポート内の IP コアについては、レジスタ アドレス マッピングおよびその他のドキュメントを参照してください。

AXI4-Stream Audio 互換のリファレンス設計への IP の統合

次に、HDL ワークフロー アドバイザーで、[組み込みシステムの統合] タスクを実行して、生成された HDL IP コアを Intel SoC に展開します。

1. タスク 4.1 [プロジェクトを作成] を実行します。このタスクでは、生成された IP コアが Audio System with AXI4 Stream Interface リファレンス設計に挿入されます。最初の図に表示されているように、このリファレンス設計には、Arrow SOC で送受信される内外のオーディオ データを処理する IP が含まれます。生成されたプロジェクトは完全な設計であり、アルゴリズム部分 (生成された DUT アルゴリズムの IP) とプラットフォーム部分 (リファレンス設計) が含まれます。オーディオ フィルター モデルを統合するリファレンス設計を作成する方法の詳細については、基本的な Intel 評価ボードのオーディオ システム リファレンス設計の作成の例を参照してください。

2. [結果] ペインの [Generated Altera Qsys project] リンクをクリックして、生成されたプラットフォーム デザイナー Qsys プロジェクトを開きます。

3. HDL ワークフロー アドバイザーで、残りのタスクを実行してソフトウェア インターフェイス モデルを生成し、FPGA ビットストリームを作成およびダウンロードします。[ターゲット デバイスをプログラム] タスクで [ダウンロード] プログラミング メソッドを選択して、FPGA ビットストリームを Intel ボード上の SD カードにダウンロードし、Intel ボードの電源をオフ/オンすると設計が自動的に再読み込みされるようにします。

FPGA ファブリックでパラメーターを調整するための ARM 実行可能ファイルの生成

ソフトウェア インターフェイス モデルはタスク 4.2 [ソフトウェア インターフェイス モデルを生成] で生成されます。

1. ソフトウェア インターフェイス モデルからコードを生成する前に、オーディオ入力ソースとオーディオ出力シンク、つまり From Multimedia File、Data Type Conversion、Buffer、Audio Device Writer、および Spectrum Analyzer の各ブロックをコメントアウトします。これらのブロックは ARM プロセッサで実行する必要はありません。Audio_filter IP は FPGA ファブリックで Filtering_Algorithm として実行されています。ARM プロセッサは、フィルター タイプ (双二次ローパス、バンドパス、またはパススルー) の選択に AXI4 インターフェイスを使用しています。

生成されたモデルで、[ハードウェア] ペインに移動し、[ハードウェア設定] をクリックして [コンフィギュレーション パラメーター] ダイアログ ボックスを開きます。

[ソルバー] を選択して [終了時間] を [inf] に設定します。

次に、[ハードウェア] ペインで [監視と調整] ボタンをクリックします。Embedded Coder は、モデルを構築し、ARM 実行可能ファイルを Intel ボード ハードウェアにダウンロードして、これを実行し、モデルを Intel ボード ハードウェアで実行しているこの実行可能ファイルに接続します。次に、モデル パラメーターを調整できます。

使用するフィルターのタイプは、Filter Select ブロックのドロップ ダウン オプションを使用して選択できます。

フィルター処理されたオーディオ出力は、Arrow SoC の "LINE OUT" ジャックにイヤフォンまたはスピーカーを接続して聴くことができます。選択されたフィルターに応じて、Arrow SoC の対応する LED がオンになります。この例では、パススルー (フィルターを使用しない) オプションが選択されると LD0 がオンになり、双二次ロー パス フィルターが選択されると LD1 がオンになり、双二次バンドパス フィルターが選択されると LD2 がオンになります。