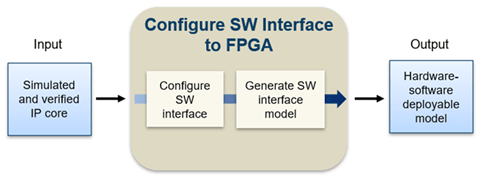

FPGA へのソフトウェア インターフェイスの構成

設計した IP コアに接続し、ターゲット ハードウェアの組み込みプロセッサに展開するソフトウェア インターフェイス モデルの構成

ターゲット プラットフォームの組み込みプロセッサで実行されるアルゴリズムを含むソフトウェア インターフェイス モデルを作成します。入力は、テストおよび検証済みの IP コア モデルです。出力は、FPGA とプロセッサ間の通信を含むソフトウェア インターフェイス モデル、および SoC デバイスまたは Simulink® Real-Time™ ターゲット マシンに搭載されている組み込みプロセッサに展開されるアルゴリズムです。ワークフローの詳細については、FPGA および SoC ハードウェアをターゲットにする方法の概要を参照してください。

トピック

- Choose a Method to Interact with IP Cores on Target Hardware

Choose a software interface method to interact with IP cores running on target hardware.

- HDL IP コアを調査して迅速にプロトタイプを作成するためのソフトウェア インターフェイス モデルの生成

ソフトウェア インターフェイス モデルを生成して HDL IP コアと通信し、ラピッド プロトタイピングを実行する。

- Generate Device Tree for IP Core

Generate device tree files that include the HDL Coder™ generated IP core.