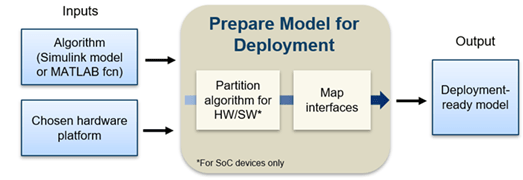

展開用モデルの準備

FPGA に展開するモデルまたは MATLAB 関数を準備します。入力は、Simulink® モデルまたは MATLAB 関数、および選択したハードウェア プラットフォームです。出力は、スタンドアロン FPGA の展開専用に設計された分割モデル、SoC デバイスに搭載されている FPGA、または Simulink Real-Time™ ターゲット マシン上の FPGA I/O ボードです。

ワークフローの詳細については、FPGA および SoC ハードウェアをターゲットにする方法の概要を参照してください。

トピック

- AXI4 スレーブ インターフェイスの生成のための設計のモデル化

スカラー端子、ベクトル端子、バス データ型の AXI4 または AXI4-Lite インターフェイス用のモデルの設計および値の読み戻し方法。

- Map Bus Data Types to AXI4 Slave Interfaces

This example shows how to map bus data types to an AXI4 slave interface, generate an HDL IP core with a AXI4 Master interface, perform matrix multiplication in an HDL IP core, and write the output result to DDR memory. In this example, you:

- AXI4-Stream インターフェイス生成向けのモデル設計

AXI4-Stream ベクトルまたはスカラー インターフェイス生成向けのモデルの設計法

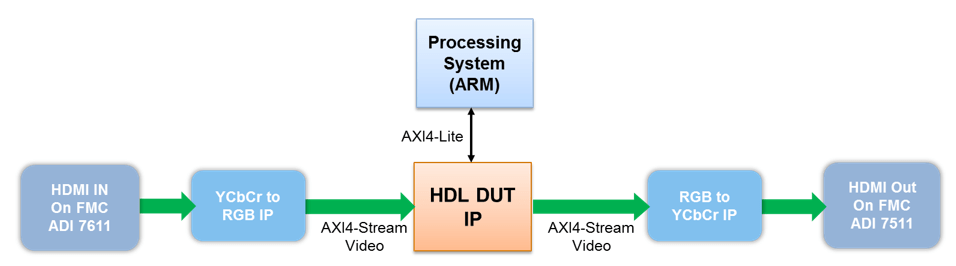

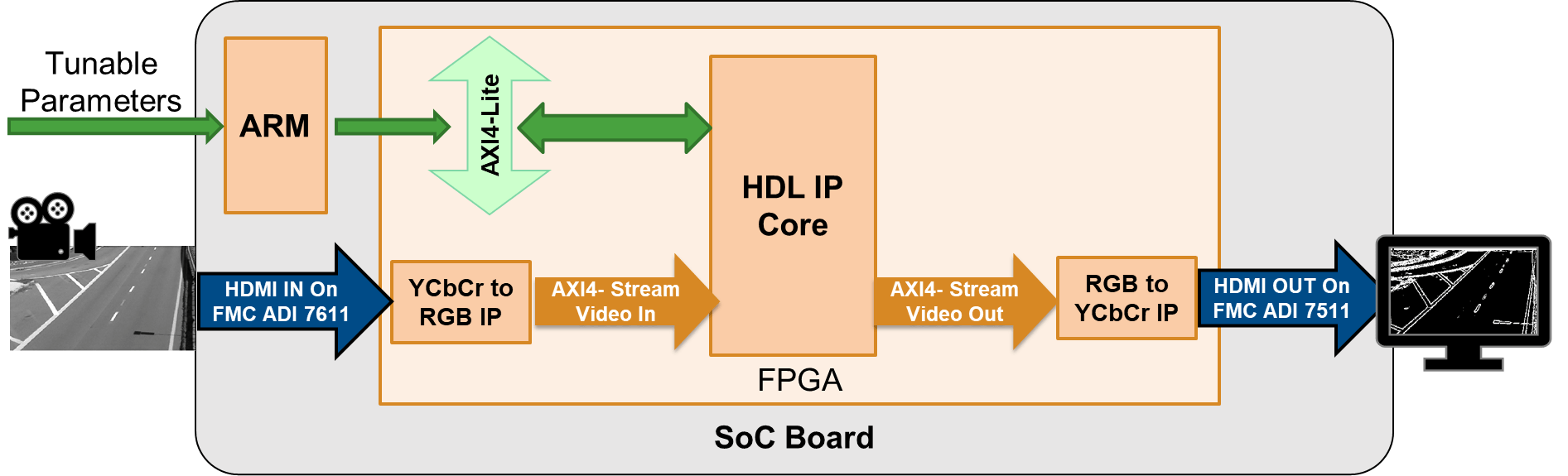

- AXI4-Stream Video インターフェイス生成向けのモデル設計

AXI4-Stream Video インターフェイスをもつ IP コア生成のためのモデルの設計法。

- AXI4 Master インターフェイスを生成するためのモデル設計

AXI4 Master プロトコルの説明および AXI4-Master インターフェイスを備えた IP コアの生成用にモデルを設計する方法の説明。

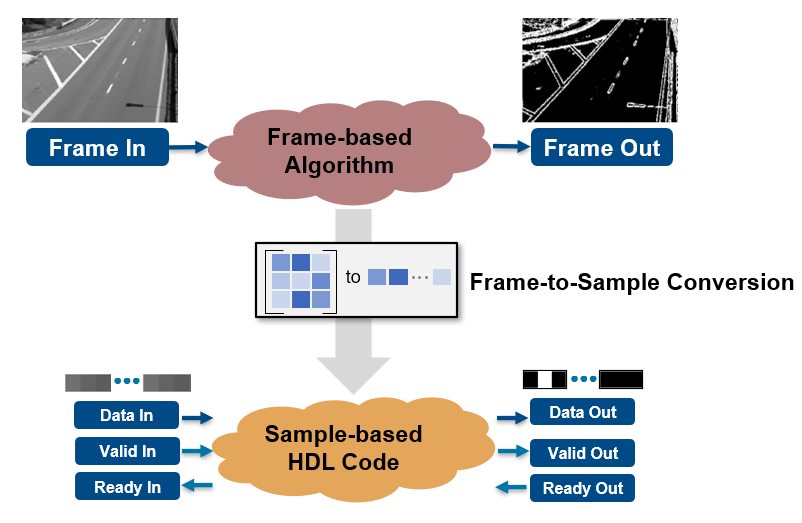

- Model Design for Frame-Based IP Core Generation

How to design your model to use the frame-to-sample optimization for IP core generation.

- Save Target Hardware Settings in Model

This example shows how to save your target hardware settings in a Simulink® model.