AXI4-Stream Video インターフェイスを使用した IP コアの生成

この例では、生成された HDL IP コアでの高速ビデオ ストリーミングを可能にする AXI4-Stream Video インターフェイスの使用方法を説明します。

要件

この例を実行するには、次のソフトウェアとハードウェアをインストールして設定していなければなりません。

HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアにリストされている、サポートされているバージョンの Xilinx® Vivado® Design Suite

ZedBoard™

FMC HDMI I/O カード (FMC-HDMI-CAM または FMC-IMAGEON)

ZedBoard を設定するには、Simulink モデルからの IP コアの生成入門の例の "Zynq ハードウェアとツールの設定" セクションを参照してください。

はじめに

以下の例では、次のような操作方法を説明します。

ストリーミング ピクセル プロトコルを使用したビデオ ストリーミング アルゴリズムのモデル化。

AXI4-Stream Video インターフェイスを使用した HDL IP コアの生成。

HDMI インターフェイスにアクセスできる ZedBoard ビデオ リファレンス設計への生成された IP コアの統合。

ARM® プロセッサを使用した FPGA ファブリックでのパラメーター調整によるライブ ビデオ出力の変更。

独自のカスタム ビデオ リファレンス設計の作成。

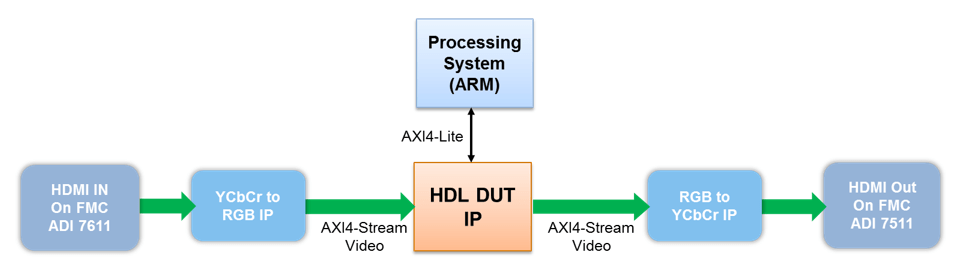

上記の図は、生成された HDL DUT IP コアが事前定義されたビデオ リファレンス設計でどのように機能するかを示すアーキテクチャの概要図です。この図で、HDL DUT IP ブロックは IP コアの生成ワークフローから生成された IP コアです。図の他の部分は事前定義されたビデオ リファレンス設計を表し、この設計には HDMI 入力インターフェイスと HDMI 出力インターフェイスを処理する他の IP が含まれます。

HDL DUT IP は、HDMI 入力 IP からのビデオ ストリームを処理し、出力ビデオ ストリームを生成して HDMI 出力 IP に送信します。これらのビデオ ストリームはすべて AXI4-Stream Video インターフェイスで転送されます。

HDL DUT IP には、パラメーター調整のために AXI4-Lite インターフェイスを含めることもできます。AXI4-Lite インターフェイスと比べて、AXI4-Stream Video インターフェイスは、データをより高速に転送するため、ビデオ アルゴリズムのデータ パスにより適しています。

Zynq ハードウェアとツールの設定

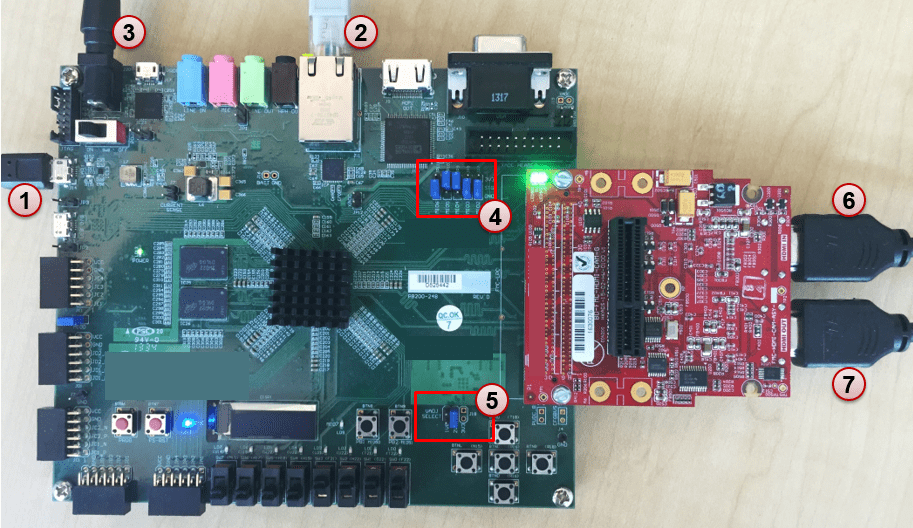

1. 以下の図に示すように ZedBoard と FMC HDMI I/O カードを設定します。ZedBoard ハードウェアの設定の詳細については、ボードのドキュメンテーションを参照してください。

2. 上の図 (マーカー 1 ~ 3) に示すように USB UART ケーブル、イーサネット ケーブルおよび電力ケーブルを接続します。

3. 上の図 (マーカー 4) に示すように JP7 ~ JP11 のジャンパーが設定されており、Linux を SD カードから起動できるようになっていることを確認します。JP7: 下、JP8: 下、JP9: 上、JP10: 上、JP11: 下です。

4. 上の図 (マーカー 5) に示すように J18 のジャンパーが 2V5 で設定されていることを確認します。

5. 上の図 (マーカー 6) に示すように HDMI ビデオ ソースを FMC HDMI I/O カードに接続します。ビデオ ソースは 1080p ビデオ出力 (ビデオ カメラ、スマート フォン、タブレット、コンピューターの HDMI 出力など) を提供できなければなりません。

6. 上の図 (マーカー 7) に示すようにモニターを FMC HDMI I/O カードに接続します。モニターは 1080p 表示をサポートできなければなりません。

7. まだインストールしていない場合は、HDL Coder™ Support Package for AMD FPGA and SoC Devices をインストールします。サポート パッケージをインストールするには、MATLAB® ツールストリップに移動して [アドオン]、[ハードウェア サポート パッケージの入手] をクリックします。

8. HDL Coder Support Package for AMD FPGA and SoC Devices で提供される SD カード イメージを使用していることを確認します。SD カード イメージを更新する必要がある場合は、AMD SoC ボード用のサポートのインストール (Embedded Coder)の「Hardware Setup」セクションを参照してください。

9. MATLAB コマンド ウィンドウで次のコマンドを入力して Zynq® ハードウェア接続を設定します。

h = zynq

関数 zynq は COM ポートを介してハードウェアにログインし、ifconfig コマンドを実行してボードの IP アドレスを取得します。この関数はイーサネット接続のテストも行います。

10. hdlsetuptoolpathコマンドを使用して Xilinx Vivado 合成ツール パスを設定します。コマンドを実行するときに独自の Vivado インストール パスを使用します。

hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath', vivadopath)

ストリーミング ピクセル プロトコルを使用したビデオ ストリーミング アルゴリズムのモデル化

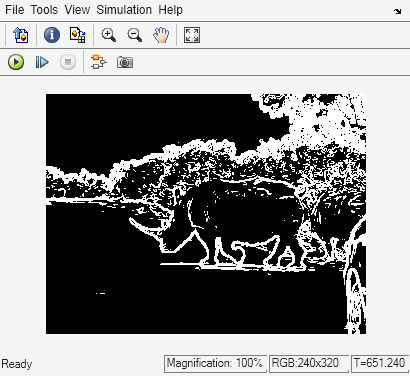

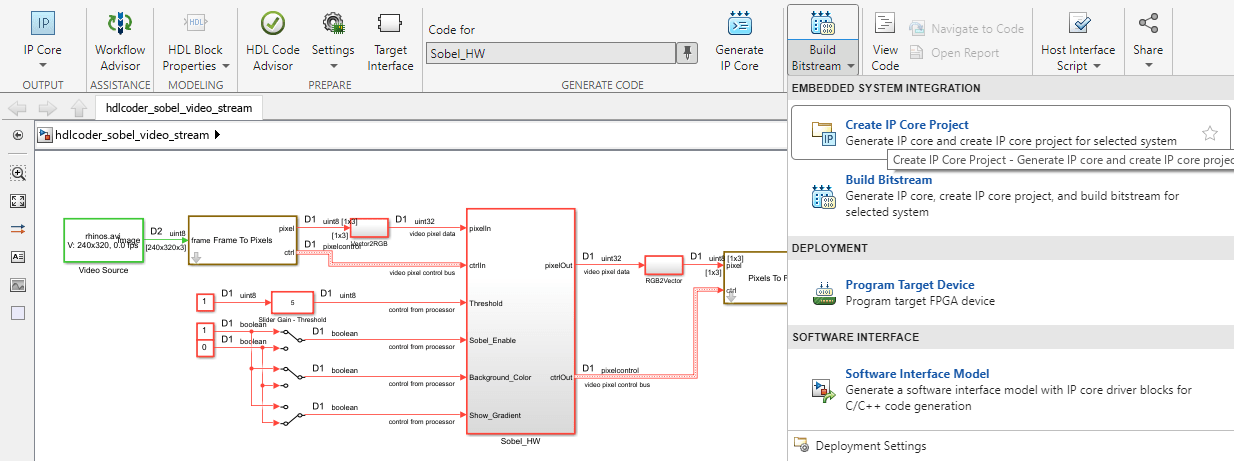

Zynq ハードウェアに簡単なソーベル エッジ検出アルゴリズムを展開するには、まず、設計のどの部分を FPGA で実行し、設計のどの部分を ARM プロセッサで実行するかを特定します。この例では、エッジ検出器を FPGA に実装し、着信ビデオ ストリームを AXI4-Stream Video プロトコルで処理します。ARM プロセッサにより、FPGA でパラメーターを調整し、ライブ ビデオ出力を変更します。

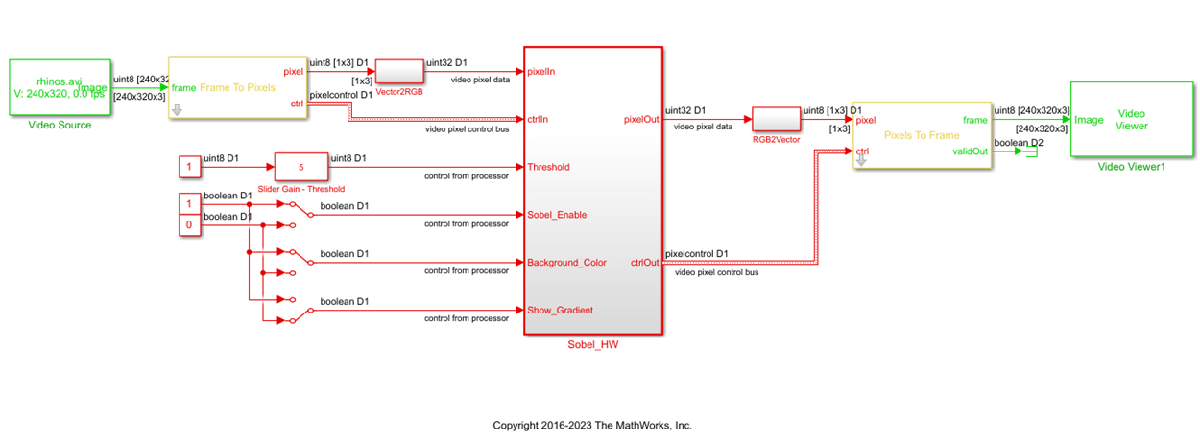

モデル例では、DUT サブシステム Sobel_HW が Edge Detector ブロックを使用してソーベル エッジ検出アルゴリズムを実装します。ビデオ データと制御信号は、Vision HDL Toolbox™ のすべてのブロックで使用されるビデオ ストリーミング ピクセル プロトコルでモデル化されています。pixelIn と pixelOut はビデオ ストリームのデータ端子です。ctrlIn と ctrlOut はビデオ ストリームの制御端子です。これらは、信号 hStart、hEnd、vStart、vEnd、valid を含むバス データ型 (Pixel Control Bus) を使用してモデル化されています。

4 つの入力端子 Threshold、Sobel_Enable、Background_Color および Show_Gradient は、ソーベル エッジ検出アルゴリズムのパラメーターを調整する制御端子です。Slider Gain ブロックまたは Manual Switch ブロックを使用してこれらの端子の入力値を調整できます。これらの端子を AXi4-Lite インターフェイスにマッピングすると、生成された AXI インターフェイスのアクセス可能なレジスタに書き込むことで、ARM プロセッサが生成された IP コアを制御できます。

modelname = 'hdlcoder_sobel_video_stream';

open_system(modelname);

sim(modelname);

AXI4-Stream Video インターフェイスを使用した HDL IP コアの生成

R2023b 以降

次に、IP コア生成のモデルを構成し、設計およびターゲット インターフェイスを構成し、IP コアを生成します。この例では Simulink® ツールストリップの [HDL コード] タブを使用して IP コアを生成します。HDL ワークフロー アドバイザーを使用して IP コアを生成するには、Comparison of IP Core Generation Techniquesを参照してください。その後、生成された IP コアを Zynq ハードウェアに展開し、組み込みプロセッサに接続できます。詳しい手順については、Simulink モデルからの IP コアの生成入門を参照してください。特定のハードウェア プラットフォーム用の IP コアを生成する方法の概要については、FPGA および SoC ハードウェアをターゲットにする方法の概要を参照してください。

IP コア生成用のモデルの準備

コンフィギュレーション パラメーターを使用してモデルを準備し、IP コア エディターを使用して設計を構成し、Simulink ツールストリップの [HDL コード] タブを使用して IP コアを生成します。この例では、ターゲット インターフェイスの設定は既にモデルに適用されています。モデルのターゲット インターフェイス設定の保存の詳細については、Save IP Core Generation and Target Hardware Settings in Modelを参照してください。

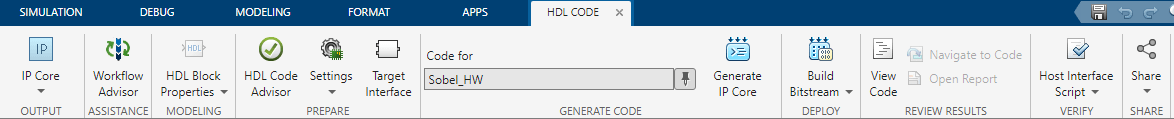

[アプリ] タブで、[HDL Coder] をクリックします。[HDL コード] タブの [出力] セクションで、ドロップダウン ボタンが [IP コア] に設定されていることを確認します。

この例のテスト対象デバイス (DUT) である

Sobel_HWサブシステムを選択します。[次のコード] がこのサブシステムに設定されていることを確認します。選択内容を記憶しておくために、ピン ボタン をクリックできます。

をクリックできます。

[設定] をクリックし、[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成]、[ターゲット] ペインを開きます。

[ターゲット プラットフォーム] パラメーターを

ZedBoardに設定します。このオプションが表示されていない場合は、[Get more] を選択してサポート パッケージ インストーラーを開きます。サポート パッケージ インストーラーで、[AMD FPGA and SoC Devices] を選択し、手順に従ってインストールを完了します。[合成ツール] がXilinx Vivadoに設定されていることを確認します。[リファレンス設計] パラメーターが

Default video system (requires HDMI FMC module)に設定されていることを確認します。[OK] をクリックして、更新した設定を保存します。

設計およびターゲット インターフェイスの構成

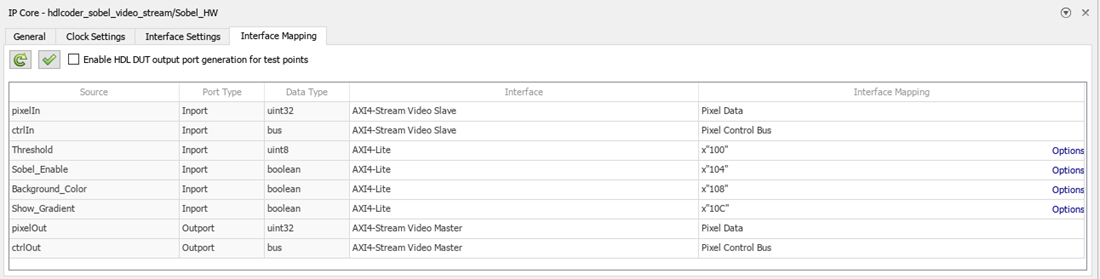

DUT 端子を IP コア ターゲット ハードウェアにマッピングし、DUT レベルの IP コア オプションを設定することで、ターゲット ハードウェアにマッピングするように設計を構成します。この例では、AXI4-Stream Video インターフェイスはマスター/スレーブ モードで通信します。このモードでは、マスター デバイスがデータをスレーブ デバイスに送信します。したがって、入力データ端子は AXI4-Stream Video Slave インターフェイスにマッピングされ、出力データ端子は AXI4-Stream Video Master インターフェイスにマッピングされます。

Simulink で、[HDL コード] タブの [ターゲット インターフェイス] をクリックして IP コア エディターを開きます。

[Interface Mapping] タブを選択して、各 DUT 端子を IP コアのターゲット インターフェイスのいずれかにマッピングします。マッピング テーブルが表示されない場合は、IP コア設定を再読み込みする

ボタンをクリックし、モデルをコンパイルして DUT 端子およびそのデータ型を再び取り込みます。

ボタンをクリックし、モデルをコンパイルして DUT 端子およびそのデータ型を再び取り込みます。pixelIn、ctrlIn、pixelOut、およびctrlOutの各端子を AXI4-Stream Video インターフェイスにマッピングします。Threshold端子などの制御パラメーター端子を AXI4-Lite インターフェイスにマッピングします。DUT 端子が、下のイメージで示されているインターフェイスにマッピングされていることを確認します。

IP コア設定を検証する

ボタンをクリックして、設定を検証します。

ボタンをクリックして、設定を検証します。

必要に応じて、IP コア エディターで以下を行うことによって、ターゲット ハードウェアの DUT レベルの IP コア設定を調整できます。

[General] タブを使用して、IP コアの名前や IP コア レポートを生成するかどうかなど、最上位の設定を構成する。

[Clock Settings] タブを使用してクロック関連の設定を構成する。

[Interface Settings] タブを使用して、レジスタ インターフェイスや FPGA Data Capture のプロパティなど、インターフェイス関連の設定を構成する。

IP コアを生成

次に、IP コアを生成します。Simulink ツールストリップの [HDL コード] タブで [IP コアを生成] をクリックします。

IP コアを生成すると、コード生成レポートも生成されます。[コード生成レポート] ウィンドウの左側のペインで、[IP コアの生成レポート] をクリックします。このレポートには、IP コアのレジスタ アドレス マッピングなど、生成されたカスタム IP コアの動作と内容が記載されています。

AXI4-Stream Video 互換のリファレンス設計への IP の統合

R2023b 以降

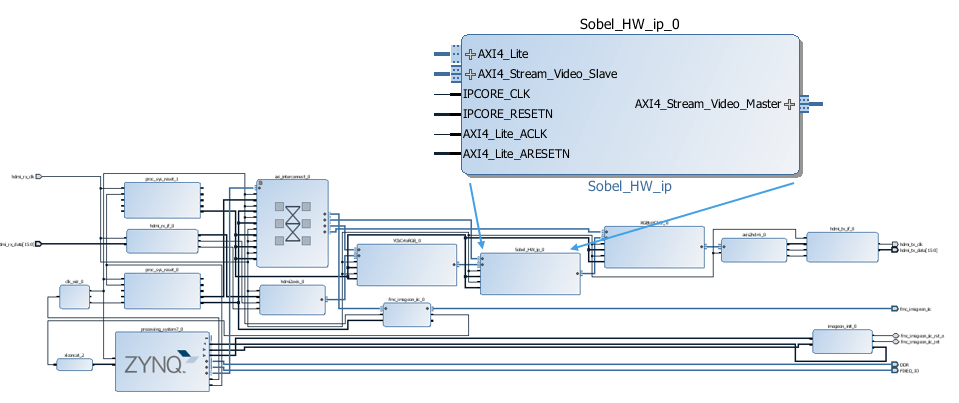

次に、プロジェクトを作成し、FPGA ビットストリームを生成し、ビットストリームを Zynq ハードウェアにダウンロードすることで、生成された IP コアを組み込みシステム リファレンス設計に挿入します。

リファレンス設計は事前定義の Xilinx Vivado プロジェクトです。このプロジェクトには、カスタム IP コアと組み込みソフトウェアを除く、Xilinx ソフトウェアで設計を Zynq プラットフォームに展開するために必要なすべての要素が含まれています。この例では Simulink ツールストリップの [HDL コード] タブを使用して IP コアを展開して検証します。HDL ワークフロー アドバイザーを使用して IP コアを展開して検証する方法の詳細については、Comparison of IP Core Deployment and Verification Techniquesを参照してください。

IP コア プロジェクトの作成

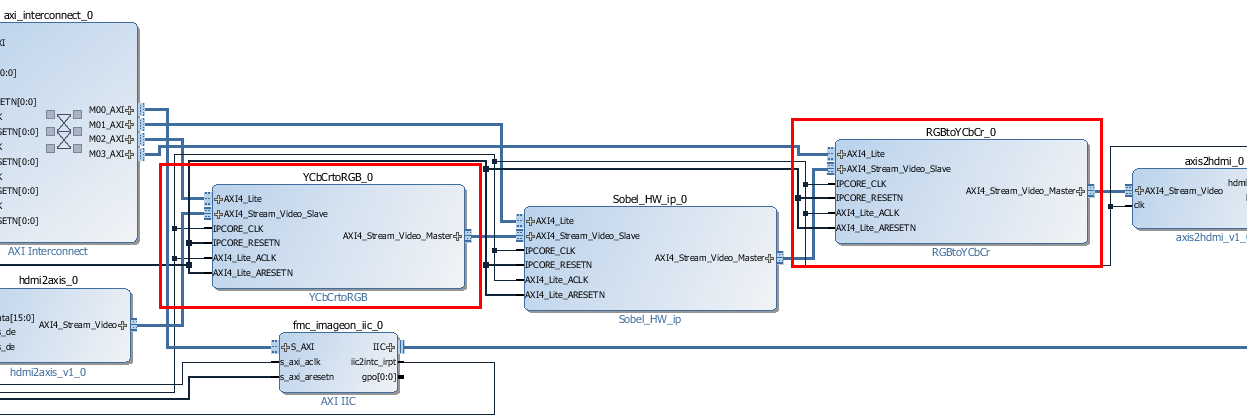

IP コアに関連付けられているファイルを整理して維持する Vivado プロジェクトを作成して、生成された IP コアを Xilinx プラットフォームに統合します。Vivado プロジェクトを作成するには、Simulink ツールストリップの [HDL コード] タブで [ビットストリームの作成]、[IP コア プロジェクトの作成] を選択します。HDL Coder により、IP インテグレーター組み込み設計が生成され、診断ビューアーにその設計へのリンクが表示されます。

Simulink 診断ビューアーのリンクをクリックして、生成された Vivado プロジェクトを開きます。Vivado ツールで、[Open Block Design] をクリックして Zynq 設計図を表示します。これには、生成された HDL IP コア、その他のビデオ パイプライン IP、および Zynq プロセッサが含まれます。このイメージに表示されているように、このリファレンス設計には、以下を処理する IP が含まれています。

HDMI 入出力インターフェイス

YCbCr から RGB への色空間変換

生成されたプロジェクトは完全な Zynq 設計であり、生成された DUT アルゴリズムの IP とリファレンス設計が含まれます。

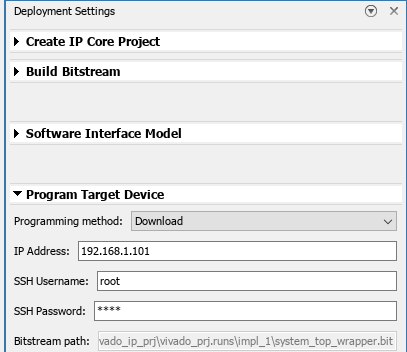

展開設定の構成

次に、ビットストリームの作成の設定を構成します。Simulink ツールストリップの [HDL コード] タブで [ビットストリームの作成]、[展開の設定] を選択します。[展開の設定] ウィンドウの [ビットストリームの作成] セクションで [ビルド プロセスを外部で実行] を選択して、現在の MATLAB セッションではなく別のウィンドウで Xilinx 合成ツールを実行します。

次に、[ターゲット デバイスをプログラム] セクションで以下のようにします。

[プログラミング メソッド] を

Downloadに設定して、Zynq ボードの電源をオフ/オンしたときに、FPGA ビットストリームをターゲット Zynq ボード上の SD カードにダウンロードして設計が自動的に再読み込みされるようにします。[IP アドレス] をターゲット ボードの IP アドレスに設定します。

[SSH ユーザー名] および [SSH パスワード] をターゲット ボードの構成に設定します。

ビットストリームの生成およびターゲット デバイスのプログラム

ビットストリーム ファイルを生成するには、Simulink ツールストリップの [HDL コード] タブで [ビットストリームの作成] をクリックし、合成ツールが外部ウィンドウで実行されるまで待機します。

ビットストリームをダウンロードするには、[HDL コード] タブで [ビットストリームの作成]、[ターゲット デバイスをプログラム] を選択します。

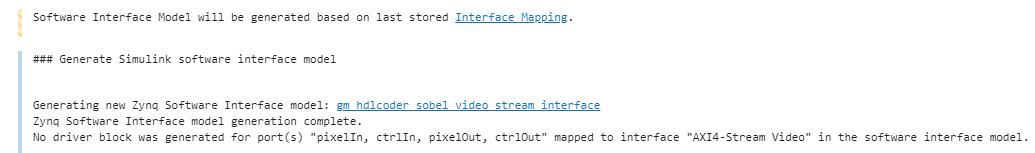

ソフトウェア インターフェイス モデルを使用したプロセッサへの展開

ARM プロセッサの設計の一部をターゲットにするには、ソフトウェア インターフェイス モデルを生成します。ソフトウェア インターフェイス モデルには、設計内のソフトウェアで実行される部分が含まれます。これには HDL サブシステムの外側にあるすべてのブロックが含まれており、HDL サブシステムは AXI ドライバー ブロックに置き換えられます。Embedded Coder ライセンスを保有している場合は、ソフトウェア インターフェイス モデルから組み込みコードを自動的に生成してビルドし、ARM プロセッサ上の Linux で実行可能ファイルを実行できます。生成された組み込みソフトウェアは、AXI ドライバー ブロックから AXI ドライバー コードを生成し、そのコードを使用して HDL Coder で生成された IP コアを制御します。ソフトウェア インターフェイス モデルは、IP コア生成および IP コア統合プロセスのどの段階でも生成できます。

ソフトウェア インターフェイス モデルを生成するには、Simulink ツールストリップの [HDL コード] タブで [ビットストリームの作成]、[ソフトウェア インターフェイス モデル] を選択します。Simulink 診断ビューアーに、生成されたソフトウェア インターフェイス モデルへのリンクが表示されます。

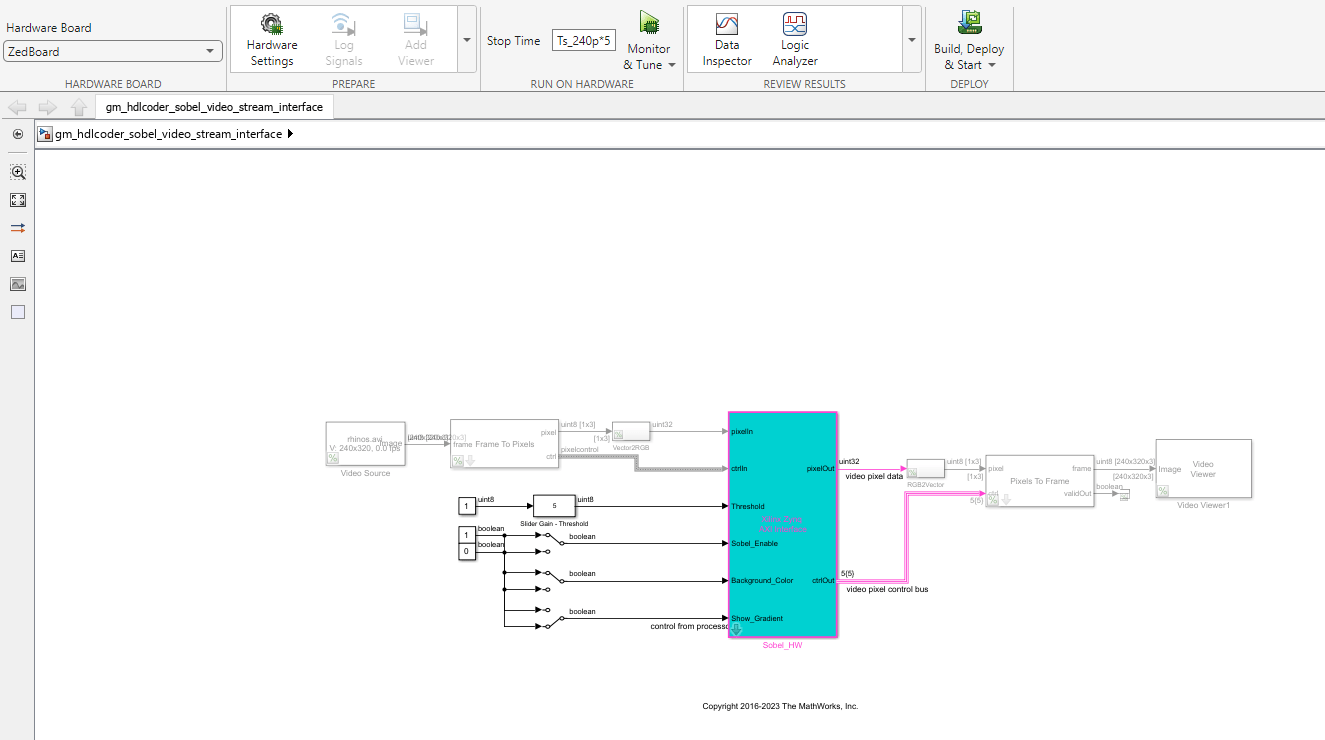

ソフトウェア インターフェイス モデルからコードを生成する前に、次の図に示すように、生成されたモデルで Video Source と Video Viewer をコメント アウトします。これらのブロックは ARM プロセッサで実行する必要はありません。ARM プロセッサは AXI4-Lite インターフェイスを使用して FPGA ファブリックを制御するため、実際のビデオ ソースと表示インターフェイスは FPGA ファブリックで実行されます。ビデオ ソースは HDMI 入力から取得され、ビデオ出力は HDMI 出力に接続されているモニターに送信されます。

ZedBoard ハードウェアでのソフトウェア インターフェイス モデルの実行

次に、生成されたソフトウェア インターフェイス モデルを構成し、組み込み C コードを生成し、エクスターナル モードを使用して Zynq ハードウェア上の ARM プロセッサでモデルを実行します。

アルゴリズムのプロトタイピングおよび開発を行う場合は、アルゴリズムをハードウェアで実行しながらアルゴリズムを監視および調整すると便利です。エクスターナル モードを使用して、アルゴリズムを Zynq ハードウェアの ARM プロセッサに展開してから、イーサネット接続を介してホスト コンピューター上の Simulink モデルにアルゴリズムをリンクできます。

生成されたモデルで、[ハードウェア] タブの [準備] セクションにある [ハードウェア設定] をクリックして、[コンフィギュレーション パラメーター] ダイアログ ボックスを開きます。

[ハードウェアで実行] セクションで [終了時間] を

infに設定します。[OK] をクリックします。[ハードウェア] タブの [ハードウェアで実行] セクションで [監視と調整] をクリックします。Embedded Coder は、モデルを構築し、ARM 実行可能ファイルを Zynq ハードウェアにダウンロードして、これを実行し、モデルを Zynq ハードウェアで実行しているこの実行可能ファイルに接続します。

[Sobel_Enable] 端子への入力スイッチを使用して、ライブ ビデオ出力がエッジ検出器出力と元のビデオの間で切り替わることを確認します。[Threshold] 端子または [Background_Color] 端子へのスイッチ入力を使用して、ライブ ビデオ出力に対するエッジ検出のさまざまな影響を確認します。モデルは、エクスターナル モードと AXI4-Lite インターフェイスを介して Zynq ハードウェアにパラメーター値を送信します。

モデル パラメーターの変更が終わったら、Simulink ツールストリップの [停止] ボタンをクリックし、システム コマンド ウィンドウを閉じます。

ビデオ リファレンス設計のカスタマイズ

既存の Default video system リファレンス設計を拡張して前処理または後処理カメラ パイプライン IP をさらに追加したり、別の SoC ハードウェアまたはビデオ カメラ インターフェイスを使用したりするとします。Default Video System リファレンス設計は、独自のカスタム リファレンス設計を作成する開始点として使用できます。

たとえば、Default video system リファレンス設計には、次の図に示すように、YCbCr から RGB への色空間変換を行う 2 つの IP コアが含まれています。これらの 2 つの IP コアは、IP コアの生成時に HDL Coder によって生成されます。他の前処理または後処理カメラ パイプライン IP コアを生成してカスタム リファレンス設計に追加し、ビデオ プラットフォームを拡張できます。

独自のカスタム リファレンス設計の作成の詳細については、AMD ワークフロー用のカスタムのボードとリファレンス設計の定義の例を参照してください。