HDL Coder によるテスト ポイント信号のモデル化およびデバッグ

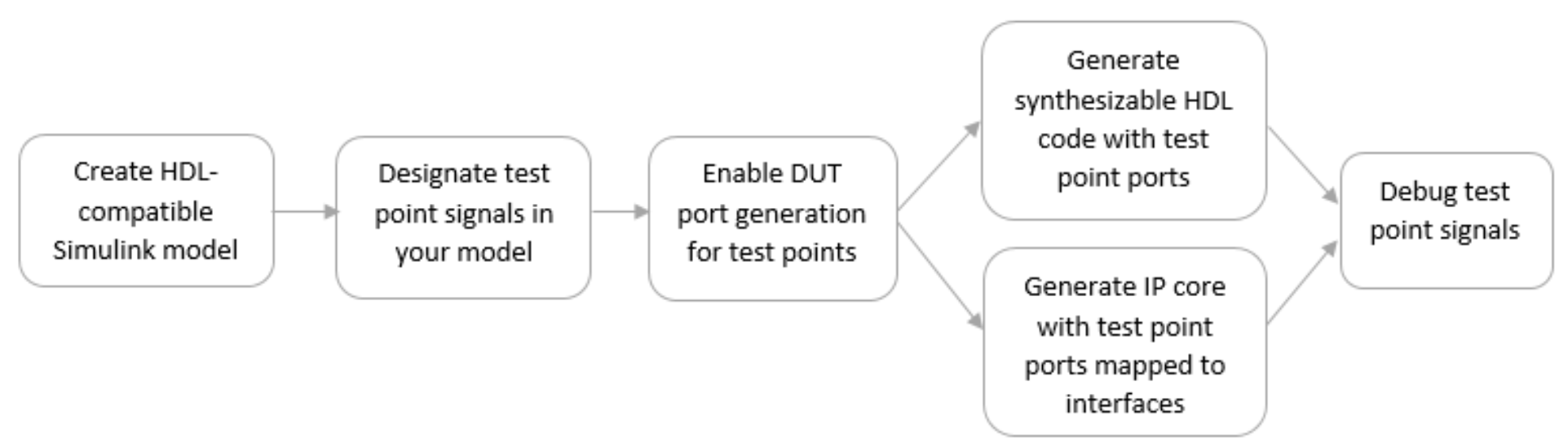

この例では、Simulink® モデルで信号をテスト ポイントとしてマークする方法と、HDL コード生成後に、生成されたモデルまたはテスト ベンチを使用して最上位レベルで信号をデバッグする方法を説明します。

テスト ポイントを使用する理由

テスト ポイントは、Simulink モデルのさまざまなポイントにおけるシミュレーション結果を簡単にデバッグおよび観察するために使用できる信号です。テスト ポイントとして指定された信号は、モデル内の Floating Scope ブロックで観察できます。Simulink では、モデル内の任意の信号をテスト ポイントとして指定できます。

コード生成後、DUT 出力端子でテスト ポイント信号を観察し、下流のワークフローにおいて生成コードをデバッグできます。この機能を利用することで、コード ジェネレーターは、サブシステム階層の深いレベルから DUT 出力端子にテスト ポイント信号を伝播できるため、設計を容易にデバッグできるようになります。

HDL Coder によるテスト ポイント信号のモデル化およびデバッグ

HDL 互換モデルの作成

信号をテスト ポイントとして指定し、HDL コードを生成する前に、作成したモデルが HDL コード生成との互換性があるか確認します。HDL 互換 Simulink モデルの作成を参照してください。

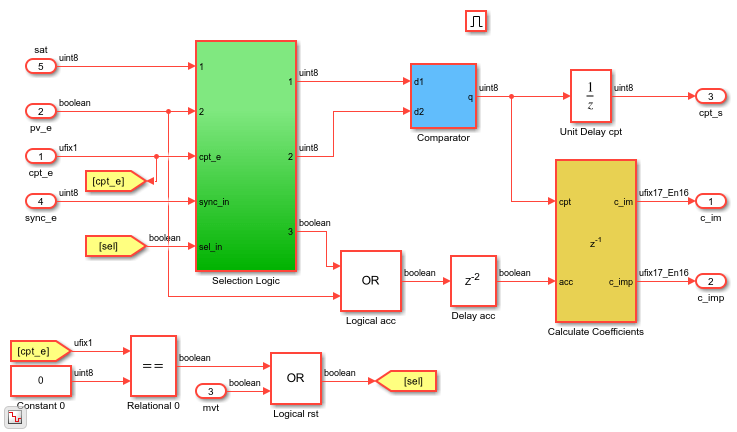

この例では、HDL コード生成用に準備された hdlcoder_test_points モデルを開きます。DUT は、Selection Logic と Comparator からの入力に基づいて 2 つの係数を計算する Enabled Subsystem です。

load_system('hdlcoder_test_points') open_system('hdlcoder_test_points/DUT/MaJ Counter') set_param('hdlcoder_test_points', 'SimulationCommand', 'update');

信号をテスト ポイントとして指定

このモデルで内部信号をデバッグするには、次のいずれかの方法でこれらをテスト ポイントとしてマークします。

Simulink エディターで、[信号プロパティ] ダイアログ ボックスを開くには、信号を右クリックして [プロパティ] を選択します。次に、[テスト ポイント] を選択します。

コマンド ラインで、ブロックの出力端子へのハンドルを取得し、端子パラメーター

TestPointをonに設定します。

たとえば、以下のコマンドを入力して、OR 演算を行う Logical acc ブロックからの出力信号をテスト ポイントとして指定します。

portHandles = get_param('hdlcoder_test_points/DUT/MaJ Counter/Logical acc', 'portHandles'); outportHandle = portHandles.Outport; set_param(outportHandle,'TestPoint','on');

ブロックに複数の出力端子がある場合は、テスト ポイントとして指定する出力ハンドルを指定します。たとえば、Demux ブロックの 2 番目の出力をテスト ポイントとして指定するには、以下のコマンドを入力します。

set_param(outportHandle(2),'TestPoint','on');

[テスト ポイント] の設定を有効にした各信号について、Simulink にインジケーターが表示されます。モデルをナビゲートすると、3 つの追加のテスト ポイントが表示されます。これらのテスト ポイントは、Selection Logic Subsystem ブロック、Comparator Subsystem ブロック、および Calculate Coefficients Subsystem ブロックの中にあります。

詳細については、テスト ポイントとしての信号の設定を参照してください。

テスト ポイントの DUT 出力端子生成の有効化

HDL コード生成前、テスト ポイントとして指定した信号をデバッグするには、信号の HDL DUT 端子生成を有効にします。モデル コードを生成すると、HDL Coder™ により、これらの信号は追加の出力端子として DUT に伝播されます。

hdlcoder_simulink_test_points モデルで DUT 出力端子生成を有効にするには、次を実行します。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成]、[グローバル設定]、[端子] タブで、[テスト ポイントの HDL DUT 端子生成を有効にする] を選択します。

コマンド ラインで

EnableTestpointsプロパティを使用します。

hdlset_param('hdlcoder_test_points','EnableTestpoints','on')

このパラメーターの詳細については、Enable HDL DUT output port generation for test pointsを参照してください。

テスト ポイントの DUT 出力端子の生成を有効にすると、[コンフィギュレーション パラメーター] ダイアログ ボックスを使用して [生成された DUT 出力端子の遅延の均衡化] を無効にするか、コマンド ラインを使用して BalanceDelaysForTestpoints を off に設定することで、生成された DUT 出力端子の遅延の均衡化を無効にすることができます。このパラメーターの詳細については、生成された DUT 出力端子の遅延の均衡化を参照してください。

手動で追加した出力端子をテスト ポイントとして扱い、DUT レベルの Outport ブロックで HDL ブロック プロパティ [BalanceDelays] を無効にすることもできます。

DUT 端子生成を有効にした後、以下のワークフローのいずれかを実行できます。

HDL コードを生成します。コードをターゲットの FPGA に展開するには、HDL ワークフロー アドバイザーで

Generic ASIC/FPGAワークフローを使用します。テスト ポイント端子をターゲット プラットフォーム インターフェイスにマッピングし、合成ツールとして

Xilinx VivadoまたはAltera Quartus IIを使用するIP Core GenerationワークフローまたはSimulink Real-Time FPGA I/Oワークフローを使用して、HDL IP コアを生成します。

HDL コード生成と FPGA ターゲット

HDL コード内のテスト ポイント端子とモデル内のテスト ポイント信号間のマッピングを表示する場合は、コード生成レポートの生成を有効にします。このレポートには、Simulink モデル内の対応するテスト ポイント信号へのリンクをもつテスト ポイント端子が表示されます。

たとえば、hdlcoder_simulink_test_points モデルに対してレポート生成を有効にするには、次のようにします。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] ペインで [リソース利用レポートを生成] を選択します。

この設定をコマンド ラインで指定するには、

ResourceReportプロパティを使用します。

hdlset_param('hdlcoder_test_points','ResourceReport','on')

レポート生成の詳細については、コード生成レポートの作成と使用を参照してください。

HDL コードを生成するには、次のようにします。

DUTサブシステムを右クリックします。コンテキスト メニューに HDL Coder アプリのオプションを追加するには、[アプリの選択] をポイントし、[HDL Coder] をクリックします。次に、HDL Coder アプリのセクションで [サブシステムに対する HDL を生成] を選択します。コマンド ラインで、DUT サブシステムに対して

makehdlを実行します。

コードをターゲット プラットフォームに展開するには、Generic ASIC/FPGA ワークフローを使用します。HDL ワークフロー アドバイザーの [ターゲット デバイスおよび合成ツールを設定] タスクで、[ターゲット ワークフロー] に [Generic ASIC/FPGA] を選択し、[合成ツール] を指定してから、ワークフローを実行します。

コードが生成されると、HDL Coder でコード生成レポートが開きます。[コード インターフェイス レポート] セクションには、Output Ports セクション内のテスト ポイントへのリンクが含まれます。

テスト ポイント端子のリンクをクリックすると、コード ジェネレーターにより、Simulink モデルでテスト ポイントとして指定した、該当する信号が強調表示されます。そのため、このレポートを利用して、生成されたコードのテスト ポイント端子から、Simulink モデル内のテスト ポイント信号に逆トレースできます。

生成された HDL コードでテスト ポイント端子を確認するには、DUT.v ファイルを開きます。

最上位のモジュール宣言内で、テスト ポイント端子を確認できます。これらの端子には、接頭辞 tp_ と、テスト ポイント端子に対応することを示すコメントが付けられています。ターゲット言語として VHDL® を指定した場合、テスト ポイント端子はエンティティ宣言内で確認できます。

IP コアの生成と SoC ターゲット

HDL IP コアを生成するには、HDL ワークフロー アドバイザーを開きます。アドバイザーで、以下を実行します。

[ターゲット デバイスおよび合成ツールを設定] タスクで、[ターゲット ワーフロー] に対して [

IP Core Generation] を選択し、合成ツールとしてXilinx VivadoまたはAltera Quartus IIを使用する [ターゲット プラットフォーム] を指定します。Simulink Real-Time FPGA I/Oワークフローを使用する場合は、合成ツールとしてXilinx Vivadoを使用する [ターゲット プラットフォーム] を指定します。[ターゲットのリファレンス設計を設定] タスクで、HDL Coder の既定のリファレンス設計、または HDL IP コアを統合するカスタム リファレンス設計を指定します。テスト ポイント信号に一意の名前を指定しない場合、このタスクの実行は失敗する可能性があります。このエラーを修正するには、[結果] サブペインで、リンクを選択してテスト ポイント信号の一意の名前を生成します。タスクが成功したことを確認するには、タスクを再実行します。

[ターゲット インターフェイスを設定] タスクで、[テスト ポイントの HDL DUT 端子生成を有効にする] チェックボックスをオンにしてテスト ポイントの HDL DUT 端子生成を有効にすると、[ターゲット プラットフォーム インターフェイス テーブル] にテスト ポイント端子が表示されます。端子を AXI4、AXI4-Lite、または External Port インターフェイスにマッピングできます。このタスクを実行した後、コード ジェネレーターはこのテスト ポイント インターフェイス マッピング情報を DUT に保存します。この情報を表示するには、DUT サブシステムの [HDL ブロック プロパティ] にある [ターゲット仕様] タブで TestPointMapping ブロック プロパティを探します。ワークフローの以降の実行で DUT のこの情報を再読み込みできます。

[RTL コードと IP コアの生成] タスクで、[選択したタスクまで実行] を選択し、IP コアを生成します。コード ジェネレーターでは、テスト ポイント端子のインターフェイスへのマッピングを表示する IP コアの生成レポートが開きます。

テスト ポイント端子のリンクをクリックすると、コード ジェネレーターにより、Simulink モデルでテスト ポイントとして指定した、該当する信号が強調表示されます。

生成された HDL ソース ファイルを開くと、IP コア ラッパーに接続されているテスト ポイント信号が表示されます。

ワークフローを実行してソフトウェア インターフェイス モデルを生成し、[ターゲットのリファレンス設計を設定] タスクで指定したターゲットのリファレンス設計を IP コアに統合します。

IP Core Generation ワークフローの詳細については、カスタム IP コアの生成およびカスタム IP コア レポートを参照してください。

テスト ポイント信号のデバッグ

HDL コードを生成した後、または IP コアを生成した後に、テスト ポイント信号をデバッグできます。

モデル用に HDL コードを生成した場合、または Generic ASIC/FPGA ワークフローを実行した場合、テスト ポイント信号をデバッグするには、HDL テスト ベンチを生成するか、生成したモデルを使用します。生成されたモデルを開くには、コマンド ラインで「gm_hdlcoder_test_points」と入力します。

生成されたモデルでは、コメント アウトされた Scope ブロックに接続された DUT 出力端子でテスト ポイントを確認できます。これらの信号のシミュレーション結果を観察するには、Scope ブロックのコメントを解除してからシミュレーションを実行します。生成されたモデルを見てみると、信号をテスト ポイントとして指定したポイントで、コード ジェネレーターが出力端子を生成していることが分かります。これらの端子は、追加の出力端子として HDL Coder によって DUT に伝播されます。

[ソフトウェア インターフェイス モデルを生成] タスクに対して IP Core Generation ワークフローを実行すると、コード ジェネレーターはソフトウェア インターフェイス モデルを開きます。

ARM® プロセッサからテスト ポイント信号上のデータを観察するには、Scope ブロックのコメントを解除してから、ソフトウェア インターフェイス モデルを実行します。

考慮事項

テスト ポイント端子は、コード生成プロセスの他の出力端子と同様と見なされます。テスト ポイント端子の生成は、リソース共有、ストリーミング、分散型パイプライン方式などすべての最適化と連携します。各種最適化の詳細については、速度と面積の最適化を参照してください。

検証モデルを生成すると、コード ジェネレーターでテスト ポイント信号と、出力の時点でテスト ポイント端子が比較されないことが分かります。Scope ブロックをコメント解除し、シミュレーションを実行して、テスト ポイント信号を観察することもできます。生成されたモデルと検証モデルの詳細については、生成されたモデルと検証モデルを参照してください。

コシミュレーション モデルを生成すると、テスト ポイント端子が Terminator ブロックに接続されていることが分かります。テスト ポイントを観察するには、Terminator ブロックを削除し、出力端子を Scope ブロックに接続してから、コシミュレーションを実行します。また、コシミュレーションを実行する HDL シミュレーターで波形を観察することもできます。コシミュレーションの詳細については、コシミュレーション モデルの生成を参照してください。

生成されたモデルを開くと、パフォーマンスを考慮して Scope ブロックがコメント アウトされています。

DUT テスト ポイント端子では、端子の順序は指定できません。コードを生成するときに、HDL Coder によって端子の順序が決まります。

[ターゲット ワークフロー] は、

Generic ASIC/FPGA、IP Core GenerationまたはSimulink Real-Time FPGA I/Oでなければなりません。IP Core GenerationワークフローまたはSimulink Real-Time FPGA I/Oワークフローを使用する場合、[合成ツール] はXilinx VivadoまたはAltera Quartus IIでなければなりません。Xilinx ISEはサポートされません。IP Core GenerationワークフローまたはSimulink Real-Time FPGA I/Oワークフローを使用する場合、テスト ポイント端子を AXI4、AXI4-Lite、または External Port インターフェイスにマッピングできます。端子は AXI4-Stream インターフェイスまたは AXI4-Stream Video インターフェイスにマッピングできません。IP コア ワークフローでテスト ポイントまたは調整可能なパラメーターを使用する場合、DUT は、最上位モデルやモデル参照の DUT ではなく、サブシステム レベルの DUT でなければなりません。