カスタム IP コア レポート

既定では、カスタム IP コアの生成時に HTML カスタム IP コア レポートが生成されます。このレポートには、生成されたカスタム IP コアの動作と内容が記載されています。

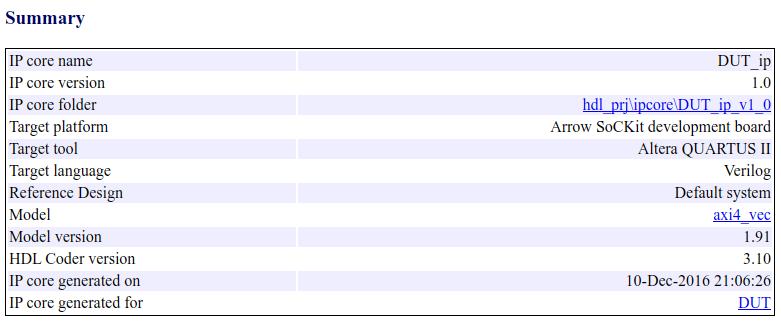

概要

[概要] セクションには、カスタム IP コアの生成時点での設定が表示されます。

次の図は [概要] セクションの例を示しています。

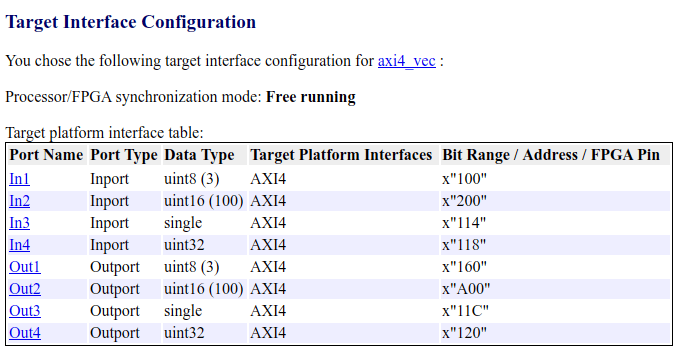

Target Interface Configuration

[Target Interface Configuration] セクションでは、DUT 端子のターゲット ハードウェア インターフェイスへのマッピング方法と、プロセッサ/FPGA 同期モードを示しています。

次の図は [Target Interface Configuration] セクションの例を示しています。

プロセッサ/FPGA 同期モードの詳細は、プロセッサと FPGA の同期を参照してください。

ターゲット プラットフォーム インターフェイスの詳細は、カスタム IP コアの生成を参照してください。

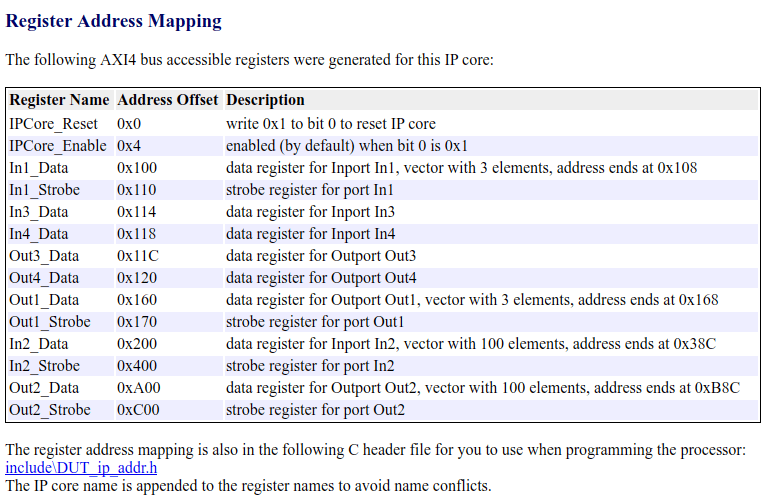

Register Address Mapping

[Register Address Mapping] セクションには、カスタム IP コアにある AXI4-Lite バスにアクセス可能なレジスタのアドレス オフセット、および同じアドレス オフセットがある C ヘッダー ファイルの名前が表示されます。

次の図は [Register Address Mapping] セクションの例を示しています。

Bit Packing Order

[Bit Packing Order] セクションには、内部 IO インターフェイス、外部 IO インターフェイスおよび外部端子インターフェイスのベクトル入力とベクトル出力に関するデータ パック順序の概要が含まれます。このセクションは、内部 IO、外部 IO および外部端子の端子幅が 128 ビット幅より大きい値に設定されている場合にのみ表示されます。

次の図は [Bit Packing Order] セクションの例を示しています。

IP Core User Guide

[IP Core User Guide] セクションには、システム アーキテクチャの概要、プロセッサと FPGA の同期モードの説明、組み込みシステム統合環境に IP コアを統合する手順が含まれます。

次の図は IP コア ユーザー ガイド システム アーキテクチャの説明の例です。

テスト対象設計 (DUT) にレジスタが含まれている場合、HDL Coder™ は IP コアの生成レポートに次のセクションを追加します。

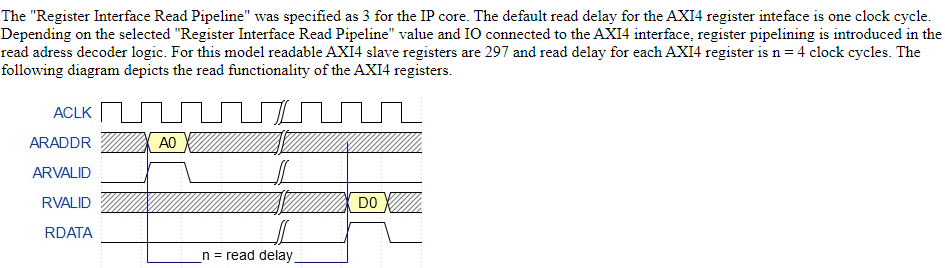

次の図は、プロセッサ/FPGA の同期の説明の例です。

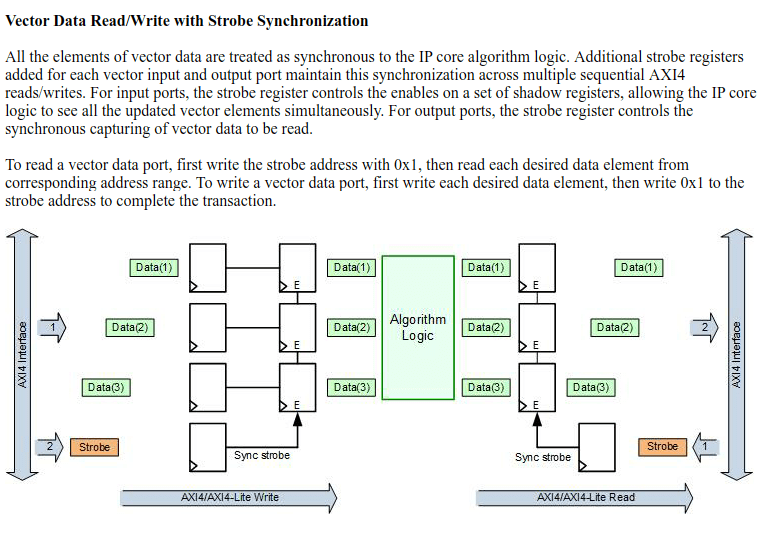

DUT インターフェイスでベクトル データ信号を使用する場合は、コード ジェネレーターが AXI4 インターフェイス間でベクトル データを同期する方法を示すこのセクションが IP コア レポートに表示されます。

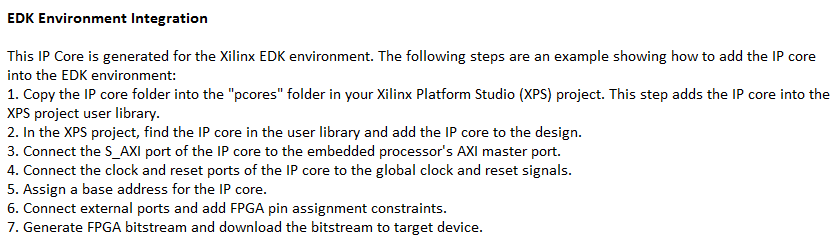

次の図は、Xilinx® プラットフォームの組み込みシステム統合環境で IP コアを統合する手順の例です。Altera® プラットフォームをターゲットにする場合、IP コアを Altera Qsys 環境に統合する類似の手順がレポートに表示されます。

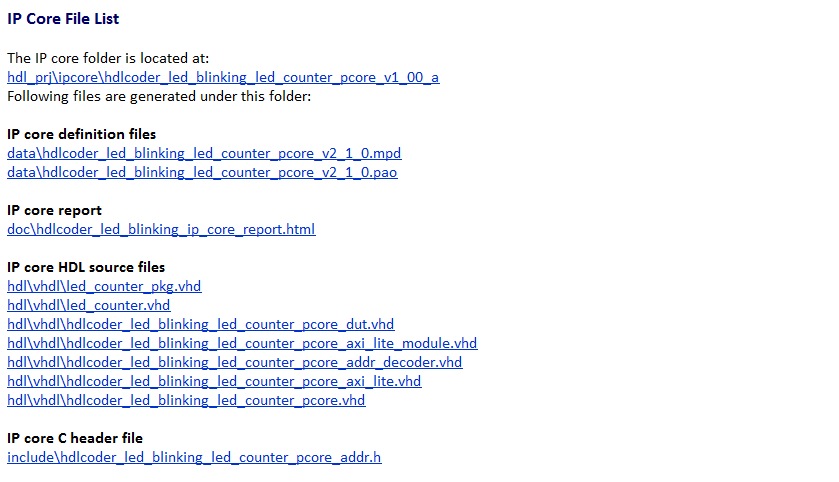

IP Core File List

[IP Core File List] セクションには、カスタム IP コアを構成するファイルとファイル フォルダーの一覧が表示されます。

次の図は IP コア ファイル リストの例です。