プロセッサと FPGA の同期

HDL ワークフロー アドバイザーでは、組み込みシステム統合プロジェクトで使用するカスタム IP コアを生成する場合にプロセッサと FPGA に対して [プロセッサ/FPGA 同期] モードを選択できます。以下の同期モードを使用できます。

フリー ラン(既定の設定)コプロセッシング - ブロックコプロセッシング – 遅延ノンブロック

フリー ラン モード

フリー ラン モードでは、プロセッサと FPGA はそれぞれが非同期で、継続的に、並行して実行されます。

プロセッサと FPGA が自動的に同期しないようにするには、[プロセッサ/FPGA 同期] モードとして [フリー ラン] を選択します。

次の図は、プロセッサと FPGA がフリー ラン モードで通信する方法を説明しています。影付きの部分は、プロセッサと FPGA が継続的に実行されていることを表します。

[コプロセッシング - ブロック] モード

HDL Coder™ のブロック コプロセッサ モードでは、プロセッサと FPGA が連携して実行されるための FPGA の同期ロジックを自動的に生成します。

プロセッサのサンプル時間よりも FPGA の実行時間が短く、プロセッサの続行前に FPGA を完了する必要がある場合は、[プロセッサ/FPGA 同期] モードとして [コプロセッシング – ブロック] を選択します。

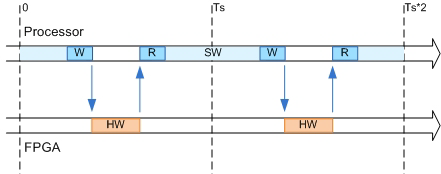

次の図は、プロセッサと FPGA がブロック コプロセッシング モードで動作する方法を説明しています。

影付きの部分は、プロセッサと FPGA が実行されていることを表します。プロセッサはサンプル時間ごとに FPGA に書き込みを行い、その後停止して、FPGA が処理を完了するまで待機してから引き続き処理を続行します。FPGA が実行されるたびに、生成されたロジックを DUT サブシステムの 1 サンプル時間の間実行します。