コード生成レポートの作成と使用

レポート コンフィギュレーション パラメーターの少なくとも 1 つが有効になっている Simulink® モデルから HDL コードを生成すると、HDL Coder™ によって HTML コード生成レポートが生成および表示されます。レポートには、生成されたコードに関する次のような情報が含まれます。

リソース使用量の推定

タイミング推定

HDL Coder 最適化の影響

コードを Simulink ブロックまでトレースするリンク

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [レポート] 設定のモデル コンフィギュレーション パラメーターを使用して、コード生成レポートをカスタマイズします。

レポートの生成

下表では、コード生成レポートに追加できるセクションをリストします。既定では、HDL Coder により、[概要]、[クロック概要]、および [コード インターフェイス レポート] の各セクションが生成されます。

| レポートのセクション | 説明 | コンフィギュレーション パラメーター | 依存関係 |

|---|---|---|---|

| 概要 | モデル、テスト対象設計 (DUT)、コード生成日、および既定以外の HDL Coder 設定に関する情報が含まれます。 | [コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [レポート] セクションのパラメーターの少なくとも 1 つを有効にします。 | [HDL コード生成] 、 [グローバル設定] の設定で [HDL コードを生成] を有効にします。 |

| クロック概要 | 以下に関する情報が含まれます。

レポートには、モデル内のクロック数に基づいた次のような情報も表示されます。

詳細については、HDL Coder での複数のクロックの使用を参照してください。 | ||

| コード インターフェイス レポート | DUT への入力端子と出力端子の名前、データ型、ビット長がリストされます。レポートには、Simulink モデル内の各入力端子および出力端子へのリンクが表示されます。 |

タイミングおよび面積レポート

| レポートのセクション | 説明 | コンフィギュレーション パラメーター | 依存関係 |

|---|---|---|---|

| 高水準リソース レポート | DUT が消費する加算器、減算器、乗算器、レジスタ、およびその他のリソースの概要が示されます。 | リソース利用レポートを生成 | [HDL コード生成] 、 [グローバル設定] の設定で [HDL コードを生成] を有効にします。 |

| ターゲット固有のレポート | FPGA 浮動小数点ライブラリ マッピングを使用してターゲット固有のコードを生成した場合にリソース利用レポートが表示されます。 |

| |

| ネイティブ浮動小数点リソース レポート | Simulink ブロックのマッピング先の浮動小数点演算子がリストされます。 |

| |

| クリティカル パスの推定 | クリティカル パスとそのパスに沿った伝播遅延が推定されます。このセクションでは、DUT が実行可能な最大周波数が推定されます。 | 高位のタイミング クリティカル パス レポートを生成 |

|

最適化レポート

| レポートのセクション | 説明 | コンフィギュレーション パラメーター | 依存関係 |

|---|---|---|---|

| 遅延の均衡化 | 以下に関する詳細情報が示されます。

詳細については、遅延の均衡化レポートを参照してください。 | 最適化レポートを生成 |

|

| 階層のフラット化 | 階層のフラット化のステータス、[FlattenHierarchy] が [on] または [off] に設定されているサブシステム、およびインラインの HDL ファイルが表示されます。詳細については、階層のフラット化のレポートを参照してください。 | ||

| コードの再利用 | HDL Coder が生成されたサブシステム コードを再利用した場所の概要が示されます。 | ||

| ターゲット コード生成 | 生成されたコードで浮動小数点型が使用されている場合に、ターゲット デバイスの概要とターゲット マッピング ステータスが表示されます。 | ||

| ストリーミングおよび共有 | 共有またはストリーミングを指定したサブシステムに関する情報の概要が示されます。詳細については、ストリーミング レポートおよびリソース共有レポートを参照してください。 | ||

| クロック レート パイプライン | モデルでクロックレート パイプラインがどのように実行されたかの詳細が示されます。詳細については、クロックレート パイプライン レポートを参照してください。 | ||

| 分散型パイプライン方式 | 分散型パイプライン方式の変換を適用する前後のレジスタを比較するリストが表示されます。詳細については、分散型パイプライン方式のレポートを参照してください。 | ||

| 適応パイプライン | 適応パイプライン最適化のステータス、パイプライン レジスタが挿入されたブロック、およびパイプライン レジスタの数が表示されます。詳細については、適応パイプライン レポートを参照してください。 | ||

| フレームからサンプルへ | 以下に関する情報が含まれます。

|

トレーサビリティ レポートとモデルの Web ビュー

| レポートのセクション | 説明 | コンフィギュレーション パラメーター | 依存関係 |

|---|---|---|---|

| トレーサビリティ レポート | 可能な場合、生成されたコードの行から Simulink モデル内の対応するブロックへのリンクが示されます。このレポートでは、Simulink のコード ビューを使用してコードとモデルの間をトレースできます。詳細については、トレーサビリティを使用した Simulink モデルと HDL コード間の移動を参照してください。 | トレーサビリティ レポートの生成 | [HDL コード生成] 、 [グローバル設定] の設定で [HDL コードを生成] を有効にします。 |

| モデルの Web ビュー | HTML コード生成レポートで Simulink モデルが表示されます。モデルの Web ビューには Simulink Report Generator™ が必要です。詳細については、Generate Web View of Model in Code Generation Reportを参照してください。 | モデルの Web ビューを生成 | [HDL コード生成] 、 [グローバル設定] の設定で [HDL コードを生成] を有効にします。 |

あるいは、次の表に記載されているプロパティを on または off に設定することで、コード生成レポートをプログラムによってカスタマイズすることもできます。このプロパティを設定するには、hdlset_paramまたはmakehdlを使用します。

| レポートのセクション | makehdl プロパティ | 依存関係 |

|---|---|---|

| 高水準リソース レポート | ResourceReport | GenerateHDLCode を on に設定します。 |

| ターゲット固有のレポート | GenerateHDLCode を on に設定し、FloatingPointTargetConfiguration をベンダー固有の浮動小数点ライブラリに設定します。 | |

| ネイティブ浮動小数点リソース レポート | GenerateHDLCode および UseFloatingPoint を on に設定します。 | |

| クリティカル パスの推定 | CriticalPathEstimation | GenerateHDLCode および GenerateModel を on に設定します。 |

| 遅延の均衡化 | OptimizationReport | GenerateHDLCode および GenerateModel を on に設定します。 |

| 階層のフラット化 | ||

| コードの再利用 | ||

| ターゲット コード生成 | ||

| ストリーミングおよび共有 | ||

| クロック レート パイプライン | ||

| 分散型パイプライン方式 | ||

| 適応パイプライン | ||

| フレームからサンプルへ | ||

| トレーサビリティ レポート | Traceability | GenerateHDLCode を on に設定します。 |

| モデルの Web ビュー | HDLGenerateWebView | GenerateHDLCode を on に設定します。 |

コード生成レポートの操作

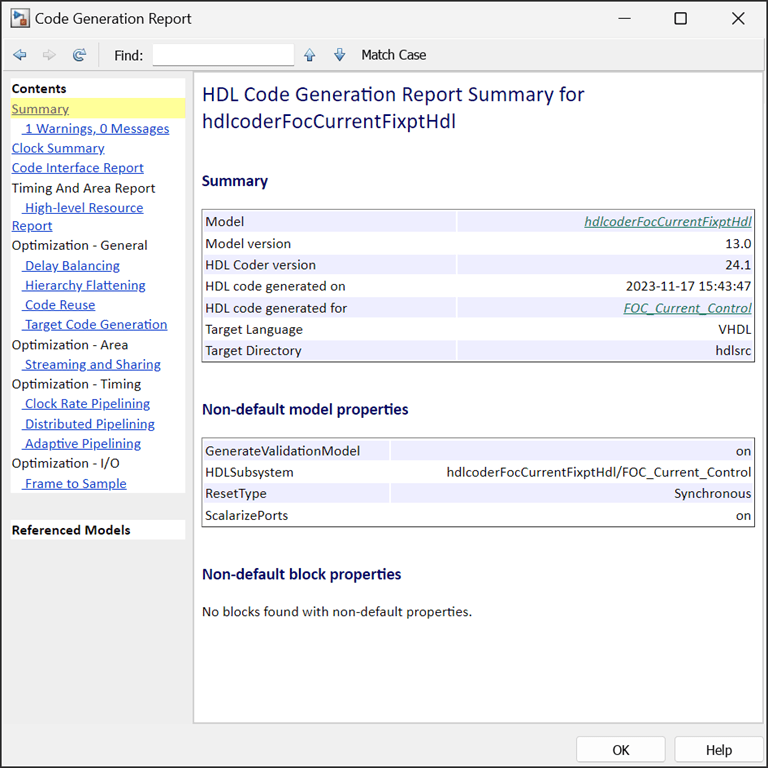

Simulink モデルからコード生成レポートに移動できます。たとえば、モデル hdlcoderFocCurrentFixptHdl.slx のコード生成レポートを生成して表示するには、MATLAB® コマンド ラインで次のコマンドを使用してモデルを開きます。

openExample('hdlcoder/ClockRatePipeliningExample','supportingFile','hdlcoderFocCurrentFixptHdl.slx')

このモデルでは、[リソース利用レポートを生成] コンフィギュレーション パラメーターと [最適化レポートを生成] コンフィギュレーション パラメーターが有効になっています。FOC_Current_Control サブシステムの HDL コードを生成するには、次を入力します。

makehdl('hdlcoderFocCurrentFixptHdl/FOC_Current_Control')コードの生成後に、レポートが自動的に開きます。また、MATLAB コマンド ウィンドウで hdlcoderFoxCurrentFixptHdl_codegen_rpt.html へのリンクをクリックするか、[HDL Coder] アプリで [レポートを開く] を選択することで、手動で開くこともできます。

モデルのコード生成レポート hdlcoderFoxCurrentFixptHdl_codegen_rpt.html には以下が含まれています。

レポートの各種セクションへのリンクを含む [コンテンツ] ペイン。

生成コードのリソース使用量を示す [高水準リソース レポート] セクション。

HDL Coder によって適用されるクロックレート パイプライン、分散型パイプライン方式、およびその他の最適化に関する追加のセクション。

レポートをナビゲートするには、[コンテンツ] ペインで対応するリンクをクリックして各種セクションを参照します。

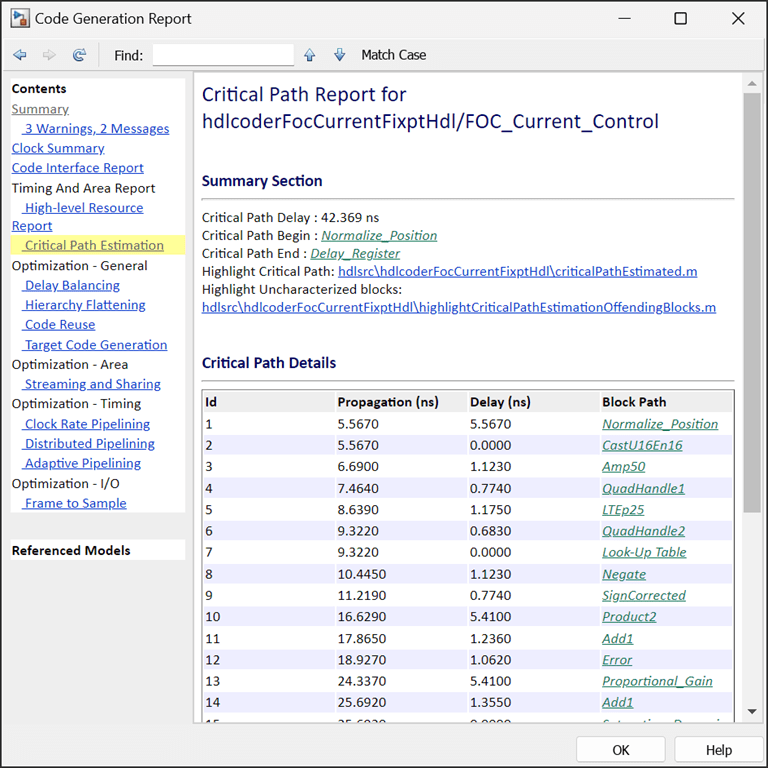

必要なセクションのみを含めるようにレポートをカスタマイズできます。たとえば、[クリティカル パスの推定] セクションを追加するには、CriticalPathEstimation プロパティを有効にして次のように入力します。

makehdl('hdlcoderFocCurrentFixptHdl/FOC_Current_Control', 'CriticalPathEstimation', 'on')

hdlcoderFocCurrentFixptHdl.slx のコード生成レポートが生成されます。

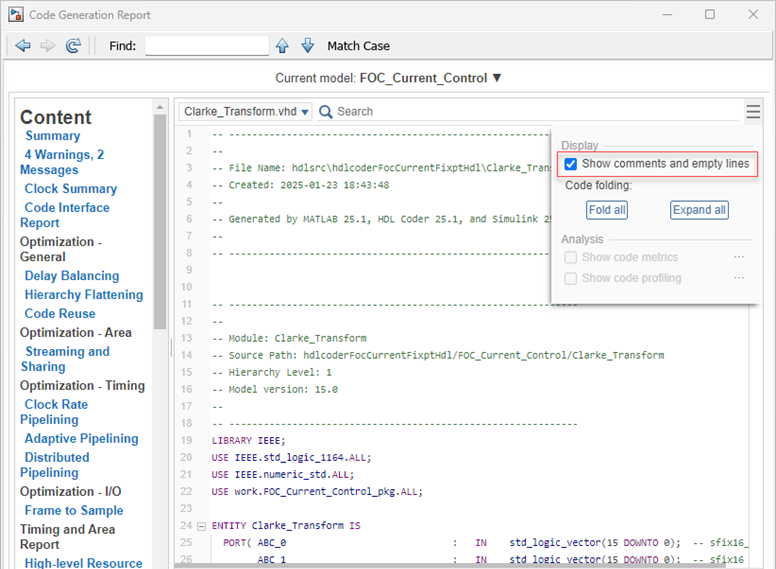

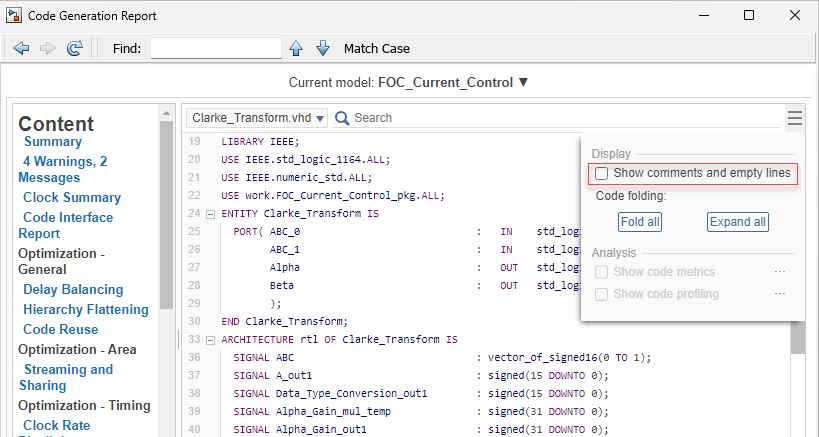

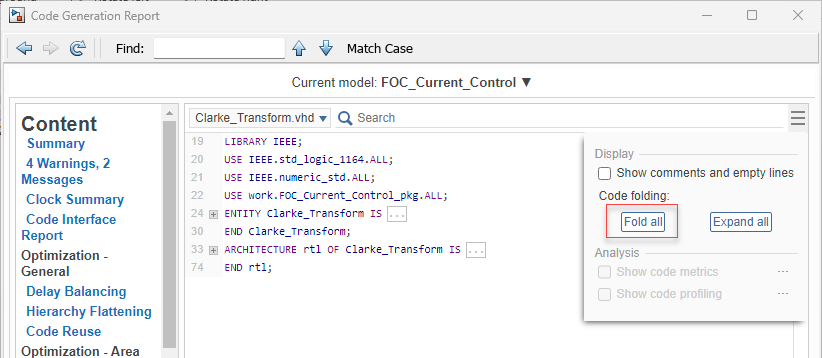

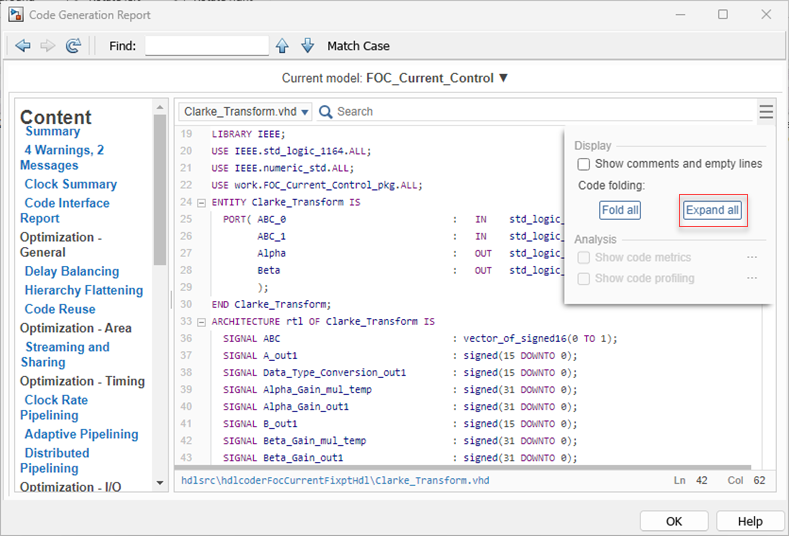

[コンフィギュレーション パラメーター] ボタン  を使用して、レポートにおける生成コードの外観をカスタマイズすることもできます。[表示] ペインで以下のフィルターを適用できます。

を使用して、レポートにおける生成コードの外観をカスタマイズすることもできます。[表示] ペインで以下のフィルターを適用できます。

コメントと空の行を生成コードに含めるには、[コメントと空の行を表示] パラメーターを選択します。コードに含まれるコメントと空の行がレポートに表示されます。

コメントと空の行を生成コードから除外するには、[コメントと空の行を表示] パラメーターをクリアします。コメントと空の行がレポートで非表示になります。

生成コード内のすべてのコード セクションを折りたたむには、[すべて折りたたむ] ボタンをクリックします。すべてのコード セクションが折りたたまれた状態でレポートに表示されます。

生成コード内のすべてのコード セクションを展開するには、[すべて展開する] ボタンをクリックします。すべてのコード セクションが展開されてレポートに表示されます。

コード生成レポートを使用した合成前のコードの評価

[リソース利用レポートを生成] または [高位のタイミング クリティカル パス レポートを生成] パラメーターを選択すると、HDL Coder により、コード生成レポートに [タイミングおよび面積レポート] セクションが追加されます。タイミングおよび面積レポートを使用して、生成されたコードがハードウェアで必要とされる周波数とリソースで実行できるかどうかを評価できます。

生成されたコードの面積の評価

高水準リソース レポートの [概要] セクションでは、次の使用量が推定されます。

乗算器

加算器と減算器

1 ビット レジスタ

RAM

マルチプレクサー

I/O ビット

静的シフト演算子

動的シフト演算子

リソース レポートを使用して、生成された HDL コードのリソース使用量の推定値を追跡して削減します。

[高水準リソース レポート] セクションには、次のセクションも含まれています。

[レジスタ] セクションには、1 ビット レジスタの合計が表示されます。合計は、レジスタのビット幅とその発生頻度の積の和です。

[静的シフト演算子] セクションと [動的シフト演算子] セクション。静的シフトは、マスク定数であるシフト値です。シフト ロジックは変わりません。動的シフトは、ブロックへの入力として指定されるシフト値です。動的シフトは静的シフトよりもリソース使用量が大きくなります。

レポート内のリソース使用量がハードウェアで利用可能な量を超えている場合は、DUT にリソース共有やストリーミングなどの面積の最適化を適用することを検討してください。リソース共有とストリーミングは、面積を削減する共有ハードウェア リソースを使用するように生成コードを最適化します。詳細については、Area Optimizationsを参照してください。

生成されたコードのタイミングの評価

[クリティカル パスの推定] セクションには、モデル内でタイミング遅延が最長の連結パスの推定が含まれます。HDL Coder はターゲット固有のタイミング データベースを使用して、生成されたコードのクリティカル パスを推定します。HDL Coder にターゲット コンフィギュレーション用のタイミング データベースがない場合は、関数genhdltdbを使用してターゲット固有のタイミング データベースを生成します。詳細については、合成実行なしのクリティカル パスの推定を参照してください。

クリティカル パスの伝播遅延により、生成されたコードがターゲット上で実行できる周波数が制限されます。クリティカル パス推定の推定遅延が長すぎて、DUT がターゲット周波数で実行できない場合は、推定クリティカル パスの最適化を検討してください。クリティカル パスの推定では、生成されたモデル内のクリティカル パスを強調表示する criticalPathEstimated スクリプトへのリンクが示されます。このスクリプトを使用して、生成されたモデル内の推定クリティカル パスを特定し、元の Simulink モデルに遅延を追加してクリティカル パスを分割します。

さらに、HDL Coder 最適化により、クリティカル パスのタイミングを最適化し、DUT の最大周波数を高めることができます。詳細については、Balance Pipeline Delays and Design Delaysを参照してください。

最適化の影響の評価

報告されたタイミングまたは面積の使用量が要件を満たしていない場合は、合成前に元のモデルを最適化してそのモデルからコードを再度生成できます。コードを生成した後、最適化レポートを使用して、HDL Coder によって DUT がどのように最適化されたか、また特定の最適化が適用されなかった理由を把握します。最適化レポートを使用して、最適化の障害を特定し、DUT のタイミングと面積を改善します。