適応パイプライン設定の指定

ブロックとレジスタの特定のパターンまたは組み合わせにより、達成可能なクロック周波数を向上し、FPGA ボード上の使用面積を削減できます。適応パイプライン最適化は、設計内のブロックにパイプライン レジスタを挿入することによって、これらのパターンを作成します。最適化では、ターゲット デバイス、ターゲット周波数、乗算器の語長、[HDL ブロック プロパティ] の設定を考慮して、設計に挿入するパイプライン レジスタの最適な数を決定します。適応パイプラインは次と併用します。

クロックレート パイプラインとの併用により、低速データレートではなく、高速クロックレートでのパイプライン レジスタを挿入する。クロックレート パイプラインでは、DUT をあるレートで設計した後に、[Simulink のレートを実際のハードウェアのレートとして扱う] パラメーターまたは [オーバーサンプリング係数] パラメーターのいずれかを使用して設計のオーバーサンプリング値を指定できます。これらのパラメーターの詳細については、Simulink のレートを実際のハードウェアのレートとして扱うおよびオーバーサンプリング係数を参照してください。

リソース共有による面積とタイミングの節約。コード ジェネレーターはリソースを共有し、適応パイプライン レジスタを挿入するため。

既定では、適応パイプライン最適化はモデルで無効になっています。場合によっては、HDL コードを生成する前にこの最適化を有効にしなければなりません。適応パイプラインが必要な設計パターンを参照してください。

要件

HDL Coder™ で適応パイプラインを挿入するには、ターゲット デバイスを指定します。設計に乗算器が含まれる場合、ターゲット デバイスとターゲット周波数を指定します。

メモ

適応パイプライン用に特徴付けられていないターゲット デバイスを使用する場合、最適化では、[合成ツール] に

[Xilinx Vivado]が指定されている場合は Xilinx® Virtex®-7 を使用し、[合成ツール] が[Altera Quartus II]または[Intel Quartus Pro]の場合は Intel® Stratix® V を使用します。HDL Coder で適応パイプラインを挿入するサブシステムに対して遅延の均衡化が有効になっていることを確認します。遅延の均衡化を無効にすると、コード ジェネレーターは適応パイプラインを挿入しません。

設計に浮動小数点のデータ型や演算が含まれていないことを確認してください。

メモ

場合によって、フィードバック ループ内にブロックが存在する際、必要な数のパイプライン レジスタを適応パイプラインが出力に挿入できないことがあります。このとき、遅延の均衡化が失敗することがあります。

適応パイプラインの指定

適応パイプラインは、モデル全体に設定することも、より詳細に制御するために最上位 DUT サブシステム内のサブシステムに設定することもできます。

モデルの適応パイプラインの有効化

既定では、適応パイプラインはモデル レベルで無効になっています。適応パイプラインを有効にするには、次のいずれかの手順に従います。

HDL ワークフロー アドバイザーの[HDL コード生成] 、 [コード生成オプションを設定] 、 [最適化オプションを設定] 、 [パイプライン] タブで、[適応パイプライン] を選択します。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [最適化] 、 [パイプライン] タブで、[適応パイプライン] を選択して [OK] をクリックします。

コマンド ラインで関数

makehdlまたはhdlset_paramを使用して、適応パイプラインをonに設定します。hdlset_param(gcs, 'AdaptivePipelining', 'on')

サブシステムに対する適応パイプラインの有効化

既定では、モデル内のサブシステムは、モデルレベルの適応パイプライン設定を継承します。モデル内のあるサブシステムについて、HDL Coder が選択的に適応パイプラインを有効化するには、そのサブシステムの [AdaptivePipelining] を [on] にします。

サブシステムの適応パイプラインの設定方法については、サブシステムに対する適応パイプラインの設定を参照してください。

サポートされているブロック

適応パイプラインは、パイプラインの自動挿入について、乗算器、積和、レート変換の次のブロックをサポートしています。

Product

Gain

Multiply-Add

Multiply-Accumulate

MATLAB Function

Product ブロックと Gain ブロックのパイプライン挿入

これらのブロックに適応パイプラインを挿入するには、以下のようにします。

ターゲット デバイスを指定します。

ターゲット周波数に 0 より大きい値を指定します。

コード生成時、HDL Coder は、ブロックの入力端子と出力端子にレジスタを挿入します。乗算器とレジスタの組み合わせは、ターゲット デバイス上の DSP ユニットにマッピングされる可能性があります。

この図は、ターゲット FPGA デバイスとして Intel Arria10 を使用し、ターゲット周波数を 500 MHz としたときに、Product ブロックおよび Gain ブロックに対して生成されたモデルを示します。各ブロックへの入力の型は int16 です。

HDL Coder が挿入するパイプライン レジスタのパターンと数は、ターゲット デバイス、ターゲット周波数、乗算器の語長によって異なります。

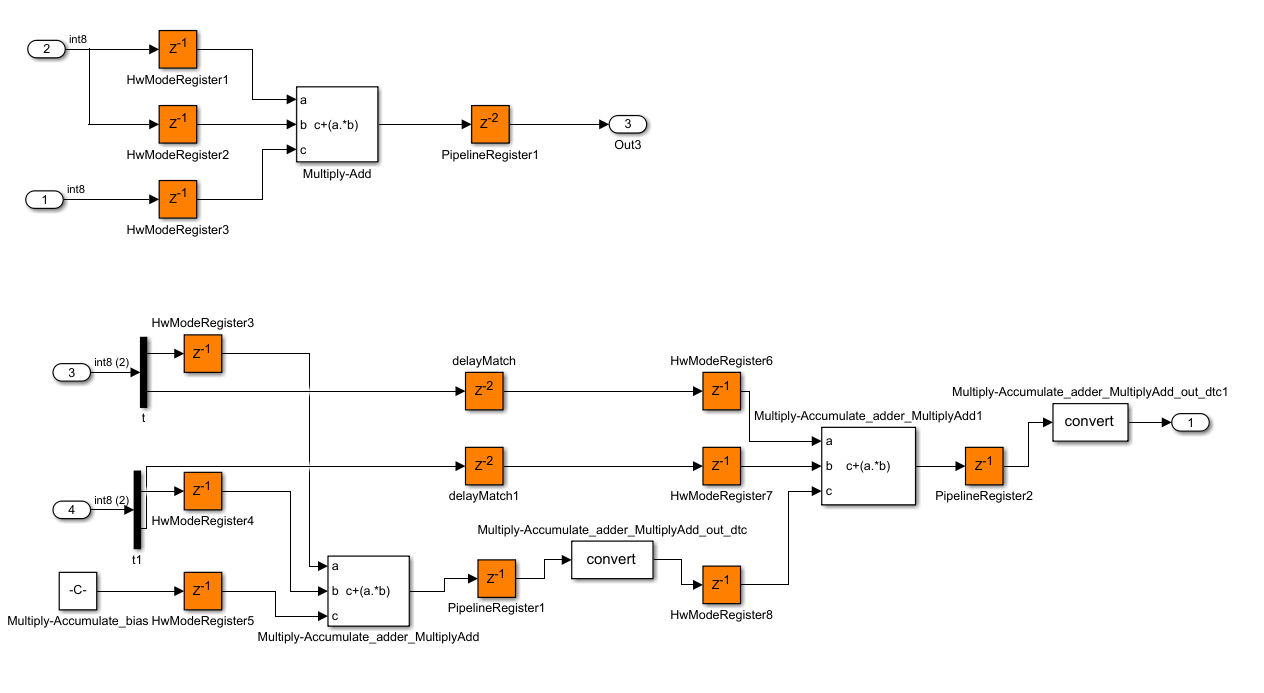

この図は、ターゲット FPGA デバイスとして Xilinx Virtex7 を使用し、ターゲット周波数を 1500 MHz としたときに、これらのブロックに対して生成されたモデルを示します。入力の型は int8 です。

ブロックにより、出力端子のパイプライン レジスタの数は異なります。遅延を一致させるため、HDL Coder は、Product ブロックと Gain ブロックの出力に遅延を追加します。

Multiply-Add ブロックと Multiply-Accumulate ブロックのパイプライン挿入

これらのブロックに適応パイプラインを挿入するには、以下のようにします。

ターゲット デバイスを指定します。

ターゲット周波数に 0 より大きい値を指定します。

Multiply-Accumulate ブロックに対して

ParallelHDL アーキテクチャを使用します。サイズNの入力ベクトルでは、このアーキテクチャは結果を計算するためにN個の Multiply-Add ブロックを直列で使用します。

注意

[PipelineDepth] が auto またはゼロより大きい値に設定された Multiply-Add ブロックと、HDL アーキテクチャが Parallel として指定された Multiply-Accumulate ブロックは、適応パイプライン設定を無視します。ターゲット FPGA デバイスとゼロより大きいターゲット周波数を指定した場合、適応パイプラインが無効になっているときでも、コード ジェネレーターはブロックの入出力でパイプライン レジスタを挿入します。

コード生成時、HDL Coder は、ブロックの入力端子と出力端子にレジスタを挿入します。ブロックとレジスタの組み合わせは、ターゲット デバイス上の DSP ユニットにマッピングされる可能性があります。

この図は、ターゲット FPGA デバイスとして Intel Arria10 を使用し、ターゲット周波数を 500 MHz としたときに、Multiply-Add と Multiply-Accumulate に対して生成されたモデルを示します。各ブロックへの入力の型は int8 です。

HDL Coder が挿入するパイプライン レジスタのパターンと数は、ターゲット デバイス、ターゲット周波数、乗算器の語長によって異なります。

この図は、ターゲット FPGA デバイスとして Xilinx Virtex7 を使用し、ターゲット周波数を 1500 MHz としたときに、これらのブロックに対して生成されたモデルを示します。入力の型は int16 です。

MATLAB Function ブロックのパイプライン挿入

MATLAB Function ブロックに適応パイプラインを挿入するには、以下のようにします。

ターゲット デバイスを指定します。

ターゲット周波数に 0 より大きい値を指定します。

MATLAB Function ブロックの HDL アーキテクチャを

MATLAB Datapathに設定します。

HDL Coder は、アーキテクチャが MATLAB Datapath に設定されている MATLAB Function ブロックを通常のサブシステムと同様に扱います。コード ジェネレーターは MATLAB® アルゴリズムを Simulink® ブロック線図に変換します。Simulink ブロック線図が、適応パイプラインでサポートされている Product または Add といったブロックを使用する場合、コード ジェネレーターはブロックの入出力端子にパイプライン レジスタを挿入します。乗算器とレジスタの組み合わせは、ターゲット デバイス上の DSP ユニットにマッピングされる可能性があります。

MATLAB Datapath アーキテクチャを使用する MATLAB Function ブロックについて考えます。このコードは MATLAB Function ブロック内のアルゴリズムです。

function y = fcn(u)

y = u*5;この図は、ターゲット FPGA デバイスとして Intel Arria10 を使用し、ターゲット周波数が 500 MHz である MATLAB Function ブロックに対して生成されたモデルを示します。各ブロックへの入力の型は int16 です。コード ジェネレーターは、定数の乗算としてアルゴリズムを推定し、入出力で適応パイプラインを挿入しました。

MATLAB Function ブロックでの HDL アプリケーションを参照してください。

適応パイプライン レポート

適応パイプライン情報をレポートで見るには、各サブシステムまたはモデル参照のコードを生成する前に、コード生成レポートを有効にします。[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] ペインで [最適化レポートを生成] を選択します。

HDL コードを生成する場合、コード生成が完了するとコード生成レポートが開きます。最適化レポートの [適応パイプライン] セクションを選択します。

適応パイプライン レポートに、適応パイプライン最適化のステータスと、設計に適応パイプラインが挿入されたかどうかが表示されます。

適応パイプラインを有効化して HDL コードを生成すると、次のレポートが表示されます。

パイプライン レジスタを挿入したブロック。設計のブロック内に挿入されたパイプライン レジスタを確認するには、ブロックへのリンクをクリックしてください。

挿入されたパイプライン レジスタの数。

追加メモ。

適応パイプラインが完了しない場合は、失敗の原因となった基準。

参考

AdaptivePipelining | クロックレート パイプライン | Balance delays