このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

適応パイプラインが必要な設計パターン

ブロックとレジスタの特定のパターンまたは組み合わせにより、達成可能なクロック周波数を向上し、FPGA 上の使用面積を削減できます。適応パイプライン最適化は、設計内のブロックにパイプライン レジスタを挿入することによって、これらのパターンを作成します。最適化では、ターゲット デバイス、ターゲット周波数、乗算器の語長、[HDL ブロック プロパティ] の設定を考慮して、設計に挿入するパイプライン レジスタの最適な数を決定します。適応パイプライン設定の指定を参照してください。

既定では、適応パイプライン最適化はモデルで無効になっています。この最適化を使用する場合は、有効にしなければなりません。

多くの場合、適応パイプライン最適化を有効にしなくても、モデルでパイプラインを選択的に挿入して効率的な HDL コードを生成できます。たとえば、乗算器の横にパイプラインを選択的に追加できます。

特定の設計パターンでは、コードを生成する前に適応パイプライン最適化を有効にしなければなりません。たとえば、Discrete-Time Integrator ブロックの内部ロジックにパイプラインを選択的に追加できない場合があります。

適応パイプラインを有効にするかどうかのガイドラインは次のとおりです。

R2021a より前のリリースでは、コード ジェネレーターによって適応パイプラインが挿入されるとモデルの適応パイプライン レポートに表示されていました。そのモデルのコードを生成するときは適応パイプラインを有効にします。

適応パイプライン最適化でサポートされるブロックをモデルで使用しており、それらのブロックのパイプライン レジスタを選択的に挿入していない場合は、適応パイプラインを有効にします。

適応パイプライン最適化でサポートされるブロックをモデルで使用しており、次のいずれかの最適化を有効にする場合は、適応パイプラインも有効にします。

リソース共有

ストリーミング

クロックレート パイプライン。

適応パイプライン レポートおよびサポートされているブロックを参照してください。

例ローパス、バンドパス、ハイパス フィルターを使用するオーディオ システムおよびリソース共有を使用する離散 FIR フィルターは、コードを生成する前に適応パイプラインを有効にしなければならないいくつかの状況を示しています。

ローパス、バンドパス、ハイパス フィルターを使用するオーディオ システム

Zynq ボードへのオーディオ フィルターの実装を参照してください。

この例のモデルでは、適応パイプラインが有効になっています。適応パイプラインを無効にすると、生成された HDL コードがタイミング制約を満たさなくなります。

リソース共有を使用する離散 FIR フィルター

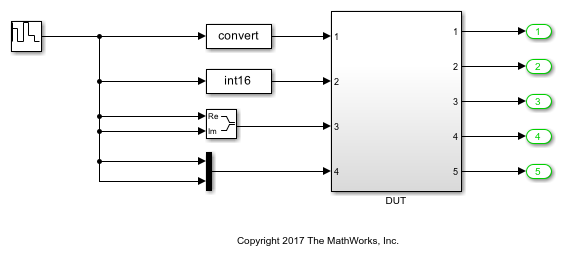

離散 FIR フィルターのモデルを開いて確認します。

DUT Subsystem ブロックで、HDL ブロック プロパティ [SharingFactor] が 8 に設定されています。したがって、このサブシステムではリソース共有最適化を使用しています。

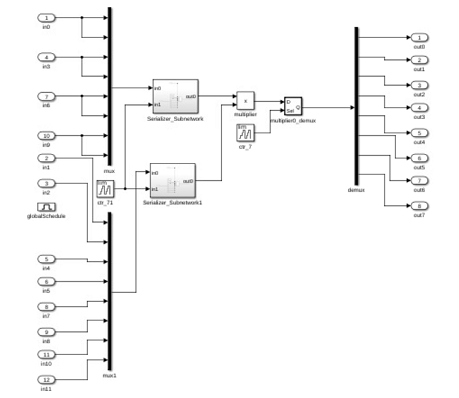

適応パイプラインを無効にしたコードの生成

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成]、[最適化]、[パイプライン] タブで、[適応パイプライン] をオフにします。

HDL ワークフロー アドバイザーで、[ターゲット周波数 (MHz)] を 200、[合成ツール] を Xilinx Vivado に設定します。HDL コードを生成し、FPGA 合成を実行します。コード生成と合成の手順の詳細については、Simulink モデルからの HDL コード生成と FPGA 合成を参照してください。

生成されたモデルでは、適応パイプラインは挿入されていません。

合成結果に、タイミング制約を満たしていないことを示す負のスラックが示されます。

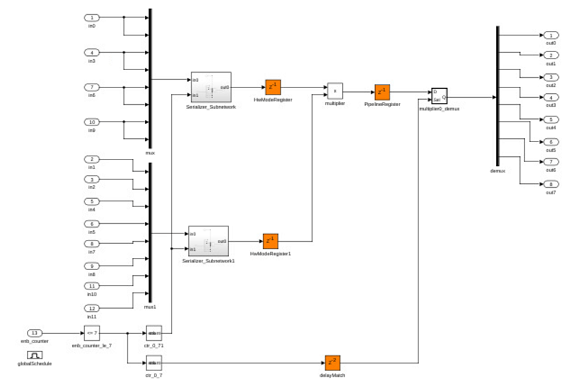

適応パイプラインを有効にしたコードの生成

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成]、[最適化]、[パイプライン] タブで、[適応パイプライン] を選択します。前と同じように、HDL コードを生成し、FPGA 合成を実行します。

生成されたモデルを確認すると、コード ジェネレーターによって乗算器ブロックに対して適応パイプラインが挿入されていることがわかります。

合成結果に、タイミング制約を満たしていることを示す正のスラックが示されます。

参考

適応パイプライン設定の指定 | リソース共有 | ストリーミング