Simulink モデルからの HDL コード生成と FPGA 合成

この例では、簡単なカウンター モデルのコードを生成し、生成されたコードを Simulink® HDL ワークフロー アドバイザーを使用して Xilinx® FPGA で合成します。このモデルを作成するには、HDL 互換 Simulink モデルの作成を参照してください。

HDL ワークフロー アドバイザーは Simulink Online™ では使用できません。

Simulink HDL ワークフロー アドバイザー

HDL ワークフロー アドバイザーは、次のような Simulink サブシステムの HDL コードの生成と FPGA 設計プロセスをサポートします。

モデルに HDL コード生成との互換性があるか確認し、非互換設定を自動的に修正。

HDL コード、テスト ベンチ、コードとテスト ベンチをビルドして実行するスクリプトの生成。

コシミュレーションまたは SystemVerilog DPI テスト ベンチ、コード カバレッジの生成 (HDL Verifier™ が必要)。

サードパーティ製の合成ツールとの統合による合成とタイミング解析。

合成時に取得したクリティカル パスなどの情報によるモデルのバックアノテーション。

選択した FPGA 開発ターゲット デバイスと Simulink Real-Time™ FPGA I/O ワークフローに対する、FPGA インザループ シミュレーションを含む完全な自動ワークフロー。

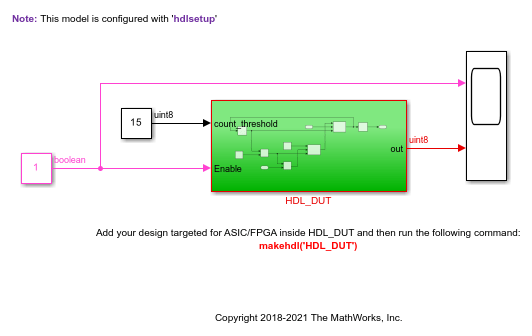

簡単なカウンター モデル

このモデルはゼロからしきい値である 15 までカウントし、ゼロに戻ります。[count_threshold] 端子に接続されている Constant ブロックの値を変更することで、しきい値を変更できます。[Enable] 端子は、カウンターが加算カウントするか、あるいは前の値を保持するかを指定します。[Enable] 端子に接続されている Constant ブロックの値を変更することで、カウンター アクションを変更できます。値 1 は、カウンターが加算カウントすることを示します。値を 0 にすると、前のカウント値が保持されます。

ツール パスの設定

ターゲット プラットフォームで設計を合成するには、HDL ワークフロー アドバイザーを開いてワークフローを実行する前に、合成ツールへのパスを設定します。この例では XilinxVivado® を使用するため、XilinxVivado が既にインストールされていなければなりません。ツール パスを設定するには、hdlsetuptoolpath 関数を使用します。

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2024.1\bin\vivado.bat');

hdlsetuptoolpath を使用してその合成ツールへのパスを設定します。サポートされている最新のツールについては、HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアを参照してください。HDL コードを生成するが設計の合成は行わない場合は、ツール パスを設定する必要はありません。

HDL ワークフロー アドバイザーを開く

Simulink モデルから HDL ワークフロー アドバイザーを開くには、次の手順に従います。

[アプリ] タブで、[HDL Coder] を選択します。

モデルの DUT サブシステム

HDL_DUTを選択し、その名前が [HDL コード] タブの [次のコード] オプションに表示されることを確認します。選択内容を記憶しておくために、このオプションを固定します。[ワークフロー アドバイザー] をクリックします。

HDL ワークフロー アドバイザーを開くときに、プロジェクト フォルダーに互換性がないという警告がコード ジェネレーターで発生することがあります。アドバイザーを開くには、[削除して続行] を選択します。

HDL ワークフロー アドバイザーの左側のペインに、フォルダーでグループ化されたタスクのグループが表示されます。フォルダーを展開すると各フォルダーで使用可能なタスクが表示されます。タスクまたはフォルダーを選択すると、そのタスクまたはフォルダーについての情報が右側のペインに表示されます。右側のペインには、コードまたはテスト ベンチを生成するためのいくつかのパラメーターおよびオプションに対してタスクを実行する単純なコントロールがあり、ステータス メッセージやその他のタスク結果の表示領域があります。

個々のタスクの詳細については、そのタスクを右クリックし、[これはなに?] を選択します。

HDL ワークフロー アドバイザーのご利用の前にを参照してください。

HDL コードの生成

[ターゲットを設定] 、 [ターゲット デバイスおよび合成ツールを設定] 手順で、[合成ツール] に

[Xilinx Vivado]を選択して [このタスクを実行] を選択します。HDL ワークフロー アドバイザーのワークフローも参照してください。HDL コードを生成するがコードの合成は行わない場合は、[合成ツール] 設定を[No Synthesis Tool Specified]のままにします。

[ターゲット周波数を設定] タスクで、[ターゲット周波数] パラメーターを使用して、設計で実現するターゲット周波数を指定します。この例では、[ターゲット周波数 (MHz)] を

200に設定します。モデルのコード生成の互換性をチェックするには、[HDL コード生成に対するモデルを準備] フォルダーのタスクを実行します。[サンプル時間をチェック] タスクを右クリックし、[選択したタスクまで実行] を選択します。実行しているタスクによって警告が発生する場合は、[すべて変更] を選択してタスクを再実行します。

コード生成を変更するには、[コード生成オプションを設定] のタスクを使用します。たとえば、ターゲット HDL 言語およびターゲット コード生成フォルダーをカスタマイズするには、[基本オプションを設定] タスクを使用します。変更を行った後、[適用] をクリックします。

コードを生成するには、[RTL コードとテスト ベンチを生成] タスクを右クリックし、[選択したタスクまで実行] を選択します。

FPGA 合成および分析の実行

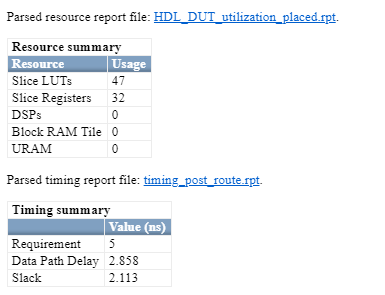

[FPGA 合成および分析] 、 [合成および P/R を実行] 、 [実装を実行] のタスクで、[このタスクをスキップ] の選択を解除し、[適用] をクリックします。その後、このタスクを右クリックして [選択したタスクまで実行] を選択します。

タスクには設計で消費されるリソースの量とデータ パスの遅延が表示されます。スラックは、組み合わせたパスについての要求された時間と到着時間との差異です。この場合、スラックは正の値であり、データが要求された時間よりも早く到着したことを意味します。

[合成結果をもつモデルに注釈を付ける] を右クリックし、[選択したタスクまで実行] を選択します。[合成ツール] として

[Microchip Libero SoC]を選択する場合、[合成結果をもつモデルに注釈を付ける] タスクは実行できません。クリティカル パスを確認するには、合成のワークフローを実行し、その後タイミング レポートを開きます。配線前後のタイミング情報の解析とモデルのクリティカル パスの視覚的な強調表示の詳細については、合成結果をもつモデルに注釈を付けるを参照してください。

モデル内の注釈付きクリティカル パスを表示します。

クリティカル パスとは、遅延が最大になる入力と出力との間を組み合わせたパスです。カウンター モデルのクリティカル パスの遅延は 2.77ns です。[実装を実行] タスクで報告されるデータ パスの遅延はクリティカル パスよりも大きくなります。これは、ターゲット FPGA での経路による遅延が考慮されるためです。リソースを節約し、クリティカル パスを最適化し、ターゲット FPGA での設計のタイミングを改善するには、HDL Coder™ で速度と面積の最適化を使用します。詳細については、HDL Coder での速度および面積の最適化を参照してください。

スクリプトを使用したコマンド ラインでのワークフローの実行

MATLAB® コマンド プロンプトで HDL ワークフローを実行するには、ワークフロー アドバイザー設定をスクリプトにエクスポートします。スクリプトにエクスポートするには、[HDL ワークフロー アドバイザー] ウィンドウで、[ファイル] 、 [スクリプトへのエクスポート] を選択します。[Export Workflow Configuration] ダイアログ ボックスで、ファイル名を入力してスクリプトを保存します。スクリプトを使用した HDL ワークフローの実行を参照してください。

参考

hdladvisor | hdlsetuptoolpath | makehdl