Simulink モデルからの HDL コードの生成

この例では、Simulink® で簡単なカウンター モデルの HDL コードを生成する方法を示します。このモデルは HDL コード生成と互換性があります。このカウンター モデルを作成するには、HDL 互換 Simulink モデルの作成を参照してください。

HDL コード生成用のモデル テンプレート

テンプレートを使用して、レジスタ、ROM、基本的な算術演算、複素数の乗算器、シフト レジスタなどをモデル化できます。

テンプレートを選択するには、MATLAB® ツールストリップで ![]() ボタンをクリックし、[HDL Coder] セクションに移動します。HDL コード生成用の Simulink テンプレートの使用を参照してください。

ボタンをクリックし、[HDL Coder] セクションに移動します。HDL コード生成用の Simulink テンプレートの使用を参照してください。

HDL コードを生成する前に、HDL コード アドバイザーを使用して、モデルの HDL 互換性をチェックし更新できます。HDL コード アドバイザーを使用した Simulink モデルの HDL 互換性のチェックを参照してください。

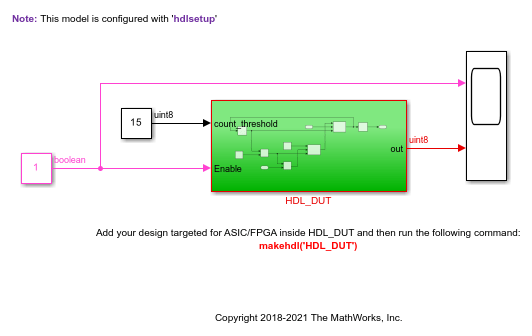

簡単なカウンター モデル

このモデルはゼロからしきい値である 15 までカウントし、ゼロに戻ります。[count_threshold] 端子に接続されている Constant ブロックの値を変更することで、しきい値を変更できます。[Enable] 端子は、カウンターが加算カウントするか、あるいは前の値を保持するかを指定します。[Enable] 端子に接続されている Constant ブロックの値を変更することで、カウンター アクションを変更できます。値 1 は、カウンターが加算カウントすることを示します。値を 0 にすると、前のカウント値が保持されます。

HDL コードの生成

カウンター モデルの場合、HDL_DUT サブシステムが DUT です。DUT のコードを生成するには、次を行います。

[アプリ] タブで、[HDL Coder] を選択します。

モデルの DUT サブシステムを選択し、その Subsystem 名が [HDL コード] タブの [次のコード] オプションに表示されることを確認します。選択内容を記憶しておくために、このオプションを固定します。[HDL コードを生成] をクリックします。

既定では、HDL Coder™ はターゲット hdlsrc フォルダーに VHDL コードを生成します。

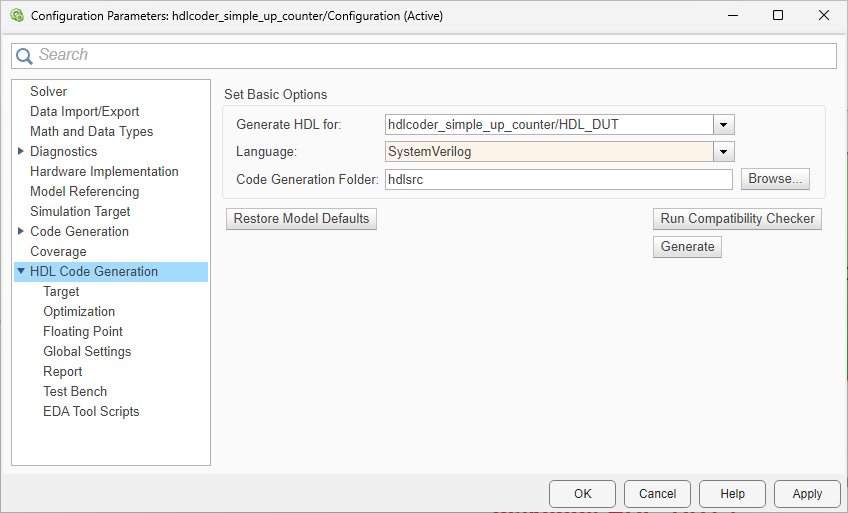

SystemVerilog コードの生成

カウンター モデル用の SystemVerilog コードを生成するには、次の手順を実行します。

[HDL コード] タブで、[設定] をクリックします。

[HDL コード生成] ペインで、[言語] に対して

[SystemVerilog]を選択します。[適用] をクリックし、[生成] をクリックします。

HDL Coder は、コードの生成前にモデルをコンパイルします。端子のデータ型などのモデルの表示オプションによっては、コードの生成後にモデルの外観が変わることがあります。コードの生成が進むにつれて、HDL Coder によって MATLAB コマンド ラインにコンフィギュレーション セットおよび生成されたファイルへのリンクを備えた進行状況を示すメッセージが表示されます。MATLAB エディターでファイルを表示するには、リンクをクリックします。

処理が完了し、次のメッセージが表示されます。

### HDL Code Generation Complete.

HDL コード生成ファイルの表示

hdlsrc フォルダーのフォルダー アイコンが現在のフォルダーに表示されます。生成されたコードとスクリプト ファイルを表示するには、hdlsrc フォルダーをダブルクリックし、HDL コードを生成したモデルと同じ名前のフォルダーをダブルクリックします。

HDL_DUT.vhd: エンティティ定義と設計したカウンターを実装する RTL アーキテクチャが含まれる VHDL® コードです。Verilog コードまたは SystemVerilog コードを生成した場合、HDL_DUT.vファイルまたはHDL_DUT.svファイルが得られます。HDL_DUT_compile.do: Siemens® ModelSim™ コンパイル スクリプト。HDL_DUT_map.txt:HDL コードの生成されたエンティティまたはモジュールを、それらを生成したモデルのサブシステムにマッピングするマッピング ファイル。マッピング ファイルを使用したコードのトレースを参照してください。HDL_DUT_report.html:HDL チェック レポートには HDL コード生成のステータスと警告またはメッセージが表示されます。gm_hdlcoder_simple_up_counter.slx:Simulink モデリング環境での HDL コードの動作を表す生成モデルです。hcv:Simulink の [コード ビュー] パネルに生成されたコードを表示するための HDL コード ビュー ファイル。Simulink で生成された HDL コードを表示するには、HDL Coder アプリで [コードの表示] をクリックします。

HDL Coder は HDL コードの動作モデルを作成します。このモデルを "生成されたモデル" といいます。生成されたモデルの名前は元のモデルと同じであり、接頭辞 gm_ をもちます。生成されたモデルは、生成された HDL コードについてビットトゥルーでサイクル アキュレートです。このモデルはブロック実装の効果と、指定した速度と面積の最適化を示しています。HDL Coder での速度および面積の最適化も参照してください。

カウンター用に生成されたモデルを開くには、次のように入力します。

gm_hdlcoder_simple_up_counter

カウンター モデルについては、最適化が無効になっているため、生成されたモデルは元のモデルと同じです。

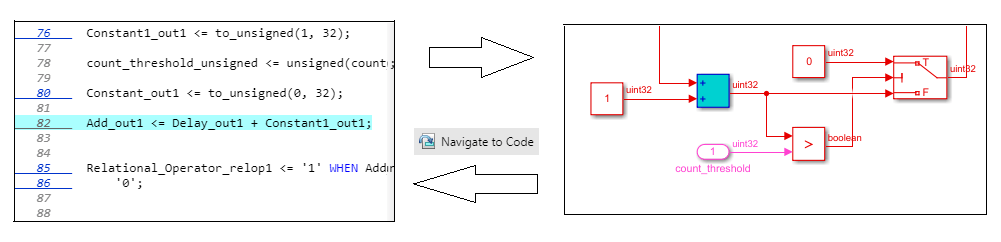

生成された HDL コードをモデルと一緒に表示するには、コード ビューを使用します。モデルの HDL コードを生成した後、モデルの右のコード ビューに生成されたコードが表示されます。コード ビューを手動で開くには、[HDL Coder] アプリを開きます。Simulink ツールストリップで [コードの表示] ボタンをクリックします。コード ビューの上部にあるドロップダウン リストを使用して、表示するファイルを選択します。コード ビューは、エディターにドッキングすることもドッキング解除することもでき、コード ビューの右上にある下矢印を使用して最小化または展開できます。

生成された HDL コードの検証

ソース モデルと生成された HDL コードとのマッピングをより簡単に特定するには、トレーサビリティ レポートを生成します。レポートを使用して、モデル内のブロックからそのブロック用に生成されたコードに移動し、コードからモデル内のブロックに移動します。

トレーサビリティ レポートを生成するには次のようにします。

[HDL コード] タブで、[設定] 、 [レポート オプション] をクリックします。

[HDL コード生成] 、 [レポート] ペインで、[トレーサビリティ レポートの生成] を選択し、

HDL_DUTサブシステムの HDL コードを生成します。

コードの生成後、[コード生成レポート] ウィンドウが開きます。HDL Coder は、コード生成レポート ファイルを、ビルド フォルダーの hdlsrc\html\ フォルダーに書き込みます。レポートを閉じた場合、このフォルダーに移動してレポートを開き直すことができます。

HDL コードからモデルに移動するには、以下のいずれかのワークフローに従います。

コード ビューを使用:

HDL コードの生成後に右側に表示されるコード ビュー パネルをクリックするか、[HDL Coder] アプリの Simulink ツールストリップで手動で [コードの表示] ボタンをクリックします。

モデル要素から対応する生成コードに移動するには、モデルでブロックをクリックします。コード ビューで、そのブロックのコードが強調表示され、強調表示されたコード行までスクロールされます。

コード ビューで、行番号のハイパーリンクまたはコード コメントのリンクをクリックすると、そのコード行のトレース先のブロックが強調表示されます。コードが生成されたモデル要素の行までコードをトレースできます。

コード生成レポートを使用:

[コード生成レポート] で、[トレーサビリティ レポート] セクションに移動し、[コードの場所] セクションのリンクをクリックします。

コードの行へのハイパーリンクを選択して、モデルの対応するブロックを強調表示します。

モデルのブロックから HDL コードに移動するには、そのブロックを選択し、[HDL コード] タブの [結果のレビュー] セクションにある [コードに移動] ボタンをクリクします。

トレーサビリティを使用した Simulink モデルと HDL コード間の移動およびコード生成レポートの作成と使用を参照してください。

[生成されるソース ファイル] セクションで HDL ファイル HDL_DUT をクリックする場合、信号 clk、reset、および clk_enable が表示されます。これらの信号は、ターゲット ハードウェアでフリップフロップを制御するクロック信号、リセット信号、クロック イネーブル信号です。HDL Coder は、モデルで使用する Delay ブロックなどのシーケンシャル要素に応じてこれらの信号をコード内で生成します。HDL Coder でのクロック バンドル信号の生成を参照してください。

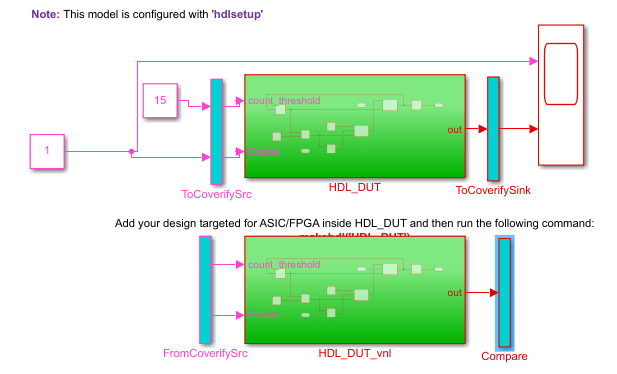

検証モデルを使用した HDL の動作の検証

HDL コードの動作モデルを元のモデルと検証するには、検証モデルを生成します。検証モデルには元のモデルと生成されたモデルの両方が含まれています。検証モデルは、元のモデルで提供するテスト ベクトルを使用して、両方のモデルの出力を比較します。

検証モデルを生成するには、次のようにします。

[HDL コード] タブで、[設定] をクリックします。

[HDL コード生成] 、 [グローバル設定] 、 [モデルの生成] タブで [検証モデル] を選択し、

HDL_DUTサブシステムの HDL コードを生成します。

コード生成ログに検証モデルへのリンクが表示されます。検証モデルには、生成されたモデルと同じ接頭辞と、接尾辞 _vnl があります。カウンター モデルでは、検証モデルは gm_hdlcoder_simple_up_counter_vnl.slx という名前です。このモデルは生成されたモデルと同じフォルダーにあります。このモデルを開くには、次を入力します。

gm_hdlcoder_simple_up_counter_vnl

モデルのシミュレーションを行った後、Compare サブシステムをダブルクリックして Assert_Out サブシステム内に移動します。Scope ブロックを開くと、err 信号は値がゼロであり、すなわち、生成されたモデルの出力が元のモデルと一致していることがわかります。

生成されたモデルと検証モデルを参照してください。

生成された HDL コードの検証

ターゲット ハードウェアでの設計の展開の前に、生成された HDL コードを検証します。hdlsrc フォルダーから、現在の作業フォルダーに移動します。Simulink モデルから生成された HDL コードの検証を参照してください。

参考

makehdl | hdlset_param | hdlsetup