このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

Simulink モデルから生成された HDL コードの検証

この例では、HDL テスト ベンチを生成し、簡単なカウンター モデルについて生成されたコードを検証する方法を示します。このモデルの HDL コードを生成するには、Simulink モデルからの HDL コードの生成を参照してください。このモデルの HDL コードを生成していない場合、HDL Coder™ はテスト ベンチを生成する前にコード生成を実行します。

HDL テスト ベンチとは

DUT についての HDL コードの機能を検証するには、HDL テスト ベンチを生成します。テスト ベンチには以下が含まれます。

テスト対象のエンティティに接続されている信号のソースによって生成されたスティミュラス データ。

テスト対象のエンティティによって生成された出力データ。テスト ベンチの実行中、このデータは検証のために VHDL® モデルの出力と比較されます。

テスト対象のエンティティを駆動するクロック、リセットおよびクロック イネーブルの入力。

テスト対象のエンティティをコンポーネントにインスタンス化したもの。

テスト対象のエンティティを駆動し、エンティティからの出力を予測されているデータと比較するコード。

Siemens® ModelSim™ シミュレーターを使用して、生成されたテスト ベンチおよびスクリプト ファイルのシミュレーションを実行できます。

簡単なカウンター モデル

このモデルを開いて、簡単なカウンターを表示します。モデルはゼロからしきい値までカウントし、ゼロに戻ります。しきい値は 15 に設定されています。しきい値を変更するには count_threshold 端子への入力の値を変更します。イネーブル信号は、カウンターが加算カウントするか、あるいは前の値を保持するかを指定します。1 の値は、カウンターが連続して加算カウントすることを示しています。

検証方法

HDL Verifier™ がインストールされている場合は、これらの方法を使用して生成された HDL コードを検証することもできます。

| 検証方法 | 詳細情報 |

|---|---|

| HDL コシミュレーション | コシミュレーション |

| SystemVerilog DPI テスト ベンチ | SystemVerilog DPI テスト ベンチ |

| FPGA インザループ | FPGA インザループ |

HDL テスト ベンチを生成

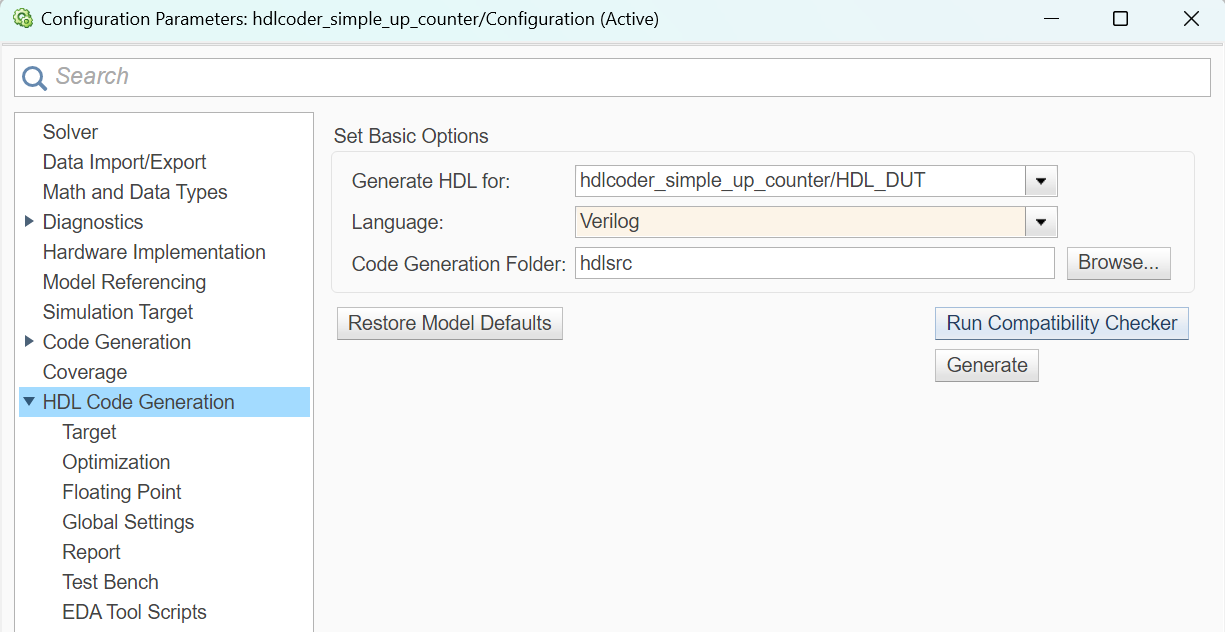

VHDL、Verilog®、または SystemVerilog の該当するテスト ベンチ コードを生成します。既定では、HDL コードおよびテスト ベンチ コードは、現在のフォルダーに対して相対的に同じターゲット フォルダー hdlsrc に書き込まれます。

カウンター モデルの場合、HDL_DUT サブシステムが DUT です。テストベンチを生成するには、このサブシステムを選択します。

[アプリ] タブで、[HDL Coder] を選択します。

DUT サブシステム

HDL_DUTを選択し、この名前が [HDL コード] タブの [次のコード] オプションに表示されることを確認します。選択内容を記憶しておくために、このオプションを固定します。[テストベンチの生成] をクリックします。

Verilog テスト ベンチ コードの生成

カウンター モデル用の Verilog テストベンチ コードを生成するには、次の手順を実行します。

[HDL コード] タブで、[設定] をクリックします。

[HDL コード生成] ペインで、[言語] に対して [

Verilog] を選択します。[HDL コード生成] 、 [テスト ベンチ] ペインで、[テスト ベンチを生成] をクリックします。

HDL Coder はモデルをコンパイルしてテスト ベンチを生成します。

テスト ベンチの生成が完了し、次のメッセージが表示されます。生成されたファイルは hdlsrc フォルダーに置かれます。

### HDL TestBench Generation Complete.

HDL テスト ベンチ ファイルの表示

カウンター モデルでは、hdlsrc フォルダーには次のテスト ベンチ ファイルが含まれています。

HDL_DUT_tb.vhd: 生成されたテストおよび出力データを含む VHDL テスト ベンチ コード。Verilog または SystemVerilog テスト ベンチ コードを生成した場合、生成されたファイルはHDL_DUT_tb.vまたはHDL_DUT_tb.svです。HDL_DUT_tb_pkg.vhd:VHDL テスト ベンチ コードのパッケージ ファイル。SystemVerilog テスト ベンチ コードを生成した場合、生成されたファイルはHDL_DUT_tb_pkg.svです。ターゲット言語として Verilog を指定した場合は、このファイルは生成されません。HDL_DUT_tb_compile.do: Siemens ModelSim コンパイル スクリプト (vcomコマンド)。このスクリプトはテスト対象のエンティティ (HDL_DUT.vhd) とテスト ベンチ コード (HDL_DUT_tb.vhd) のコンパイルおよび読み込みを行います。HDL_DUT_tb_sim.do: シミュレーターの初期化、[波形] ウィンドウの信号表示の設定、シミュレーションの実行を行う Siemens ModelSim スクリプト。

生成されたテスト ベンチ コードを MATLAB® エディターで表示するには、現在のフォルダーで HDL_DUT_tb.vhd または HDL_DUT_tb.v ファイルをダブルクリックします。

生成された HDL コードのシミュレーションの実行と検証

シミュレーション結果を検証するには、Siemens ModelSim シミュレーターを使用できます。Siemens ModelSim がインストール済みでなければなりません。

シミュレーターを開くには関数vsim (HDL Verifier)を使用します。実行可能ファイルへのパスを指定することで、このコマンドはシミュレーターを開く方法を示します。

vsim('vsimdir','C:\Program Files\ModelSim\questasim\10.6b\win64\vsim.exe')

生成されたモデルおよびテスト ベンチ コードをコンパイルし、シミュレーションを実行するには、HDL Coder によって生成されるスクリプトを使用します。カウンター モデルでは、次のコマンドを実行して、HDL_DUT サブシステム向けに生成されたテスト ベンチをコンパイルしてシミュレーションを行います。

Siemens ModelSim ソフトウェアを開いて、生成されたコード ファイルおよびスクリプトがあるフォルダーに移動します。

生成されたコンパイル スクリプトを使用して、生成されたモデルとテキスト ベンチ コードをコンパイルして読み込みます。

HDL_DUTサブシステムの場合、次のコマンドを実行して生成されたコードをコンパイルします。QuestaSim>do HDL_DUT_tb_compile.do

生成されたシミュレーション スクリプトを使用してシミュレーションを実行します。警告メッセージは無視できます。

HDL_DUTサブシステムでは、次のコマンドを実行して生成されたコードのシミュレーションを実行します。QuestaSim>do HDL_DUT_tb_sim.do

シミュレーターによって設計が最適化され、結果が [波形] ウィンドウに表示されます。シミュレーション結果が表示されない場合は [波形] ウィンドウを開きます。シミュレーション スクリプトによって、クロック信号、リセット信号、クロック イネーブル信号を含むモデルの入出力が [波形] ウィンドウに表示されます。

これで、信号を表示して、シミュレーション結果が元の設計の機能と一致していることを検証できます。検証後 Siemens ModelSim シミュレーターを閉じ、MATLAB エディターで開いているファイルを閉じます。

ターゲット デバイスでの生成 HDL コードの展開

生成されたコードをターゲット FPGA デバイスに展開するには Simulink® HDL ワークフロー アドバイザーを使用します。Simulink モデルからの HDL コード生成と FPGA 合成を参照してください。