このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

makehdl

モデル、サブシステム、モデル参照からの HDL RTL コードの生成

説明

makehdl( は、指定した DUT モデル、サブシステム、またはモデル参照から HDL コードを生成します。dut)

メモ

このコマンドを実行すると、Scope ブロックなどのブロックの [シミュレーション開始時に開く] 設定がアクティブになるため、そのブロックを呼び出せるようになります。

makehdl( は、1 つ以上の名前と値のペアの引数によって指定されるオプションを使用して、指定した DUT モデル、サブシステム、またはモデル参照から HDL コードを生成します。dut,Name,Value)

例

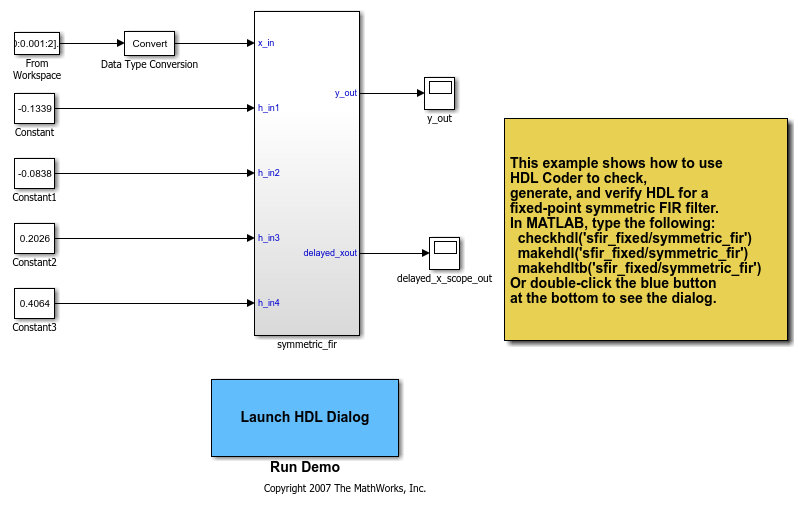

この例では、対称 FIR モデル用の VHDL を生成する方法を示します。

sfir_fixed モデルを開きます。

sfir_fixed

コード生成オプションを既定値に設定し、現在のモデルの HDL コードを生成します。

makehdl('sfir_fixed/symmetric_fir','TargetDirectory','C:\GenVHDL\hdlsrc')

### Generating HDL for 'sfir_fixed/symmetric_fir'. ### Starting HDL check. ### Begin VHDL Code Generation for 'sfir_fixed'. ### Working on sfir_fixed/symmetric_fir as C:\GenVHDL\hdlsrc\sfir_fixed\symmetric_fir.vhd. ### Creating HDL Code Generation Check Report file://C:\GenVHDL\hdlsrc\sfir_fixed\symmetric_fir_report.html ### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings, and 0 messages. ### HDL code generation complete.

生成された VHDL コードは hdlsrc フォルダーに保存されます。

sfir_fixed モデル内のサブシステム symmetric_fir に対して Verilog® を生成します。

sfir_fixed モデルを開きます。

sfir_fixed;

モデルが新しい Simulink® ウィンドウで開きます。

symmetric_fir サブシステムに対して Verilog を生成します。

makehdl('sfir_fixed/symmetric_fir', 'TargetLanguage', 'Verilog', ... 'TargetDirectory', 'C:/Generate_Verilog/hdlsrc')

### Generating HDL for 'sfir_fixed/symmetric_fir'. ### Starting HDL check. ### Begin Verilog Code Generation for 'sfir_fixed'. ### Working on sfir_fixed/symmetric_fir as C:\Generate_Verilog\hdlsrc\sfir_fixed\symmetric_fir.v. ### Creating HDL Code Generation Check Report file://C:\Generate_Verilog\hdlsrc\sfir_fixed\symmetric_fir_report.html ### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings, and 0 messages. ### HDL code generation complete.

symmetric_fir サブシステムに対して生成された Verilog コードは、hdlsrc\sfir_fixed\symmetric_fir.v に保存されます。

モデルを閉じます。

bdclose('sfir_fixed');

sfir_fixed モデル内のサブシステム symmetric_fir に対して SystemVerilog コードを生成します。

sfir_fixed モデルを開きます。

sfir_fixed;

モデルが新しい Simulink® ウィンドウで開きます。

symmetric_fir サブシステムに対して SystemVerilog コードを生成します。

makehdl('sfir_fixed/symmetric_fir', 'TargetLanguage', 'SystemVerilog', ... 'TargetDirectory', 'C:/Generate_SV/hdlsrc')

### Generating HDL for 'sfir_fixed/symmetric_fir'.

### Using the config set for model <a href="matlab:configset.showParameterGroup('sfir_fixed', { 'HDL Code Generation' } )">sfir_fixed</a> for HDL code generation parameters.

### Running HDL checks on the model 'sfir_fixed'.

### Begin compilation of the model 'sfir_fixed'...

### Working on the model 'sfir_fixed'...

### Working on... <a href="matlab:configset.internal.open('sfir_fixed', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_sfir_fixed' ....

### Copying DUT to the generated model....

### Model generation complete.

### Begin SystemVerilog Code Generation for 'sfir_fixed'.

### Working on sfir_fixed/symmetric_fir as C:\Generate_SV\hdlsrc\sfir_fixed\symmetric_fir.sv.

### Code Generation for 'sfir_fixed' completed.

### Creating HDL Code Generation Check Report file:///C:/Generate_SV/hdlsrc/sfir_fixed/symmetric_fir_report.html

### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

symmetric_fir サブシステムに対して生成された SystemVerilog コードは、hdlsrc\sfir_fixed\symmetric_fir.sv に保存されます。

モデルを閉じます。

bdclose('sfir_fixed');

サブシステム symmetric_fir が HDL コード生成と互換性をもつことを確認してから、HDL を生成します。

sfir_fixed モデルを開きます。

sfir_fixed

モデルが新しい Simulink® ウィンドウで開きます。

関数 checkhdl を使用して、symmetric_fir サブシステムが HDL コード生成と互換性があるかどうかを確認します。

hdlset_param('sfir_fixed','TargetDirectory','C:/HDL_Checks/hdlsrc'); checkhdl('sfir_fixed/symmetric_fir')

### Starting HDL check. ### Creating HDL Code Generation Check Report file://C:\HDL_Checks\hdlsrc\sfir_fixed\symmetric_fir_report.html ### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings, and 0 messages.

checkhdl は正常に完了しました。これは、HDL コード生成と互換性のあるモデルであることを意味しています。コードを生成するには、makehdl を使用します。

makehdl('sfir_fixed/symmetric_fir')

### Generating HDL for 'sfir_fixed/symmetric_fir'.

### Using the config set for model <a href="matlab:configset.showParameterGroup('sfir_fixed', { 'HDL Code Generation' } )">sfir_fixed</a> for HDL code generation parameters.

### Starting HDL check.

### Begin VHDL Code Generation for 'sfir_fixed'.

### Working on sfir_fixed/symmetric_fir as C:\HDL_Checks\hdlsrc\sfir_fixed\symmetric_fir.vhd.

### Creating HDL Code Generation Check Report file://C:\HDL_Checks\hdlsrc\sfir_fixed\symmetric_fir_report.html

### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

symmetric_fir サブシステムに対して生成された VHDL® コードは、hdlsrc\sfir_fixed\symmetric_fir.vhd に保存されます。

モデルを閉じます。

bdclose('sfir_fixed');

入力引数

サブシステム名、最上位モデルの名前、または絶対階層パスを含むモデル参照名として指定します。

例: 'top_level_name'

例: 'top_level_name/subsysA/subsysB/codegen_subsys_name'

名前と値の引数

オプションの引数のペアを Name1=Value1,...,NameN=ValueN として指定します。ここで、Name は引数名で、Value は対応する値です。名前と値の引数は他の引数の後に指定しなければなりませんが、ペアの順序は重要ではありません。

R2021a より前では、名前と値をそれぞれコンマを使って区切り、Name を引用符で囲みます。

例: 'TargetLanguage','Verilog'

ターゲット言語とフォルダー選択オプション

モデル内の HDL コードを生成するサブシステムを指定します。詳細については、HDL を生成を参照してください。

VHDL または Verilog コードのどちらを生成するかを指定します。詳細については、言語を参照してください。

生成されるファイルと HDL コードを書き込むパスを指定します。詳細については、Code Generation Folderを参照してください。

ツールと合成オプション

生成される HDL コードをターゲットにするように合成ツールを文字ベクトルとして指定します。詳細については、Synthesis Toolを参照してください。

ターゲット デバイスの合成ツールのチップ ファミリを文字ベクトルとして指定します。詳細については、Familyを参照してください。

ターゲット デバイスの合成ツールのデバイス名を文字ベクトルとして指定します。詳細については、Deviceを参照してください。

ターゲット デバイスの合成ツールのパッケージ名を文字ベクトルとして指定します。詳細については、Packageを参照してください。

ターゲット デバイスの合成ツールの速度値を文字ベクトルとして指定します。詳細については、Speedを参照してください。

ターゲット周波数 (MHz) を文字ベクトルとして指定します。詳細については、ターゲット周波数を参照してください。

一般的な最適化とマルチサイクル パス制約の設定

モデルに対して遅延の均衡化を有効にするかどうかを指定します。詳細については、Balance delaysを参照してください。

レジスタではなく RAM にマッピングする際に必要な最小 RAM サイズを指定します。次のいずれかを指定できます。

マッピングのしきい値を定義する単一の整数。このしきい値のビット サイズを超えるすべての遅延または永続配列が RAM にマッピングされます。

2 つのしきい値を定義する string。1 つは遅延の長さまたは配列サイズ、もう 1 つは語長です。

詳細については、RAM マッピングのしきい値を参照してください。

生成される HDL コードのパイプライン レジスタを FPGA 上のブロック RAM にマッピングするかどうかを指定します。詳細については、RAM へのパイプライン遅延のマッピングを参照してください。

非ゼロの初期値をもつ Delay ブロックを、ゼロの初期値をもつ Delay ブロックに変換するかどうかを指定します。詳細については、Transform non zero initial value delayを参照してください。

しきい値に基づく設計内の乗算器の分割。このしきい値は正の整数、N でなければなりません。詳細については、乗算器分割のしきい値を参照してください。

詳細については、未使用の端子を削除を参照してください。

イネーブルベースのマルチサイクル パス制約ファイルを生成します。詳細については、Enable-based constraintsを参照してください。

パイプラインと速度の最適化オプション

分散型パイプライン方式および遅延吸収で数値の整合性とパフォーマンスのどちらを優先するか。'Numerical Integrity' または 'Performance' として指定します。詳細については、Pipeline distribution priorityを参照してください。

分散型パイプライン方式および遅延吸収のときに設計上の遅延分散を許可するオプション。'off' または 'on' として指定します。詳細については、設計上の遅延分散を許可を参照してください。

分散型パイプライン方式で合成タイミング推定を使用し、ハードウェアに対するコンポーネントの機能をより正確に反映することで、分散型パイプラインの精度を高めてターゲット デバイスのクロック速度を上げます。詳細については、Use synthesis estimates for distributed pipeliningを参照してください。

マルチサイクル パスにパイプライン レジスタをデータ レートではなくクロック レートで挿入します。詳細については、クロックレート パイプラインを参照してください。

DUT 端子に対してクロック レート パイプラインを有効にします。詳細については、DUT 出力端子のクロックレート パイプラインを許可を参照してください。

設計に適応パイプライン レジスタを挿入します。詳細については、適応パイプラインを参照してください。

リソース共有と面積の最適化オプション

リソース共有の最適化を使用して、設計内の加算器を共有します。詳細については、Share Addersを参照してください。

リソース共有の最適化のための共有加算器の最小ビット幅。正の整数として指定します。詳細については、加算器共有の最小ビット幅を参照してください。

リソース共有の最適化を使用して、設計内の乗算器を共有します。詳細については、Share Multipliersを参照してください。

リソース共有の最適化のための共有乗算器の最小ビット幅。正の整数として指定します。詳細については、乗算器共有の最小ビット幅を参照してください。

コード ジェネレーターが他の乗算器と共有するために乗算器を拡張する最小語長。詳細については、乗算器拡張のしきい値を参照してください。

リソース共有の最適化を使用して、設計内の Multiply-Add ブロックを共有します。詳細については、Share Multipliersを参照してください。

リソース共有の最適化のための共有 Multiply-Add ブロックの最小ビット幅。正の整数として指定します。詳細については、Multiply-Add ブロック共有の最小ビット幅を参照してください。

リソース共有の最適化を使用して、設計内の Atomic Subsystem ブロックを共有します。詳細については、アトミック サブシステムを参照してください。

リソース共有の最適化を使用して、設計内の MATLAB Function ブロックを共有します。詳細については、MATLAB Function ブロックを参照してください。

リソース共有の最適化を使用して、設計内の浮動小数点 IP を共有します。詳細については、Floating-Point IPsを参照してください。

浮動小数点のターゲット

詳細については、ベンダー固有の浮動小数点ライブラリを参照してください。

コード生成レポートのオプション

コードからモデルへ、モデルからコードへ移動するハイパーリンクを含むトレーサビリティ レポートを生成します。詳細については、Generate traceability reportを参照してください。

コードからモデルへ、モデルからコードへ移動するために、各行からのハイパーリンク、またはコードのブロックを示すコメントへのハイパーリンクを含むトレーサビリティ レポートを生成します。詳細については、Traceability styleを参照してください。

生成される HDL コードによって使用されるハードウェア リソースの数を表示するリソース利用レポートを生成します。詳細については、Generate resource utilization reportを参照してください。

ストリーミング、共有、分散型パイプライン方式などの最適化の効果を表示する最適化レポートを生成します。詳細については、Generate optimization reportを参照してください。

コード生成レポートにモデルの Web 表示を生成し、コードとモデル間の移動を容易にします。詳細については、Generate model Web viewを参照してください。

クロック設定

生成される HDL コードで同期リセットと非同期リセットのどちらを使用するかを指定します。詳細については、Reset typeを参照してください。

リセット入力信号のアサート レベルにアクティブ High かアクティブ Low のどちらを使用するかを指定します。詳細については、リセットのアサート レベルを参照してください。

クロック入力端子の名前を文字ベクトルとして指定します。詳細については、Clock input portを参照してください。

クロック イネーブル入力端子の名前を文字ベクトルとして指定します。詳細については、クロック イネーブルの入力端子を参照してください。

リセット入力端子の名前。文字ベクトルとして指定します。

詳細については、Reset input portを参照してください。

生成される HDL コードのアクティブなクロック エッジを指定します。詳細については、クロック エッジを参照してください。

HDL コードに単一クロック入力と複数クロック入力のどちらを生成するかを指定します。詳細については、クロック入力を参照してください。

グローバル オーバーサンプリング クロックの周波数。モデルのベース レートの整数倍として指定します。詳細については、Simulink のレートを実際のハードウェアのレートとして扱うおよびオーバーサンプリング係数を参照してください。

一般的なファイルおよび変数名のオプション

生成される HDL ファイルとテスト ベンチ ファイルのヘッダー内のコメント行を指定します。詳細については、Comment in headerを参照してください。

生成される Verilog ファイル名の拡張子を指定します。詳細については、Verilog ファイルの拡張子を参照してください。

生成される VHDL ファイル名の拡張子を指定します。詳細については、VHDL ファイルの拡張子を参照してください。

重複するエンティティまたはモジュール名を解決する接尾辞を文字ベクトルとして指定します。詳細については、Entity conflict postfixを参照してください。

パッケージ ファイル名の接尾辞を文字ベクトルとして指定します。詳細については、Package postfixを参照してください。

詳細については、Reserved word postfixを参照してください。

詳細については、Split entity and architectureを参照してください。

詳細については、Split entity file postfixを参照してください。

詳細については、Split arch file postfixを参照してください。

詳細については、VHDL architecture nameを参照してください。

クロック プロセス名の接尾辞を文字ベクトルとして指定します。詳細については、Clocked process postfixを参照してください。

詳細については、複素数の虚数部の接尾辞を参照してください。

詳細については、複素数の実数部の接尾辞を参照してください。

内部クロック イネーブル信号と制御フロー イネーブル信号の接頭辞。文字ベクトルとして指定します。詳細については、[クロック イネーブルの入力端子] および [イネーブル信号の接頭辞] を参照してください。

生成される HDL コード内の個々のモジュールまたはエンティティの名前の接頭辞を指定します。HDL Coder™ は、生成されたスクリプト ファイルの名前にもこの接頭辞を適用します。

詳細については、モジュール名の接頭辞を参照してください。

詳細については、Timing controller postfixを参照してください。

詳細については、パイプラインの接尾辞を参照してください。

詳細については、VHDL ライブラリ名を参照してください。

詳細については、ブロック生成ラベルを参照してください。

詳細については、出力生成ラベルを参照してください。

詳細については、インスタンス生成ラベルを参照してください。

詳細については、インスタンスの接尾辞を参照してください。

詳細については、インスタンスの接頭辞を参照してください。

詳細については、ベクトルの接頭辞を参照してください。

詳細については、マップ ファイルの接尾辞を参照してください。

端子のコンフィギュレーション オプション

VHDL 入力は、'std_logic_vector' または 'signed/unsigned' データ型をもつことができます。Verilog 入力は 'wire' でなければなりません。

詳細については、入力データ型を参照してください。

VHDL 出力は、'Same as input data type'、'std_logic_vector'、または 'signed/unsigned' にすることができます。Verilog 出力は 'wire' でなければなりません。

詳細については、出力データ型を参照してください。

クロック イネーブル出力端子の名前。文字ベクトルとして指定します。

詳細については、クロック イネーブルの出力端子を参照してください。

詳細については、クロック イネーブルの最小化を参照してください。

詳細については、グローバル リセットの最小化を参照してください。

詳細については、Use trigger signal as clockを参照してください。

詳細については、Enable HDL DUT output port generation for test pointsを参照してください。

詳細については、Scalarize portsを参照してください。

コーディング スタイル

詳細については、Represent constant values by aggregatesを参照してください。

詳細については、インラインの MATLAB Function ブロック コードを参照してください。

詳細については、Initialize all RAM blocksを参照してください。

詳細については、RAM アーキテクチャを参照してください。

詳細については、No-reset registers initializationを参照してください。

詳細については、中間信号を最小にするを参照してください。

詳細については、For-Generate ループの展開を参照してください。

詳細については、Generate parameterized HDL code from masked subsystemを参照してください。

詳細については、Enumerated Type Encoding Schemeを参照してください。

詳細については、Indexing for scalarized port namingを参照してください。

詳細については、Use “rising_edge/falling_edge” style for registersを参照してください。

詳細については、Inline VHDL configurationを参照してください。

詳細については、Concatenate type safe zerosを参照してください。

生成される HDL コードを難読化するかどうかを指定します。詳細については、Generate obfuscated HDL codeを参照してください。

テスト対象設計 (DUT) インターフェイスとさまざまなサブシステムレベルのインターフェイスで、バス信号の VHDL 構造レコード タイプを使用するコードを生成するかどうかを指定します。詳細については、Preserve Bus structure in the generated HDL codeを参照してください。

詳細については、Optimize timing controllerを参照してください。

詳細については、Timing controller architectureを参照してください。

詳細については、カスタム ファイルのヘッダー コメントを参照してください。

詳細については、Custom File Footer Commentを参照してください。

詳細については、Emit time/date stamp in headerを参照してください。

詳細については、Include requirements in block commentsを参照してください。

詳細については、Verilog または SystemVerilog `timescale 命令の使用を参照してください。

詳細については、Verilog or SystemVerilog timescale specificationを参照してください。

コーディング標準

生成される HDL コードが業界のコーディング標準ガイドラインに準拠しなければならないかどうかを指定します。詳細については、HDL coding standardを参照してください。

HDL コードを生成するときに、業界のコーディング標準と共に使用するコーディング標準のカスタマイズ オブジェクト。詳細については、hdlcoder.CodingStandardを参照してください。

モデル生成パラメーター

詳細については、Generated modelを参照してください。

詳細については、Validation modelを参照してください。

詳細については、Prefix for generated model nameを参照してください。

詳細については、検証モデル名の接尾辞を参照してください。

詳細については、Layout styleを参照してください。

詳細については、信号の自動経路指定を参照してください。

詳細については、Inter-block horizontal scalingを参照してください。

詳細については、Inter-block vertical scalingを参照してください。

診断とコード生成の出力パラメーター

設計内のフィードバック ループを強調表示するかどうかを指定します。

クロックレート パイプラインの最適化に対する障壁を強調表示するかどうかを指定します。

分散型パイプラン方式を抑制するブロックを強調表示するかどうかを指定します。

詳細については、Check for name conflicts in black box interfacesを参照してください。

詳細については、生成された HDL コード内での実数の有無のチェックを参照してください。

HDL コードを生成するか、生成されたモデルの表示のみを行うか、HDL コードを生成して生成されたモデルを表示するかを指定します。詳細については、HDL コードの生成を参照してください。

モデルの HDL コードを生成します。詳細については、HDL コードの生成を参照してください。

スクリプトの生成

詳細については、EDA スクリプトを生成を参照してください。

詳細については、コンパイルの初期化を参照してください。

詳細については、コンパイルの終了を参照してください。

詳細については、コンパイル ファイルの接尾辞を参照してください。

Verilog コンパイル コマンド。文字ベクトルとして指定します。SimulatorFlags の名前と値のペアで 1 番目の引数を指定し、モジュール名を 2 番目の引数に指定します。

詳細については、Verilog または SystemVerilog のコンパイル コマンドを参照してください。

VHDL コンパイル コマンド。文字ベクトルとして指定します。SimulatorFlags の名前と値のペアで 1 番目の引数を指定し、エンティティ名を 2 番目の引数に指定します。

詳細については、VHDL のコンパイル コマンドを参照してください。

詳細については、Choose HDL lint toolを参照してください。

HDL lint の初期化名。文字ベクトルとして指定します。既定値は、HDLLintTool の名前と値のペアから派生します。

詳細については、Lint initializationを参照してください。

HDL lint コマンド。文字ベクトルとして指定します。既定値は、HDLLintTool の名前と値のペアから派生します。

詳細については、Lint commandを参照してください。

HDL lint の終了。文字ベクトルとして指定します。既定値は、HDLLintTool の名前と値のペアから派生します。

詳細については、Lint terminationを参照してください。

詳細については、合成ツールを選択を参照してください。

HDL 合成コマンド。文字ベクトルとして指定します。既定値は、HDLSynthTool の名前と値のペアから派生します。

詳細については、Synthesis commandを参照してください。

HDL 合成スクリプト ファイル名の接尾辞。文字ベクトルとして指定します。既定値は、HDLSynthTool の名前と値のペアから派生します。

詳細については、Synthesis file postfixを参照してください。

HDL 合成スクリプトの初期化。文字ベクトルとして指定します。既定値は、HDLSynthTool の名前と値のペアから派生します。

詳細については、Synthesis initializationを参照してください。

HDL 合成スクリプトの終了名。既定値は、HDLSynthTool の名前と値のペアから派生します。

詳細については、Synthesis terminationを参照してください。

バージョン履歴

R2006b で導入

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)