Simscape ハードウェアインザループ ワークフロー

Simscape モデルからの HDL コードの生成とターゲット ハードウェアへの展開

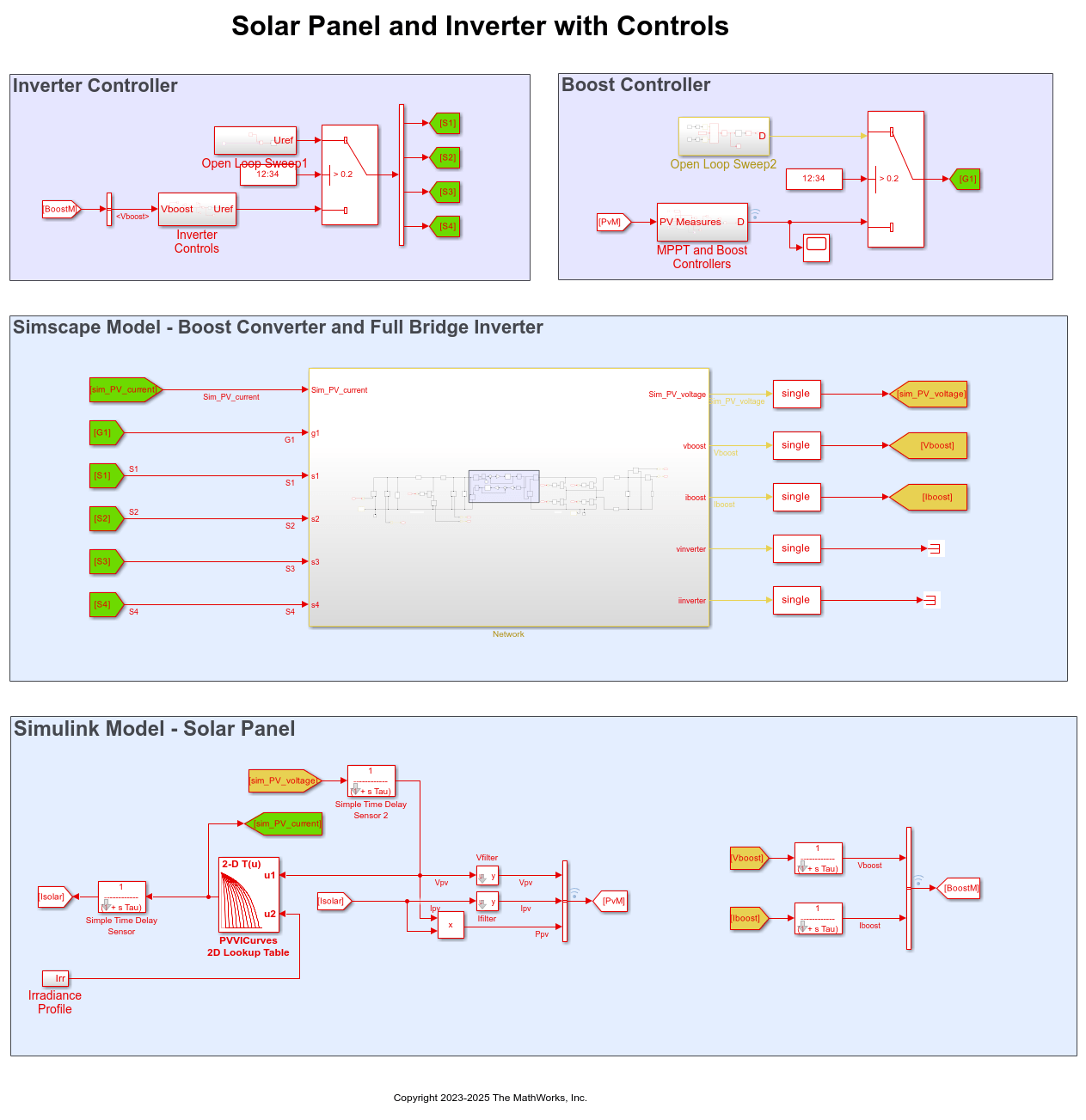

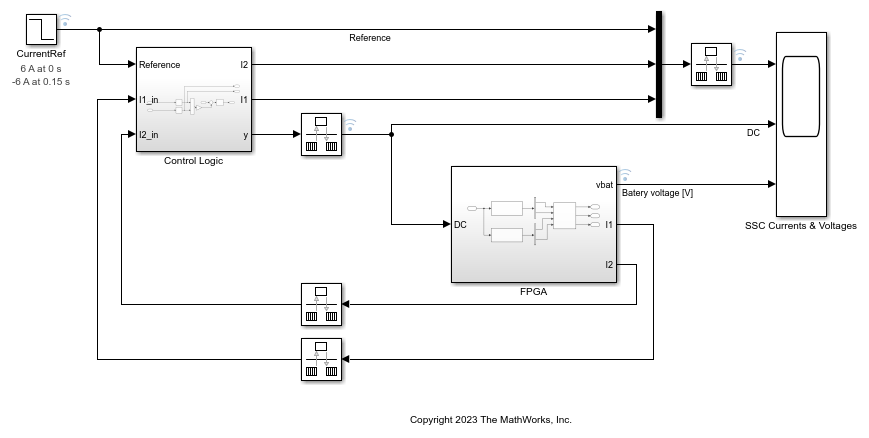

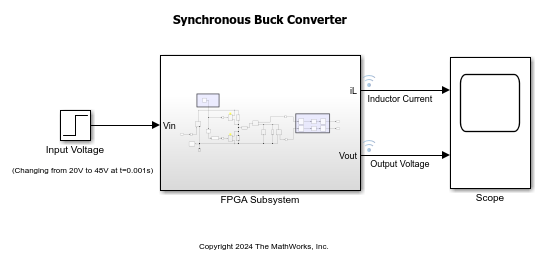

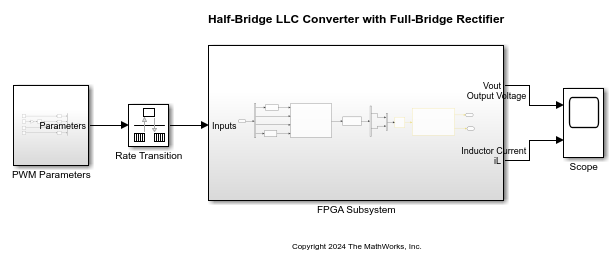

Simscape™ ハードウェアインザループ (HIL) ワークフローでは、Simscape プラント モデルの HDL コードを生成し、生成されたコードを汎用のフィールド プログラマブル ゲート アレイ (FPGA)、System on a Chip (SoC)、または Speedgoat® FPGA I/O モジュールに展開できます。プラント モデルを FPGA ボードに展開することで、モデルのシミュレーションを高速化し、HIL シミュレーションを使用してモデルをリアルタイムでシミュレートできます。

Simscape HDL ワークフロー アドバイザーは、Simscape プラント モデルを HDL コード生成用の HDL 互換の実装モデルに変換します。sschdladvisor 関数を使用してアドバイザーを開き、アドバイザーでタスクを実行して HDL 実装モデルを生成できます。HDL 実装モデルを生成するとき、実装モデルのデータ型の精度 (single や double などの浮動小数点か固定小数点) を指定できます。実装モデルに妥当性確認ロジックの挿入を指定し、HDL 実装が元の Simscape アルゴリズムと数値的に一致するかを検証することもできます。

HDL 実装モデルの生成後、HDL Coder™ を使用してこのモデルのコードを生成し、生成されたコードを HDL ワークフロー アドバイザーを使用してターゲット プラットフォームに展開できます。

Simscape ハードウェアインザループ ワークフローの基本

カテゴリ

- モデルの準備

プラント モデルの準備と構成

- HDL コード生成

プラント モデルの HDL 互換 Simulink モデルの生成と HDL コードの生成

- 展開

生成された HDL コードのターゲット ハードウェアへの展開

- トラブルシューティング

ワークフローの問題に対処するためのトラブルシューティングの提案と解決法

- 用途

リアルタイム アプリケーションの例の確認