Speedgoat FPGA IO モジュールへの Simscape DC モーター モデルの展開

この例では、DC モーターなどの非線形 Simscape™ モデル用の FPGA ビットストリームを生成して Speedgoat® FPGA I/O モジュールに展開する方法を示します。

はじめに

この例では、Simscape モデル (線形と非線形の両方) 用の HDL コードを生成してそのコードを FPGA に展開する方法について説明します。Simscape HDL ワークフロー アドバイザーを使用して、HDL 実装モデルを生成できます。次に、HDL ワークフロー アドバイザーを使用して、生成された実装モデル用の HDL コードおよび FPGA ビットストリームを生成します。HDL 互換の Simulink® モデル (HDL 実装モデル) をシミュレートして Simscape モデルに対して検証できます。Simulink Real-Time™ 開発環境を使用して、Speedgoat リアルタイム ターゲット コンピューターで直接実行されるリアルタイム モデルを生成、展開、および実行します。

この例では、次の方法について説明します。

後退オイラー法ソルバーを使用して線形 Simscape モデルの HDL コードを生成する。

分割ソルバーを使用して非線形 Simscape モデルの HDL コードを生成する。

HDL ワークフロー アドバイザーを使用して I/O 334-325K モジュールの FPGA ビットストリームを生成する。

Simulink Real-Time を使用して、リアルタイム モデルを Speedgoat のリアルタイム ターゲット マシンに展開する。

セットアップと構成

1. HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアにリストされている Xilinx® Vivado® の最新バージョンをインストールします。

次に、関数hdlsetuptoolpathを使用して、インストールした Xilinx Vivado 実行可能ファイルへのツール パスを設定します。

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2020.2\bin\vivado.bat')

2. リアルタイム シミュレーション用に、開発環境とターゲット コンピューターの設定を行います。Get Started with Simulink Real-Time (Simulink Real-Time)を参照してください。

3. Speedgoat ライブラリおよび Speedgoat HDL Coder Integration Package をインストールします。Install Speedgoat HDL Coder Integration Packages を参照してください。

降圧コンバーター

降圧コンバーターは、出力 (負荷) に対して入力 (電源) の電圧を降下させる DC/DC パワー コンバーターです。連続伝導モード (インダクタを通過する電流がゼロに低下しない) では、降圧コンバーターの理論的な伝達関数は次のようになります。

,

,

ここで、 はデューティ比です。この例では、コンバーターは 12 V の電源から抵抗の負荷をフィードし、PWM 周波数は 200 Hz に設定されています。この例では、降圧コンバーターの出力電圧を制御する方法を説明します。デューティ比を調整するために、Control サブシステムは PI ベースの制御アルゴリズムを使用します。

はデューティ比です。この例では、コンバーターは 12 V の電源から抵抗の負荷をフィードし、PWM 周波数は 200 Hz に設定されています。この例では、降圧コンバーターの出力電圧を制御する方法を説明します。デューティ比を調整するために、Control サブシステムは PI ベースの制御アルゴリズムを使用します。

降圧コンバーターと固定抵抗 (線形 Simscape ネットワーク)

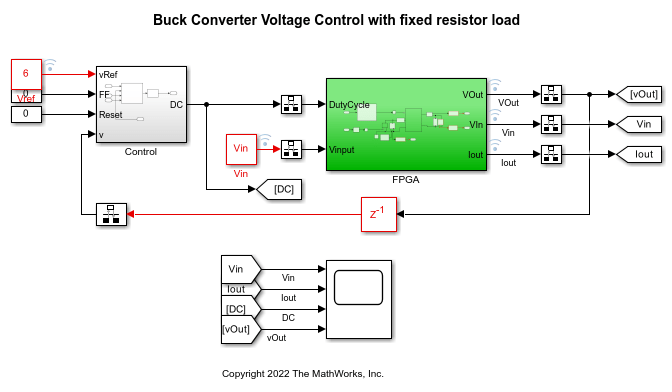

モデル ee_buck_converter_hdl.slx は降圧コンバーターと負荷としての固定抵抗で構成されます。固定抵抗は線形 Simscape 素子であるため、モデルでは後退オイラー法ソルバーを使用します。

降圧コンバーター モデルを表示するには、次のコマンドを実行します。

open_system('ee_buck_converter_hdl')

HDL コードの生成と展開の手順の詳細については、HDL ワークフロー スクリプトを使用した Simscape 電力網連結コンバーター モデルの Speedgoat IO モジュールへの展開を参照してください。

降圧コンバーターと DC モーター (非線形 Simscape ネットワーク)

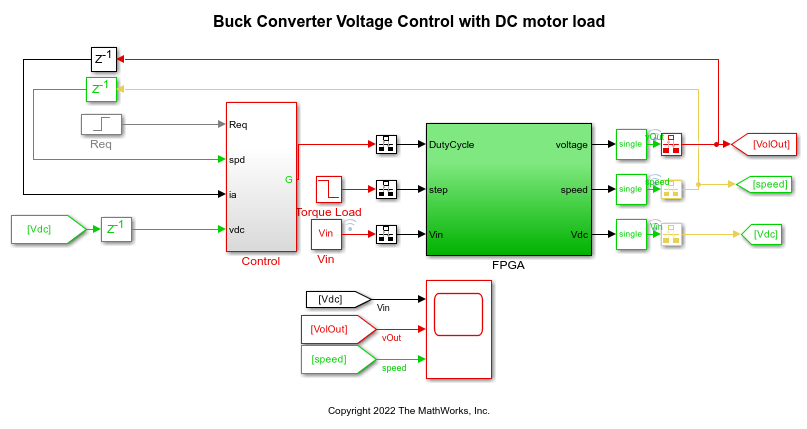

モデル ee_buck_converter_dc_motor_hdl.slx は降圧コンバーターと負荷としての DC モーターで構成されます。DC モーターは非線形素子であるため、このモデルでは分割ソルバーを使用します。詳細については、分割ソルバーの仕組みについて (Simscape)を参照してください。

降圧コンバーター モデルを表示するには、次のコマンドを実行します。

open_system('ee_buck_converter_dc_motor_hdl')

PWM 発生器と降圧コンバーターを含む緑の FPGA サブシステム内にあるブロック用に、VHDL® コードまたは Verilog® コードを生成します。

open_system('ee_buck_converter_dc_motor_hdl/FPGA')

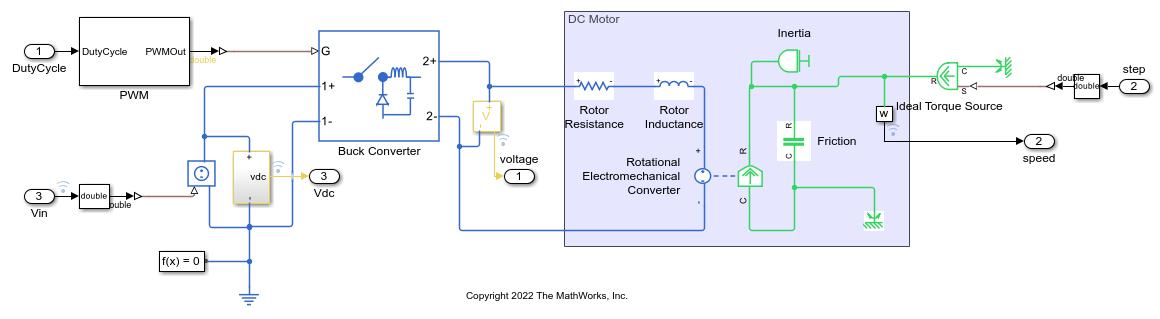

このモデルでは、Buck Converter ブロックは、接続されているコントローラーおよびゲート信号発生器によって駆動される DC 電圧を降下させるコンバーターを表します。降圧コンバーターは、電圧の振幅を下げるため、降圧レギュレーターとも呼ばれます。Rotational Electromechanical Converter ブロックは、電気ドメインと機械回転ドメイン間のインターフェイスを提供します。電気エネルギーを回転運動形式の機械エネルギーに変換します。また、回転運動を電気エネルギーに変換することもできます。

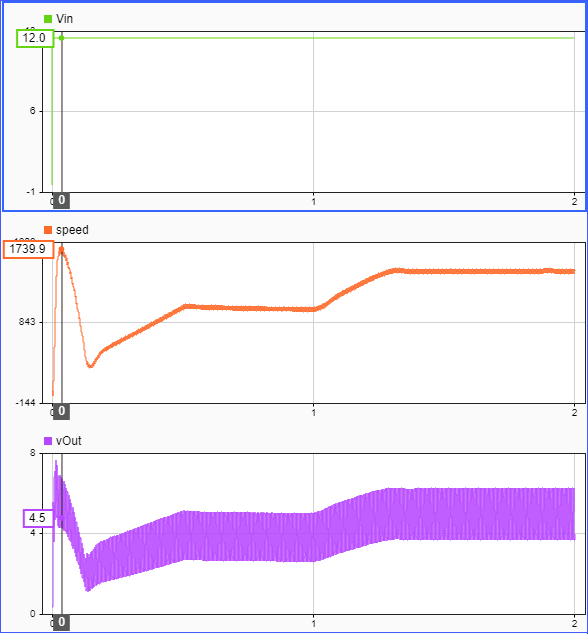

降圧コンバーター モデルのデスクトップ シミュレーションの実行

DC 入力電圧、PWM 周波数、およびデューティ比を含む入力信号が、モデルの最上位レベルで生成されます。Simscape モデルのサンプル時間は 6 μs に設定されています。信号のログがモデルの最上位レベルで有効になっています。

sim('ee_buck_converter_dc_motor_hdl') % Display the buck converter output signals in SDI Simulink.sdi.clearAllSubPlots Simulink.sdi.setSubPlotLayout(3,1); allIDs2 = Simulink.sdi.getAllRunIDs; runID2 = allIDs2(end); run2 = Simulink.sdi.getRun(runID2); run2.name = 'Simscape Desktop Simulation'; run2.getAllSignals; plotOnSubPlot(run2.getSignalsByName('Vin'),1,1,true); plotOnSubPlot(run2.getSignalsByName('speed'),2,1,true); plotOnSubPlot(run2.getSignalsByName('vOut'),3,1,true); Simulink.sdi.view;

HDL 実装モデルの生成と HDL アルゴリズムの検証

Simscape HDL ワークフロー アドバイザーは、Simscape モデルを HDL コード生成用の HDL 互換の実装モデルに変換します。アドバイザーを開くには、モデルに対して関数sschdladvisorを実行します。

sschdladvisor('ee_buck_converter_dc_motor_hdl')

HDL 実装モデルを生成するには、[実装モデルの生成] タスクのドロップダウン リストで [実装モデルを生成] タスクを右クリックし、リストから [選択したタスクまで実行] を選択します。タスクが成功すると、HDL 実装モデル gmStateSpaceHDL_ee_buck_converter_dc_motor_ へのリンクが表示されます。

open_system('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA')

HDL 実装モデルが元の Simscape モデルと一致することを確認するために、状態空間検証モデルを生成します。[実装モデルを生成] タスクで [実装モデルの妥当性確認ロジックの生成] チェック ボックスをオンにし、[妥当性確認ロジックの許容誤差] を 1e-1 に設定します。次に、タスクを実行します。HDL 実装モデルの Simscape アルゴリズムに対する検証を参照してください。

HDL ワークフロー アドバイザー

HDL ワークフロー アドバイザーは、HDL コード生成および FPGA 設計のプロセスをサポートします。このアドバイザーを使用して以下のことを行います。

モデルに HDL コード生成との互換性があるか確認し、非互換の設定を修正。

hdlsetup('gmStateSpaceHDL_ee_buck_converter_dc_motor_')

HDL コード、テスト ベンチ、およびそのコードとテスト ベンチをビルドして実行するスクリプトを生成。

合成およびタイミングの解析を実行。

生成されたコードを SoC、FPGA、Speedgoat I/O モジュールに展開。

Speedgoat ターゲット コンピューターの FPGA ビットストリームの生成

HDL ワークフロー アドバイザーを使用した Simulink Real-Time インターフェイス モデルの生成

1. HDL 実装モデルを開き、実装モデルの HDL ワークフロー アドバイザーを開きます。

open_system('gmStateSpaceHDL_ee_buck_converter_dc_motor_')

モデル内のサブシステムに対して HDL ワークフロー アドバイザーを開くには、関数hdladvisorを使用します。

hdladvisor('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA')

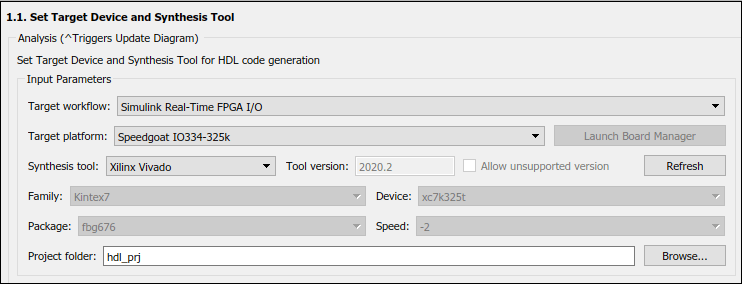

2. [ターゲット デバイスおよび合成ツールを設定] タスクで、[ターゲット ワークフロー] を [Simulink Real-Time FPGA I/O] として、[ターゲット プラットフォーム] を [Speedgoat IO334-325K] として指定します。

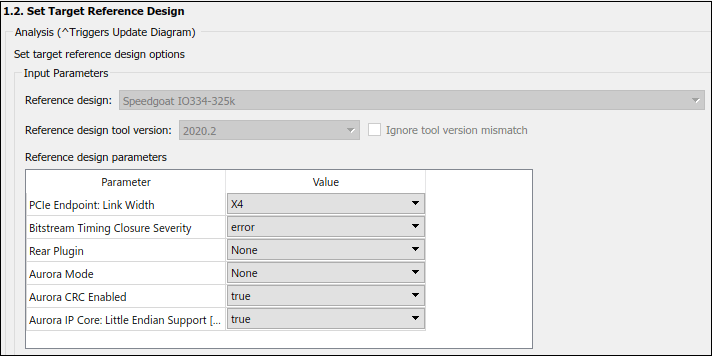

3. [ターゲットのリファレンス設計を設定] タスクで、パラメーター PCIe lanes に X4 の値を選択し、[このタスクを実行] ボタンをクリックします。

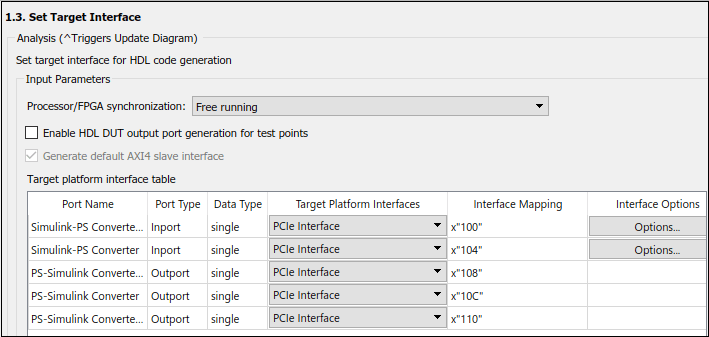

4. [ターゲット インターフェイスを設定] タスクで、入力および出力 single データ型端子を PCIe Interface にマッピングし、[このタスクを実行] ボタンをクリックします。

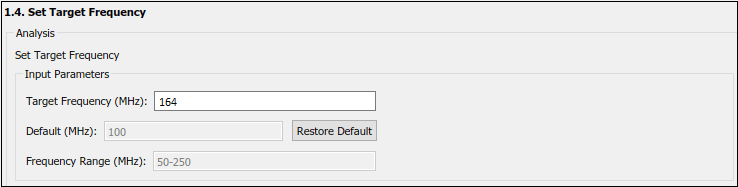

5. [ターゲット周波数を設定] タスクで [ターゲット周波数 (MHz)] の既定値は 100 に設定されます。このモデル例では、この値は 164 です。

6. [Simulink Real-Time インターフェイスの生成] タスクを右クリックして [選択したタスクまで実行] を選択して HDL IP コアおよび FPGA ビットストリームを生成します。

Simulink Real-Time インターフェイス モデルを生成するワークフロー スクリプトの実行

ワークフローの効率化と自動化のために、HDL ワークフロー アドバイザーの設定をスクリプトにエクスポートできます。このスクリプトは、コマンド ラインから実行する MATLAB® ファイルです。スクリプトを変更して実行するか、設定を HDL ワークフロー アドバイザーのユーザー インターフェイスにインポートすることができます。スクリプトを使用した HDL ワークフローの実行を参照してください。

この例では、HDL ワークフロー スクリプトの実行方法を説明します。Simulink Real-Time インターフェイス モデルを生成するには、次の MATLAB スクリプトを開いて実行します。

edit('hdlworkflow_dcmotor_IO334')

%-------------------------------------------------------------------------- % HDL Workflow Script % This script contains the model, target settings, interface mapping, and % the Workflow Configuration settings for generating HDL code for the HDL % implementation model generated for the Buck Converter Model with DC Motor % as load, and for deploying the code to the FPGA on board the Speedgoat % IO334-325K module. %-------------------------------------------------------------------------- %% Load the Model load_system('gmStateSpaceHDL_ee_buck_converter_dc_motor_'); %% Model HDL Parameters %% Set Model 'gmStateSpaceHDL_ee_buck_converter_dc_motor_' HDL parameters hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'AdaptivePipelining', 'on'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'FPToleranceValue', 1.0e-01); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'FloatingPointTargetConfiguration', hdlcoder.createFloatingPointTargetConfig('NativeFloatingPoint' ... , 'LatencyStrategy', 'Max') ... ); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'HDLSubsystem', 'gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'MaskParameterAsGeneric', 'on'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'Oversampling', 328); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'ReferenceDesign', 'Speedgoat IO334-325k'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'SynthesisTool', 'Xilinx Vivado'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'SynthesisToolChipFamily', 'Kintex7'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'SynthesisToolDeviceName', 'xc7k325t'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'SynthesisToolPackageName', 'fbg676'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'SynthesisToolSpeedValue', '-2'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'TargetDirectory', 'C:\BuckConverterDCMotor\hdl_prj\hdlsrc'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'TargetFrequency', 164); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'TargetPlatform', 'Speedgoat IO334-325k'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_', 'Workflow', 'Simulink Real-Time FPGA I/O'); % Set SubSystem HDL parameters hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA', 'AXI4SlaveIDWidth', '14'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA', 'ProcessorFPGASynchronization', 'Free running'); % Set Inport HDL parameters hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/DutyCycle', 'IOInterface', 'PCIe Interface'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/DutyCycle', 'IOInterfaceMapping', 'x"100"'); % Set Inport HDL parameters hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/step', 'IOInterface', 'PCIe Interface'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/step', 'IOInterfaceMapping', 'x"104"'); % Set Inport HDL parameters hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/Vin', 'IOInterface', 'PCIe Interface'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/Vin', 'IOInterfaceMapping', 'x"108"'); % Set Outport HDL parameters hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/voltage', 'IOInterface', 'PCIe Interface'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/voltage', 'IOInterfaceMapping', 'x"10C"'); % Set Outport HDL parameters hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/speed', 'IOInterface', 'PCIe Interface'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/speed', 'IOInterfaceMapping', 'x"110"'); % Set Outport HDL parameters hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/Vdc', 'IOInterface', 'PCIe Interface'); hdlset_param('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA/Vdc', 'IOInterfaceMapping', 'x"114"'); %% Workflow Configuration Settings % Construct the Workflow Configuration Object with default settings hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx Vivado','TargetWorkflow','Simulink Real-Time FPGA I/O'); % Specify the top level project directory hWC.ProjectFolder = 'C:\BuckConverterDCMotor\hdl_prj'; hWC.ReferenceDesignToolVersion = '2020.2'; hWC.IgnoreToolVersionMismatch = false; % Set Workflow tasks to run hWC.RunTaskGenerateRTLCodeAndIPCore = true; hWC.RunTaskCreateProject = true; hWC.RunTaskBuildFPGABitstream = true; hWC.RunTaskGenerateSimulinkRealTimeInterface = true; % Set properties related to 'RunTaskGenerateRTLCodeAndIPCore' Task hWC.GenerateIPCoreReport = true; % Set properties related to 'RunTaskCreateProject' Task hWC.Objective = hdlcoder.Objective.None; hWC.AdditionalProjectCreationTclFiles = ''; hWC.EnableIPCaching = true; % Set properties related to 'RunTaskBuildFPGABitstream' Task hWC.RunExternalBuild = false; hWC.EnableDesignCheckpoint = false; hWC.TclFileForSynthesisBuild = hdlcoder.BuildOption.Default; hWC.CustomBuildTclFile = ''; hWC.DefaultCheckpointFile = 'Default'; hWC.RoutedDesignCheckpointFilePath = ''; hWC.MaxNumOfCoresForBuild = ''; % Validate the Workflow Configuration Object hWC.validate; %% Run the workflow hdlcoder.runWorkflow('gmStateSpaceHDL_ee_buck_converter_dc_motor_/FPGA', hWC);

Speedgoat IO334-325k ターゲットへのビットストリームの展開

リアルタイム シミュレーション用の Simulink Real-Time インターフェイス モデルの準備

ワークフロー スクリプトを実行すると、RTL コードと IP コアが生成され、Vivado プロジェクトが作成され、FPGA ビットストリームがビルドされて、その後 Simulink Real-Time インターフェイス モデルが生成されます。

ハードウェアを初期化し、実行時に FPGA とのインターフェイスとなるために、FPGA サブシステムは、リアルタイム インターフェイス モデルで Speedgoat ドライバー ブロックに自動的に置き換えられます。

シングル レート モデルを得るために、モデルで残りの Rate Transition ブロックを必ずコメント アウトしてください。生成された Simulink Real-Time モデル内のすべてのブロックは、リアルタイム システムの CPU で実行されます。降圧コンバーターと DC モーターはビットストリームでプログラムされ、FPGA でより速いレートで実行されます。

ターゲット マシンへの接続とリアルタイム シミュレーションの実行

これで、Speedgoat リアルタイム ターゲット マシンにモデルを展開できるようになりました。Speedgoat リアルタイム ターゲット マシンがホスト コンピューターに接続されていて、電源が入っていることを確認します。

Simulink Real-Time エクスプローラーを使用してビットストリームをダウンロードします。Simulink Real-Time エクスプローラーを開くには、コマンド slrtExplorer を入力します。あるいは、Simulink ツールストリップの [リアルタイム] タブからエクスプローラーを開くことができます。

slrtExplorer

Simulink エディターに、speedgoat.tlc コード生成ターゲット用に構成されたモデルの [リアルタイム] タブが表示されます。Simulink の [リアルタイム] タブで [ターゲット コンピューターに接続] ボタンをクリックしてマシンに接続します。接続されたら、[ターゲットで実行] ボタンをクリックしてモデルを展開します。

Simulink Real-Time は Simulink Coder を使用してモデルから C コードを自動的に生成します。生成されたコードおよび FPGA 用のビットストリームがターゲット マシンにロードされ、モデルの実行が自動的に開始します。