このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

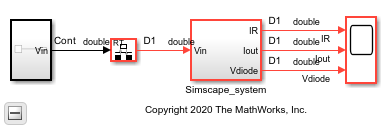

Speedgoat FPGA I/O モジュールへの Simscape モデルのハードウェアインザループ実装

この例では、Simscape™ 半波整流器モデルから FPGA ビットストリームを合成して生成し、そのビットストリームをハードウェアインザループ (HIL) 実装用に Speedgoat® FPGA I/O 334-325K ターゲットにダウンロードする方法を示します。

ハードウェアインザループ ワークフロー

Simscape HDL ワークフロー アドバイザーを使用して Simscape モデルから HDL 実装モデルを生成します。HDL 実装モデルは、Simscape アルゴリズムを HDL 互換のブロックに置き換える Simulink® モデルです。

HDL ワークフロー アドバイザーを使用して HDL 実装モデルの FPGA ビットストリームを生成します。

ハードウェアインザループ シミュレーション用に、Simulink Real-Time エクスプローラーを使用して Speedgoat FPGA I/O モジュールにビットストリームをダウンロードします。

半波整流器モデル

Simscape 半波整流器モデルを開きます。MATLAB® コマンド プロンプトで次のように入力します。

ModelName = 'sschdlexHalfWaveRectifierExample'; open_system(ModelName) set_param(ModelName, 'SimulationCommand', 'update');

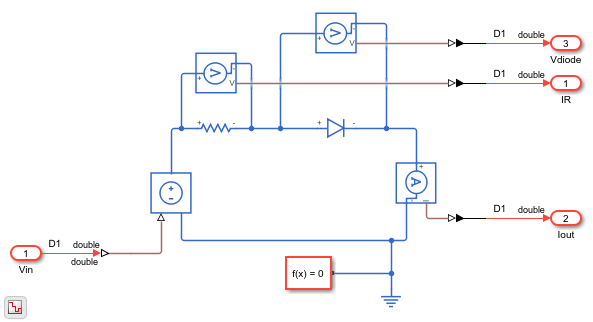

open_system([ModelName, '/Simscape_system'])

半波整流器は、線形ブロックである Resistor と、線形スイッチド システム ブロックである Diode で構成されます。入力端子と出力端子のインターフェイスにおいて、モデルには Simulink-PS Converter ブロックと PS-Simulink Converter ブロックがあります。ソルバー設定は、Simscape HDL ワークフロー アドバイザーと互換性をもつように構成されています。Solver Configuration ブロックの [ブロック パラメーター] ダイアログ ボックスを開くと、[ローカル ソルバーを使用] が選択されていて、Backward Euler が [ソルバー タイプ] として指定されています。Simscape ハードウェアインザループ ワークフロー入門を参照してください。

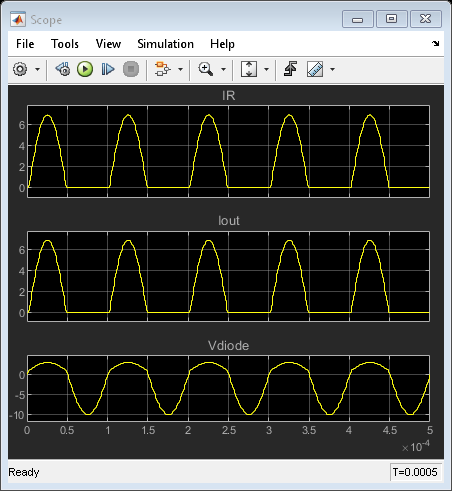

アルゴリズムの機能を確認するには、モデルをシミュレートします。

sim(ModelName)

open_system([ModelName, '/Scope'])

2. 関数 hdlsetup を使用して、Simscape モデルを HDL 互換性をもつように構成します。

hdlsetup('sschdlexHalfWaveRectifierExample')

HDL 実装モデルの生成

HDL 実装モデルを生成するには、以下を実行します。

1. Simscape HDL ワークフロー アドバイザーを開きます。

sschdladvisor('sschdlexHalfWaveRectifierExample')

2. HDL 実装モデルの機能を元の Simscape アルゴリズムと比較するには、[実装モデルを生成] ステップを選択し、次に [実装モデルの妥当性確認ロジックの生成] チェック ボックスを選択します。[妥当性確認ロジックの許容誤差] は 0.001 を使用します。[実装モデルを生成] ステップを右クリックし、[選択したタスクまで実行] を選択します。

アドバイザーにより、HDL 実装モデルと状態空間検証モデルが生成されます。HDL 実装モデルの機能を元の Simscape アルゴリズムと比較するには、状態空間検証モデルを開いてシミュレートします。このモデルの出力は、元の Simscape モデルと一致します。より系統的な検証については、HDL 実装モデルの Simscape アルゴリズムに対する検証を参照してください。

Simscape HDL ワークフロー アドバイザーのタスクも参照してください。

セットアップと構成

Speedgoat IO334-325K FPGA モジュールでは、Xilinx® Vivado® と "IP コアの生成" ワークフロー インフラストラクチャを使用します。HDL 実装モデルを Speedgoat I/O モジュールに展開する前に以下を実行します。

1. Xilinx Vivado のインストールとツール パスの設定

HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアにリストされている Xilinx® Vivado® の最新バージョンをインストールします。次に、関数hdlsetuptoolpathを使用して、インストールした Xilinx Vivado 実行可能ファイルへのツール パスを設定します。

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2022.1\bin\vivado.bat')

2. Speedgoat I/O Blockset と Speedgoat - HDL Coder Integration Package のインストール

Speedgoat I/O Blockset および Speedgoat - HDL Coder Integration Package をインストールします。オンラインで www.speedgoat.com/knowledge-center にある Speedgoat のドキュメンテーションを参照してください。

3. I/O モジュールの設定

リアルタイム シミュレーションでは、I/O モジュールを設定します。Xilinx HDL Software for Speedgoat I/O Modules を参照してください。

HDL ワークフロー アドバイザー

HDL ワークフロー アドバイザーは、HDL コード生成および FPGA 設計のプロセスをサポートします。このアドバイザーを使用して以下のことを行います。

モデルに HDL コード生成との互換性があるか確認し、非互換の設定を修正。

HDL コード、テスト ベンチ、およびそのコードとテスト ベンチをビルドして実行するスクリプトを生成。

合成およびタイミングの解析を実行。

生成されたコードを SoC、FPGA、Speedgoat I/O モジュールに展開。

HDL ワークフロー アドバイザーを開くには、関数hdladvisorを使用します。

hdladvisor('gmStateSpaceHDL_sschdlexHalfWaveRect/Simscape_system/HDL Subsystem')左側のペインには、関連タスクのグループを表すフォルダーが含まれます。フォルダーを展開してタスクを選択すると、そのタスクに関する情報が右側のペインに表示されます。右側のペインには、詳細設定パラメーターに対してタスクを実行するための単純なコントロールや、コードとテスト ベンチの生成を制御するオプション設定などが含まれます。各タスクの詳細については、そのタスクを右クリックし、[これはなに?] を選択します。HDL ワークフロー アドバイザーのご利用の前にを参照してください。

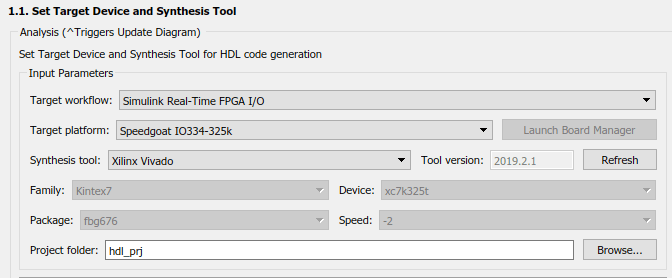

Speedgoat ターゲット コンピューターの FPGA ビットストリームの生成

1. HDL 実装モデルを開き、実装モデルの HDL ワークフロー アドバイザーを開きます。

open_system('sschdl/sschdlexHalfWaveRectifierExample/gmStateSpaceHDL_sschdlexHalfWaveRect')

hdladvisor('gmStateSpaceHDL_sschdlexHalfWaveRect/Simscape_system/HDL Subsystem')2. [ターゲット デバイスおよび合成ツールを設定] タスクで、[ターゲット ワークフロー] を Simulink Real-Time FPGA I/O、[ターゲット プラットフォーム] を Speedgoat IO334-325K と指定します。

3. [ターゲットのリファレンス設計を設定] タスクで、パラメーター PCIe lanes に x4 の値を選択し、[このタスクを実行] を選択します。

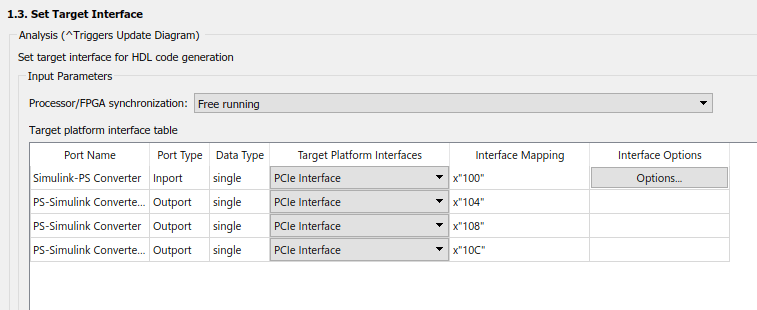

4. [ターゲット インターフェイスを設定] タスクで、入力および出力 single データ型端子を PCIe Interface にマッピングし、[このタスクを実行] を選択します。

5. [ターゲット周波数を設定] タスクで、[ターゲット周波数 (MHz)] を 100 と設定します。

6. [Simulink Real-Time インターフェイスの生成] タスクを右クリックして [選択したタスクまで実行] を選択します。HDL IP コアと FPGA ビットストリームが生成され、ビットストリームが Speedgoat ターゲット コンピューターの IO334 I/O モジュールにダウンロードされます。

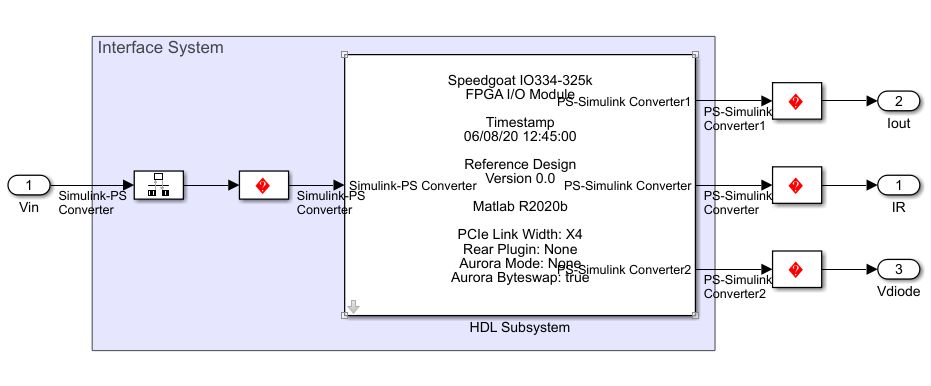

Simulink Real-Time インターフェイス モデルが "gm_gmStateSpaceHDL_sschdlexHalfWaveRectifierEx_slrt" という名前で生成されます。

ラピッド プロトタイピングのために、ワークフロー アドバイザーの設定をスクリプトにエクスポートできます。このスクリプトは、コマンド ラインから実行する MATLAB ファイルです。スクリプトを変更して実行するか、設定を HDL ワークフロー アドバイザーのユーザー インターフェイスにインポートすることができます。ワークフローを保存するには、HDL ワークフロー アドバイザーのユーザー インターフェイスで [ファイル]、[スクリプトへのエクスポート] を選択します。hdlworkflow_slrt_IO334.m としてファイルを保存します。

このファイルをインポートするには、HDL ワークフロー アドバイザーのユーザー インターフェイスで [ファイル]、[スクリプトからインポート] を選択します。[ワークフロー コンフィギュレーションのインポート] ダイアログ ボックスで、hdlworkflow_slrt_IO334.m ファイルを選択します。HDL ワークフロー アドバイザーで、インポートしたスクリプトに従ってタスクが更新されます。スクリプトを使用した HDL ワークフローの実行を参照してください。

Speedgoat IO334-325k ターゲットへのビットストリームの展開

1. ターゲットへの開発用コンピューターの接続

クロスオーバー ネットワーク ケーブルを使用して、開発用コンピューターをターゲットに接続します。Speedgoat ターゲット コンピューターの既定の IP アドレスは 192.168.7.5 です。開発用コンピューターとターゲット コンピューターの間の通信リンクは同じネットワークになければならないため、通信リンクの IP アドレスの値を 192.168.7.2 に設定します。

2. Simulink Real-Time エクスプローラーのセットアップと構成

Simulink Real-Time エクスプローラーを使用してビットストリームをダウンロードします。Simulink Real-Time エクスプローラーを開くには、コマンド slrtExplorer を入力します。あるいは、Simulink ツールストリップの [リアルタイム] タブからエクスプローラーを開くことができます。

slrtExplorer

Simulink エディターに、speedgoat.tlc コード生成ターゲット用に構成されたモデルの [リアルタイム] タブが表示されます。

a. Simulink Real-Time エクスプローラーの [ターゲットの構成] タブで、開発用コンピューターの設定を構成します。

[IP アドレス] を

192.168.7.5と設定するか、必要に応じてターゲット コンピューターのカスタムの IP アドレスを設定します。[名前] を

TargetPC1と設定するか、必要に応じてターゲット コンピューターのカスタムの名前を設定します。

b. 開発用コンピューターの設定を変更した場合は、[Change IP Address] ボタンをクリックして、対応する変更をターゲット コンピューターに適用します。

3. リアルタイム アプリケーションの作成

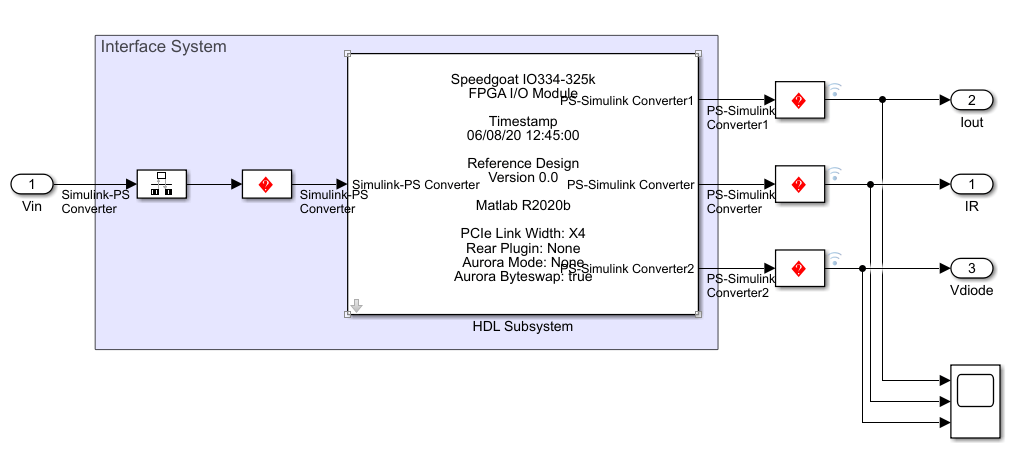

Simulink Real-Time インターフェイス モデルを開きます。Scope ブロックをモデルに追加し、出力に接続します。出力信号をログに記録し、シミュレーション データ インスペクターでシミュレーション結果を確認します。

4. リアルタイム アプリケーションのビルドと実行

[リアルタイム] タブで [ターゲットで実行] をクリックし、モデルをコンパイルして Speedgoat IO334-325k ターゲットにダウンロードします。

出力されたシミュレーション結果をシミュレーション データ インスペクターで確認します。ダウンロードしたモデルのシミュレーション結果は、元の Simscape モデルのシミュレーションと一致します。