HDL ワークフロー スクリプトを使用した Simscape 電力網連結コンバーター モデルの Speedgoat IO モジュールへの展開

この例では、Simscape™ でモデル化された、低電圧電力網に接続された三相 2 レベル電圧源コンバーターを Speedgoat® IO334 Simulink® プログラム可能 I/O モジュールに展開して、1 マイクロ秒 (us) のシミュレーション タイム ステップを実現する方法を示します。

サブサイクルの平均化方法を使用してコンバーターをモデル化することで、向上した分解能で PWM 信号を取得できます。最大 4 ns の分解能まで可能であり、スイッチング周波数が 100 kHz を超える最先端のパワー コンバーターをシミュレートできます。この例のスイッチング周波数は 20 kHz です。

この例では次の方法を示します。

Simscape HDL ワークフロー アドバイザーを使用して、Simscape モデルを HDL 互換の実装モデルに変換します。

HDL ワークフロー アドバイザーを使用して、IO334 モジュール用の HDL コードと

FPGAビットストリームを生成します。Simulink Real-Time™ を使用して、リアルタイム モデルを Speedgoat のリアルタイム ターゲット マシンに展開します。

最終的に、プラント モデルが FPGA で 1 us のタイム ステップで実行され、コントローラーがリアルタイム システムの CPU で 50 us のタイム ステップで実行されます。HDL コードと FPGA ビットストリームを生成するために、この例では、HDL ワークフロー スクリプトをコマンド ラインから実行する方法を示します。このワークフローはワークフロー アドバイザーのユーザー インターフェイスを使用して実行できます。詳細については、Speedgoat FPGA I/O モジュールへの Simscape モデルの FPGA ベースの HIL 展開を参照してください。

セットアップと構成

アルゴリズムを Speedgoat IO モジュールに展開する前に、以下を行います。

1. 生成された HDL コードを合成するには、HDL Coder™ を使用してコードを生成する前に、合成ツールのパスを設定します。たとえば、合成ツールが Xilinx® Vivado® の場合は、HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアに示されている Xilinx Vivado の最新バージョンをインストールします。

次に、関数hdlsetuptoolpathを使用して、インストールした Xilinx Vivado 実行可能ファイルへのツール パスを設定します。たとえば、次のコマンドは、インストールされた Vivado® Design Suite 2024.1 バッチ ファイルを指すように合成ツールのパスを設定します。

hdlsetuptoolpath("ToolName","Xilinx Vivado",... "ToolPath","C:\Xilinx\Vivado\2024.1\bin\vivado.bat")

2. リアルタイム シミュレーション用に、開発環境とターゲット コンピューターの設定を行います。Get Started with Simulink Real-Time (Simulink Real-Time)を参照してください。

3. Speedgoat I/O Blockset および Speedgoat - HDL Coder Integration Package をインストールするために、Speedgoat® カスタマー ポータル (www.speedgoat.com/extranet) にアクセスします。指示に従って Speedgoat I/O Blockset をダウンロードしてインストールします。

三相 2 レベル電圧源コンバーター モデル

三相 2 レベル コンバーター モデルを表示するには、次のコマンドを実行します。

open_system('sschdlexThreePhaseConverterWithGridExample')

このモデル例は、LC フィルターを介して低電圧電力網に接続された三相 2 レベル電圧源コンバーターで構成されています。コンバーターと電力網は回路ブレーカーで切断および接続できます。電力網側に対する低電圧の負荷と中電圧電力網に接続する変圧器があります。

最初の手順では、モデルを使用してデスクトップ シミュレーションで閉ループ制御を検証します。コントローラーは、同期基準座標系での電力網同期と PI 電流制御のための位相同期回路で構成されています。

2 番目の手順では、組み込みコントローラーの HIL テスト用にリアルタイム プラットフォームにモデルを展開できます。

モデルは FPGA で実行される部分と CPU でリアルタイムに実行される部分に分割されています。緑の FPGA サブシステム内の部分は FPGA で実行されます。このサブシステム外の部分は CPU でリアルタイムに実行されます。

open_system('sschdlexThreePhaseConverterWithGridExample/FPGA')

Simscape モデルのデスクトップ シミュレーションの実行

基本サンプル レートは、ハードウェアのターゲット周波数である 180 MHz の時間刻みに合わせて 1/(180e6) に設定されています。デスクトップ シミュレーションを高速化するには、基本サンプル レートの値を増やすことを検討できます。

Tbase = 1/(180e6);

回路ブレーカーを閉じるためのシミュレーションとステップ時間の設定

set_param('sschdlexThreePhaseConverterWithGridExample','StopTime','0.09'); set_param(['sschdlexThreePhaseConverterWithGridExample','/Step'],'Time','0.03');

モデルのデスクトップ シミュレーション

sim('sschdlexThreePhaseConverterWithGridExample')

Simulink データ インスペクターでの三相 2 レベル電圧源コンバーターの出力信号の表示

Simulink.sdi.clearAllSubPlots Simulink.sdi.setSubPlotLayout(2,1);

allIDs = Simulink.sdi.getAllRunIDs;

runID1 = allIDs(end);

run1 = Simulink.sdi.getRun(runID1);

run1.name = 'Desktop Simulation';

Vabc_grid = run1.getSignalsByName('Vabc_grid'); Iabc_conv = run1.getSignalsByName('Iabc_conv'); plotOnSubPlot(Vabc_grid.Children(1),1,1,true); plotOnSubPlot(Vabc_grid.Children(2),1,1,true); plotOnSubPlot(Vabc_grid.Children(3),1,1,true); plotOnSubPlot(Iabc_conv.Children(1),2,1,true); plotOnSubPlot(Iabc_conv.Children(2),2,1,true); plotOnSubPlot(Iabc_conv.Children(3),2,1,true);

Simulink.sdi.view;

HDL 実装モデルの生成

HDL コード生成との互換性のために、Simscape HDL ワークフロー アドバイザーを実行して HDL 実装モデルを生成します。

Simscape ソルバーは、サンプル ステップごとに 1 回反復して実行するように設定されています。Simscape HDL ワークフロー アドバイザーは、確定的なリアルタイム動作のために、次の手順でこのソルバー設定を使用します。

平均化スイッチ モデルではソルバーの反復を 1 に設定できます。

set_param(['sschdlexThreePhaseConverterWithGridExample','/FPGA/Solver Configuration'],'DoFixedCost','on') set_param(['sschdlexThreePhaseConverterWithGridExample','/FPGA/Solver Configuration'],'MaxNonlinIter','1')

sschdladvisor を高速化するために、モデルのサンプル時間を減らします。シミュレーション時にワークフロー アドバイザーですべてのスイッチング モードが確実に取得されるように、回路ブレーカーが閉じる時間を適応させます。

set_param('sschdlexThreePhaseConverterWithGridExample','StopTime','0.002'); set_param(['sschdlexThreePhaseConverterWithGridExample','/Step'],'Time','0.001');

アドバイザーを開くには、モデルに対して関数sschdladvisorを実行します。

sschdladvisor('sschdlexThreePhaseConverterWithGridExample')

実装モデルを生成するには、Simscape HDL ワークフロー アドバイザーで、タスクの既定の設定を維持し、タスクを実行します。[すべて実行] ボタンをクリックして、アドバイザーでタスクを実行します。[実装モデルを生成] タスクで、生成されたモデルへのリンクを確認します。このモデルは元のモデルと同じ名前をもち、接頭辞 gmStateSpaceHDL_ が付きます。

シミュレーションとステップ時間を元の値に設定します。

set_param('sschdlexThreePhaseConverterWithGridExample','StopTime','0.09'); set_param(['sschdlexThreePhaseConverterWithGridExample','/Step'],'Time','0.03');

HDL コード生成用の実装モデルの準備

実装モデルを開くには、[実装モデルを生成] タスクのリンクをクリックします。

open_system('gmStateSpaceHDL_sschdlexThreePhaseConverter')

set_param('gmStateSpaceHDL_sschdlexThreePhaseConverter','StopTime','0.09'); set_param(['gmStateSpaceHDL_sschdlexThreePhaseConverter','/Step'],'Time','0.03');

このモデルには、元の三相 2 レベル電圧源コンバーター モデルの線形スイッチド システム Simulink 置換モデルが含まれています。Simscape モデルが置き換えられたことがわかります。

open_system('gmStateSpaceHDL_sschdlexThreePhaseConverter/FPGA')

実装モデルは、Simscape サブシステムを、状態空間計算を実行する HDL 互換のアルゴリズムに置き換えます。このサブシステム内を移動すると、状態空間方程式をモデル化するいくつかの遅延、加算器、および Matrix Multiply ブロックが確認されます。このサブシステム内の From ブロックと Goto ブロックは、元のモデルと同じ入力を HDL Subsystem に提供します。

open_system('gmStateSpaceHDL_sschdlexThreePhaseConverter/FPGA/HDL Subsystem/HDL Algorithm')

HDL 実装モデルのデスクトップ シミュレーションの実行と HDL アルゴリズムの検証

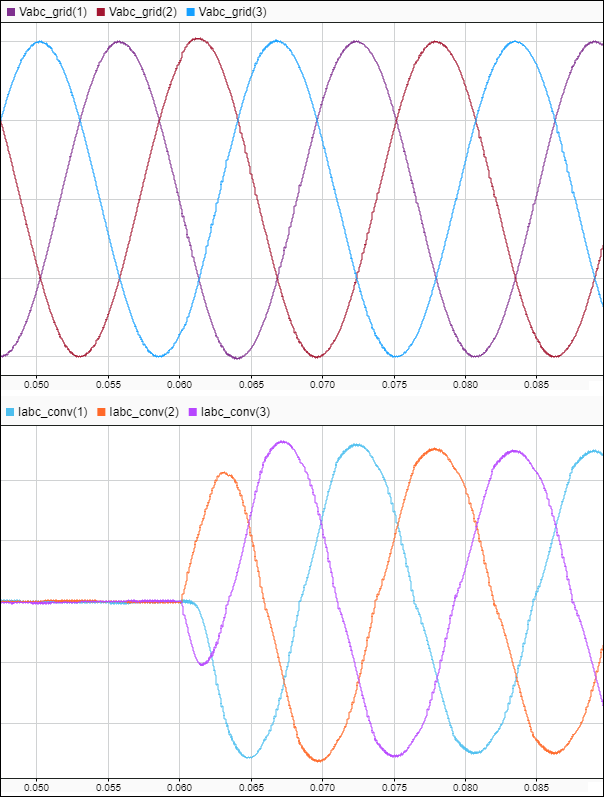

三相 2 レベル電圧源コンバーターの線形スイッチド システムの状態空間モデルを Simulink でシミュレートし、信号をシミュレーション データ インスペクターに表示することができます。実行の比較により、数値結果が元の Simscape モデルと一致することが示されます。

HDL 実装モデルをシミュレートします。

sim('gmStateSpaceHDL_sschdlexThreePhaseConverter')

Simulink データ インスペクターで三相 2 レベル電圧源コンバーター Simscape モデルの出力信号を表示します。

Simulink.sdi.clearAllSubPlots Simulink.sdi.setSubPlotLayout(2,1);

allIDs = Simulink.sdi.getAllRunIDs;

runID1 = allIDs(end);

run2 = Simulink.sdi.getRun(runID1);

run2.name = 'HDL Model Simulation';

Vabc_grid = run2.getSignalsByName('Vabc_grid'); Iabc_conv = run2.getSignalsByName('Iabc_conv'); plotOnSubPlot(Vabc_grid.Children(1),1,1,true); plotOnSubPlot(Vabc_grid.Children(2),1,1,true); plotOnSubPlot(Vabc_grid.Children(3),1,1,true); plotOnSubPlot(Iabc_conv.Children(1),2,1,true); plotOnSubPlot(Iabc_conv.Children(2),2,1,true); plotOnSubPlot(Iabc_conv.Children(3),2,1,true);

Simulink.sdi.view;

HDL 実装モデルが元の Simscape モデルと一致することを確認するために、状態空間検証モデルを生成します。[実装モデルを生成] タスクで、[実装モデルの妥当性確認ロジックの生成] チェック ボックスをオンにして、このタスクを実行します。モデルをシミュレートしてもアサーションは表示されませんが、これは、数値結果が一致することを示します。HDL 実装モデルの Simscape アルゴリズムに対する検証を参照してください。

HDL ワークフロー アドバイザー

HDL ワークフロー アドバイザーは、HDL コード生成および FPGA 設計のプロセスをサポートします。このアドバイザーを使用して以下のことを行います。

モデルに HDL コード生成との互換性があるか確認し、非互換の設定を修正。

HDL コード、テスト ベンチ、およびそのコードとテスト ベンチをビルドして実行するスクリプトを生成。

合成およびタイミングの解析を実行し、生成されたコードを SoC、FPGA、Speedgoat I/O のモジュールに展開。

モデル内の FPGA サブシステム用にアドバイザーを実行します。モデル内のサブシステム用に HDL ワークフロー アドバイザーを開くには、関数hdladvisorを使用します。以下に例を示します。

hdladvisor('gmStateSpaceHDL_sschdlexThreePhaseConverter/FPGA')

アドバイザー内のタスクの詳細については、該当するタスクを右クリックして [これはなに?] を選択します。HDL ワークフロー アドバイザーのご利用の前にを参照してください。

Simulink Real-Time インターフェイス モデルを生成するワークフロー スクリプトの実行

ワークフローの効率化と自動化のために、HDL ワークフロー アドバイザーの設定をスクリプトにエクスポートできます。このスクリプトは、コマンド ラインから実行する MATLAB® ファイルです。スクリプトを変更して実行するか、設定を HDL ワークフロー アドバイザーのユーザー インターフェイスにインポートすることができます。スクリプトを使用した HDL ワークフローの実行を参照してください。

この例では、HDL ワークフロー スクリプトの実行方法を説明します。Simulink Real-Time インターフェイス モデルを生成するには、次の MATLAB スクリプトを開いて実行します。

edit('hdlworkflow_IO334')

%% ------------------------------------------------------------------------ % This script contains the model, target settings, interface mapping, and % the Workflow Configuration settings for generating HDL code for the HDL % implementation model generated for the three-phase two-level voltage source % converter model, and for deploying the code to the FPGA on board the % Speedgoat IO334-325K module. %% ----------------------------------------------------------------------- % Make the model ready for HDL code generation % Set all data type conversion blocks to type single (except the % conversions for the analog output signals. DataTypeConversionBlocks = Simulink.findBlocksOfType([HDLModelName,'/FPGA'],'DataTypeConversion',Simulink.FindOptions('SearchDepth',1)); for i = 1:length(DataTypeConversionBlocks) BlockName = get_param(DataTypeConversionBlocks(i),'Name'); if ~any(strcmp(BlockName,{'Data Type Conversion DAC1','Data Type Conversion DAC2'})) set_param([HDLModelName,'/FPGA/',BlockName],'OutDataTypeStr','single'); end end set_param([HDLModelName,'/Data Type Conversion Vg'],'OutDataTypeStr','single'); set_param([HDLModelName,'/Data Type Conversion Breaker'],'OutDataTypeStr','single'); % Set the base sample time to 1/(180e6) (equal to a clock tick at 180MHz target % frequency). Note: The base rate determines the resolution of the PWM % signal when running the model on hardware. Tbase = 1/180e6; % Model HDL parameters % ------------------------------------------------------------------------- % Set the model HDL parameters hdlset_param(HDLModelName, 'FloatingPointTargetConfiguration', hdlcoder.createFloatingPointTargetConfig('NativeFloatingPoint', 'LatencyStrategy', 'MAX')); hdlset_param(HDLModelName, 'HDLSubsystem', [HDLModelName,'/FPGA']); hdlset_param(HDLModelName, 'Oversampling',1); hdlset_param(HDLModelName, 'ScalarizePorts', 'DUTLevel'); hdlset_param(HDLModelName, 'TargetFrequency', 180); hdlset_param(HDLModelName, 'Workflow', 'Simulink Real-Time FPGA I/O'); hdlset_param(HDLModelName, 'TargetPlatform', 'Speedgoat IO334-325k'); hdlset_param(HDLModelName, 'TargetDirectory', 'c:\hdl_prj\hdlsrc'); hdlset_param(HDLModelName,'ResetType','Synchronous') hdlset_param(HDLModelName, 'AdaptivePipelining', 'on'); hdlset_param(HDLModelName, 'ReferenceDesignParameter', {'PCIe_Link_Width','X4','RearPlugin','None','AuroraMode','None','AuroraByteswap','true'}); % Block ram options hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm/State Update/Multiply Input'], 'UseRAM', 'on'); hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm/State Update/Multiply State'], 'UseRAM', 'on'); % Set input and output pipeline registers hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm'], 'ConstrainedOutputPipeline', 2); hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm'], 'InputPipeline', 2); hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm'], 'OutputPipeline', 2); hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm/Mode Selection'], 'ConstrainedOutputPipeline', 2); hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm/Mode Selection'], 'OutputPipeline', 2); hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm/Output'], 'ConstrainedOutputPipeline', 2); hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm/Output'], 'OutputPipeline', 2); hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm/State Update'], 'ConstrainedOutputPipeline', 2); hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm/State Update'], 'OutputPipeline', 2); % Enable flatten hyrarchy hdlset_param([HDLModelName,'/FPGA'], 'FlattenHierarchy', 'on'); % Set the code generation options for the MATLAB function to "data path" hdlset_param([HDLModelName,'/FPGA/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector'], 'Architecture', 'MATLAB Datapath'); % We define the hardware interfaces for all input and output ports to the % FPGA subsystem % Set inport HDL parameters hdlset_param([HDLModelName,'/FPGA/modWave'], 'IOInterface', 'PCIe Interface'); hdlset_param([HDLModelName,'/FPGA/modWave'], 'IOInterfaceMapping', 'x"100"'); hdlset_param([HDLModelName,'/FPGA/Period'], 'IOInterface', 'PCIe Interface'); hdlset_param([HDLModelName,'/FPGA/Period'], 'IOInterfaceMapping', 'x"114"'); hdlset_param([HDLModelName,'/FPGA/Enable'], 'IOInterface', 'PCIe Interface'); hdlset_param([HDLModelName,'/FPGA/Enable'], 'IOInterfaceMapping', 'x"118"'); hdlset_param([HDLModelName,'/FPGA/DeadBand'], 'IOInterface', 'PCIe Interface'); hdlset_param([HDLModelName,'/FPGA/DeadBand'], 'IOInterfaceMapping', 'x"11C"'); hdlset_param([HDLModelName,'/FPGA/Grid Voltage'], 'IOInterface', 'PCIe Interface'); hdlset_param([HDLModelName,'/FPGA/Grid Voltage'], 'IOInterfaceMapping', 'x"120"'); hdlset_param([HDLModelName,'/FPGA/breaker'], 'IOInterface', 'PCIe Interface'); hdlset_param([HDLModelName,'/FPGA/breaker'], 'IOInterfaceMapping', 'x"134"'); % Set outport HDL parameters hdlset_param([HDLModelName,'/FPGA/PCIe_FrameData'], 'IOInterface', 'PCIe Interface'); hdlset_param([HDLModelName,'/FPGA/PCIe_FrameData'], 'IOInterfaceMapping', 'x"1000"'); hdlset_param([HDLModelName,'/FPGA/DAC_1'], 'IOInterface', 'IO334 AO Data [0:15]'); hdlset_param([HDLModelName,'/FPGA/DAC_1'], 'IOInterfaceMapping', 'Channel 01'); hdlset_param([HDLModelName,'/FPGA/DAC_2'], 'IOInterface', 'IO334 AO Data [0:15]'); hdlset_param([HDLModelName,'/FPGA/DAC_2'], 'IOInterfaceMapping', 'Channel 02'); hdlset_param([HDLModelName,'/FPGA/DAC_3'], 'IOInterface', 'IO334 AO Data [0:15]'); hdlset_param([HDLModelName,'/FPGA/DAC_3'], 'IOInterfaceMapping', 'Channel 03'); hdlset_param([HDLModelName,'/FPGA/DAC_5'], 'IOInterface', 'IO334 AO Data [0:15]'); hdlset_param([HDLModelName,'/FPGA/DAC_5'], 'IOInterfaceMapping', 'Channel 05'); hdlset_param([HDLModelName,'/FPGA/DAC_6'], 'IOInterface', 'IO334 AO Data [0:15]'); hdlset_param([HDLModelName,'/FPGA/DAC_6'], 'IOInterfaceMapping', 'Channel 06'); hdlset_param([HDLModelName,'/FPGA/DAC_7'], 'IOInterface', 'IO334 AO Data [0:15]'); hdlset_param([HDLModelName,'/FPGA/DAC_7'], 'IOInterfaceMapping', 'Channel 07'); hdlset_param([HDLModelName,'/FPGA/DAC trigger 1_8'], 'IOInterface', 'IO334 AO Trigger [0:1]'); hdlset_param([HDLModelName,'/FPGA/DAC trigger 1_8'], 'IOInterfaceMapping', 'Channel 01 to 08'); %% Workflow Configuration Settings % Construct the Workflow Configuration Object with default settings hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx Vivado','TargetWorkflow','Simulink Real-Time FPGA I/O'); % Specify the top level project directory (make sure to define a short % specific path) hWC.ProjectFolder = 'c:/hdl_prj'; hWC.IgnoreToolVersionMismatch = true; % Set properties related to 'RunTaskCreateProject' Task hWC.Objective = hdlcoder.Objective.SpeedOptimized; % Set Workflow tasks to run hWC.RunTaskGenerateRTLCodeAndIPCore = true; hWC.RunTaskCreateProject = true; hWC.RunTaskBuildFPGABitstream = true; hWC.RunTaskGenerateSimulinkRealTimeInterface = true; %% Run the workflow hdlcoder.runWorkflow([HDLModelName,'/FPGA'], hWC); %% Get the model ready for deployment on the Speedgoat real-time target machine % Get the name of the generate real-time model SLRTModelName = ['gm_',HDLModelName,'_slrt']; % Comment through all rate transition blocks. The entire CPU model runs at % a time step of 50us. The rate transitions between the FPGA and CPU model % happen implicitly through the CPU read and write operations. RateTransitionBlocks = Simulink.findBlocksOfType(SLRTModelName,'RateTransition',Simulink.FindOptions('SearchDepth',1)); for i = 1:length(RateTransitionBlocks) BlockName = get_param(RateTransitionBlocks(i),'Name'); if ~any(strcmp(BlockName,{'Data Type Conversion DAC1','Data Type Conversion DAC2'})) set_param([SLRTModelName,'/',BlockName],'Commented','through'); end end % Uncomment the subsystem for data logging on the real-time CPU set_param([SLRTModelName,'/CPU Signal Logging'],'Commented','off');

リアルタイム シミュレーション用の Simulink Real-Time インターフェイス モデルの準備

ワークフロー スクリプトを実行すると、RTL コードと IP コアが生成され、Vivado プロジェクトが作成され、FPGA ビットストリームがビルドされて、その後 Simulink Real-Time インターフェイス モデルが生成されます。

Speedgoat リアルタイム ターゲット マシンにモデルを展開する前に、リアル タイム テスト用にモデルを準備します。

generated_model = get_param(gcs,'Name');

% comment through all rate transition blocks RateTransitionBlocks = Simulink.findBlocksOfType(generated_model,'RateTransition',Simulink.FindOptions('SearchDepth',1)); for i = 1:length(RateTransitionBlocks) BlockName = get_param(RateTransitionBlocks(i),'Name'); if ~any(strcmp(BlockName,{'Data Type Conversion DAC1','Data Type Conversion DAC2'})) set_param([generated_model,'/',BlockName],'Commented','through'); end end

% uncomment the subsystem for logging set_param([generated_model,'/CPU Signal Logging'],'Commented','off');

ターゲット マシンへの接続とリアルタイム シミュレーションの実行

これで、Speedgoat リアルタイム ターゲット マシンにモデルを展開できるようになりました。三相 2 レベル電圧源コンバーター モデルは、IO334 上の FPGA に自動的に読み込まれます。

Speedgoat リアルタイム ターゲット マシンに接続します。

tg = slrealtime; connect(tg);

モデルをビルドしてターゲット マシンにダウンロードします。

model = 'generated_model'; open_system(model); modelSTF = getSTFName(tg); set_param(model,"SystemTargetFile",modelSTF) set_param(model,'FixedStep','.01'); evalc('slbuild(model)');

モデルの実行を開始します。

load(tg,model); start(tg);

while strcmp(tg.status,'running') pause(10); end

ファイルのログ ブロックは、ターゲット マシンの SSD 上に信号を保存します。モデルが停止すると、データはホスト コンピューターに自動的にアップロードされます。このデータはシミュレーション データ インスペクターで可視化されます。リアルタイム シミュレーションの結果が元の Simscape モデルと一致することを確認できます。

% Display grid voltage and converter current in SDI

Simulink.sdi.clearAllSubPlots

Simulink.sdi.setSubPlotLayout(2,1);

allIDs = Simulink.sdi.getAllRunIDs;

runID1 = allIDs(end);

run3 = Simulink.sdi.getRun(runID1);

run3.name = 'Real-Time Simulation';

Vabc_grid = run3.getSignalsByName('Vabc_grid'); Iabc_conv = run3.getSignalsByName('Iabc_conv'); plotOnSubPlot(Vabc_grid.Children(1),1,1,true); plotOnSubPlot(Vabc_grid.Children(2),1,1,true); plotOnSubPlot(Vabc_grid.Children(3),1,1,true); plotOnSubPlot(Iabc_conv.Children(1),2,1,true); plotOnSubPlot(Iabc_conv.Children(2),2,1,true); plotOnSubPlot(Iabc_conv.Children(3),2,1,true);

Simulink.sdi.view;

あるいは、IO334 のアナログ出力で信号を測定できます。