Speedgoat Simulink プログラム可能 I/O モジュール向けの IP コアの生成ワークフロー

HDL Coder™ は [IP コアの生成] ワークフロー インフラストラクチャを使用して、Xilinx® Vivado® をサポートする Speedgoat® Simulink® プログラム可能 I/O モジュール向けの再利用可能な HDL IP コアを生成します。このワークフローでは、ターゲット インターフェイス構成および指定するコード ジェネレーターの設定が表示される IP コア レポートが生成されます。IP コアを組み込みシステム統合環境に追加して、さらに大規模な設計に統合できます。カスタム IP コアの生成を参照してください。

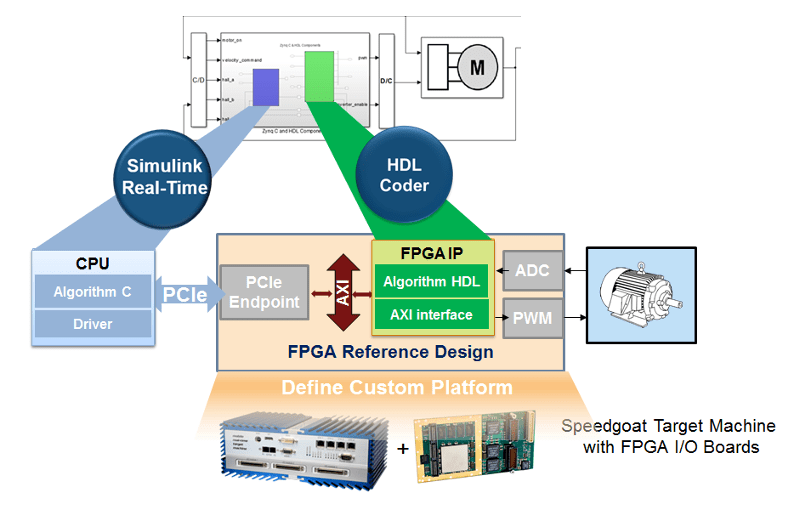

次の図は、ソフトウェアが AXI インターフェイスをもつ IP コアを生成する方法および IP コアを FPGA リファレンス設計に統合する方法を示しています。

サポートされる I/O モジュール

HDL Coder が [Simulink Real-Time FPGA I/O] ワークフローでサポートする I/O モジュールの詳細については、HDL ワークフロー アドバイザーでの Speedgoat FPGA のサポートを参照してください。

IP コアの生成ワークフロー

このワークフローの主な機能は次のとおりです。

合成ツールとして Xilinx Vivado を使用します。

再利用可能で、共有可能な IP コアを生成します。IP コアは、RTL コード、C ヘッダー ファイルおよび IP コア定義ファイルをパッケージ化します。

IP コアを Speedgoat リファレンス設計に統合するためのプロジェクトを作成します。

FPGA ビットストリームを生成して、ビットストリームをターゲット ハードウェアにダウンロードします。

FPGA ビットストリームの作成後、ワークフローは Simulink Real-Time™ モデルを生成します。このモデルは、FPGA のプログラミングを行い、リアルタイム実行中に I/O モジュールと PCIe バスを介して通信を行うブロックを含むインターフェイス サブシステム モデルです。

制限

IP Core Generation ワークフローは以下をサポートしません。

[クロック イネーブルを使用しない汎用 RAM]に設定されている [RAM アーキテクチャ]。IP コアと AXI インターフェイスに異なるクロックを使用。

IPCore_ClkおよびAXILite_ACLKは同期していて、同じクロック ソースに接続されていなければなりません。IPCore_RESETNおよびAXILite_ARESETNは、同じリセット ソースに接続されていなければなりません。グローバル リセット信号の IP コア クロック領域への同期を参照してください。

参考

トピック

- HDL ワークフロー アドバイザーでの Speedgoat FPGA のサポート

- Speedgoat Simulink プログラム可能 I/O モジュールでの FPGA プログラミングと構成

- カスタム IP コアの生成