このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

HDL ワークフロー スクリプトを使用した Simscape 降圧コンバーター モデルの Speedgoat IO モジュールへの展開

この例では、Simscape™ 降圧コンバーター モデルを Speedgoat IO334 Simulink® プログラム可能 I/O モジュールに展開し、そのモデルをわずか 1 マイクロ秒のサンプル ステップ サイズでリアルタイムに実行する方法を説明します。例では、DCDC コンバーターのトポロジを使用して、Speedgoat リアルタイム ターゲット マシン上でのハードウェアインザループ (HIL) シミュレーション用にパワー エレクトロニクス コンバーター モデルを準備する方法が示されます。

このワークフローを使用するには、以下を行います。

Simscape HDL ワークフロー アドバイザーを使用して、モデルを HDL 互換の実装モデルに変換します。

HDL ワークフロー アドバイザーを使用して、IO334 モジュール用の HDL コードと FPGA ビットストリームを生成します。

Simulink Real-Time を使用して、リアルタイム モデルを Speedgoat のリアルタイム ターゲット マシンに展開します。

モデルは、HDL コード生成まではサンプル時間 1 us で実行され、その後は 50 us で、CPU でリアルタイムに実行されます。HDL コードと FPGA ビットストリームを生成するために、例では、HDL ワークフロー スクリプトをコマンド ラインから実行する方法を示します。ワークフロー アドバイザーのユーザー インターフェイスを使用してこのワークフローを実行する方法を示す例については、Speedgoat FPGA I/O モジュールへの Simscape モデルのハードウェアインザループ実装を参照してください。

セットアップと構成

アルゴリズムを Speedgoat IO モジュールに展開する前に、以下を行います。

1. HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアにリストされている Xilinx® Vivado® の最新バージョンをインストールします。

次に、関数hdlsetuptoolpathを使用して、インストールした Xilinx Vivado 実行可能ファイルへのツール パスを設定します。

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2019.2\bin\vivado.bat')

2. リアルタイム シミュレーション用に、開発環境とターゲット コンピューターの設定を行います。Get Started with Simulink Real-Time (Simulink Real-Time)を参照してください。

3. Speedgoat ライブラリおよび Speedgoat HDL Coder Integration Package をインストールします。Install Speedgoat HDL Coder Integration Packages を参照してください。

降圧コンバーター モデル

降圧コンバーター モデルを表示するには、次のコマンドを実行します。

open_system('sschdlexBuckConverterModel')

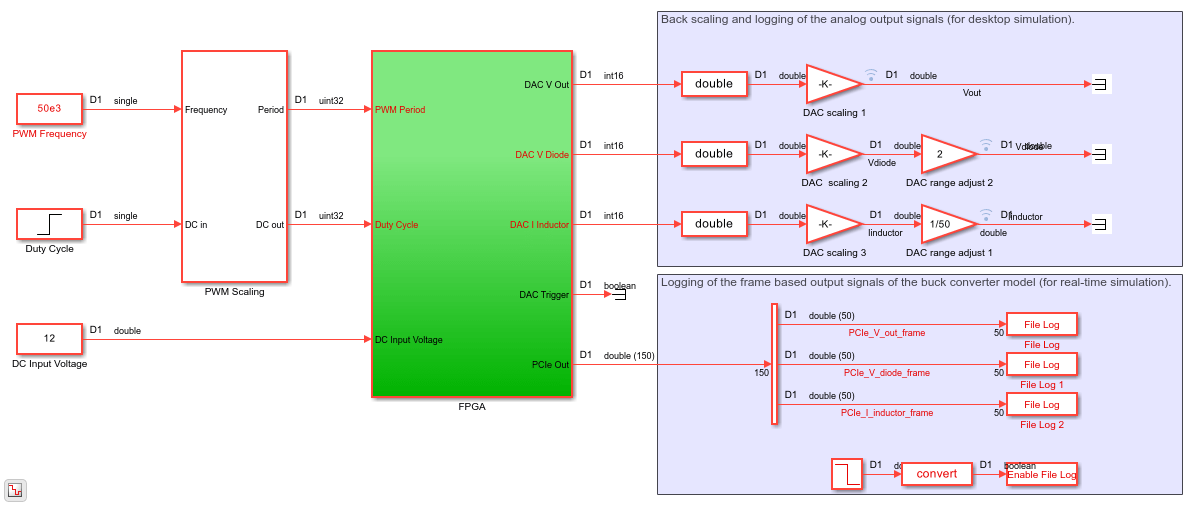

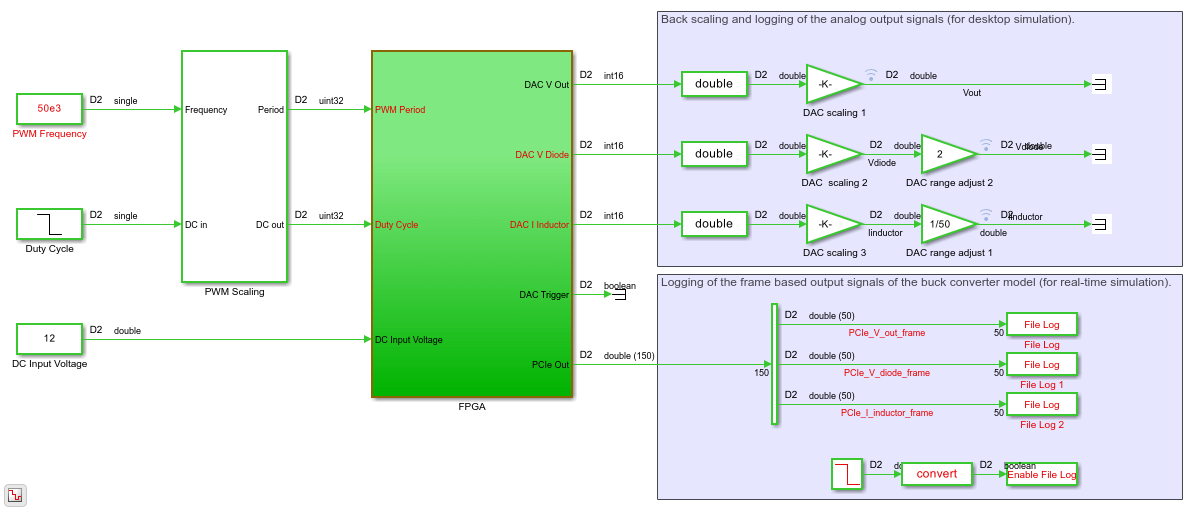

このモデルはリアルタイム展開用に変更され、sschdlex_IO334_BuckConverter という名前で保存されています。このモデルは、FPGA で実行される部分と CPU で実行される部分に分割されています。緑の FPGA サブシステム内の部分は FPGA で実行されます。このサブシステム外の部分は CPU でリアルタイムに実行されます。

open_system('sschdlex_IO334_BuckConverter')

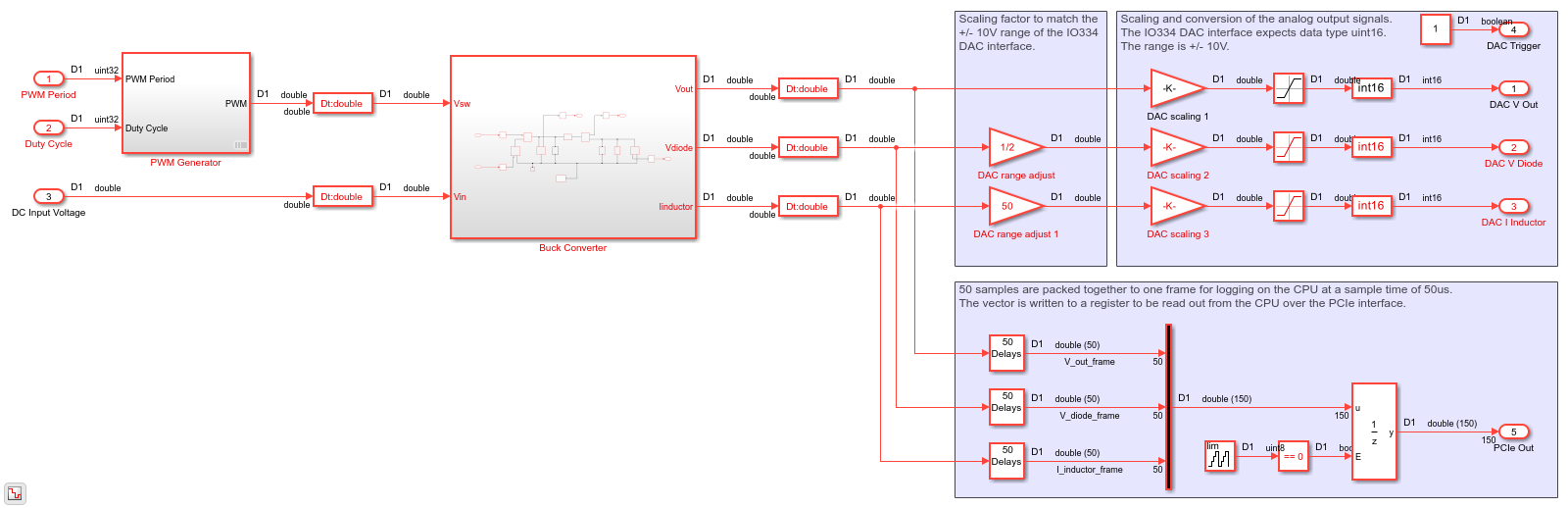

PWM 発生器と降圧コンバーターを含む緑の FPGA サブシステム内にあるブロック用に、VHDL コードを生成します。このコードはその後、IO334 モジュール搭載の FPGA に展開されます。サブシステムの出力は DAC インターフェイスにマッピングされます。Buck Converter サブシステムからの出力信号は 10V の範囲内でスケーリングされ、uint16 データ型を使用するように変換されます。CPU での出力信号をログに記録するために、50 個のサンプルが 1 つのフレームにパックされます。

open_system('sschdlex_IO334_BuckConverter/FPGA')

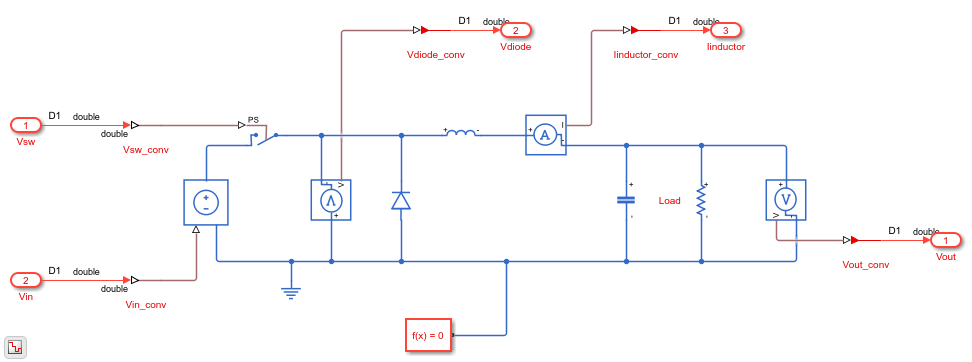

降圧コンバーター モデルを確認するには、Buck Converter サブシステムをダブルクリックします。降圧コンバーターは、出力において入力電圧を降下させるパワー コンバーター モデルです。出力における電圧は、デューティ比 D によって降下します。出力電圧 Vout は、Vin/D として計算されます。

open_system('sschdlex_IO334_BuckConverter/FPGA/Buck Converter')

Simscape モデルのデスクトップ シミュレーションの実行

シミュレーション入力は、0.2 から 0.8 までのデューティ比ステップ波形です。DC 入力電圧、PWM 周波数、およびデューティ比を含む入力信号が、モデルの最上位レベルで生成されます。Simscape モデルのサンプル時間は 1us に設定されています。信号のログがモデルの最上位レベルで有効になっています。

sim('sschdlex_IO334_BuckConverter')

HDL 実装モデルの生成

HDL コード生成との互換性のために、Simscape HDL ワークフロー アドバイザーを実行して HDL 実装モデルを生成します。

Simscape ソルバーは、サンプル ステップごとに 2 回反復して実行するように設定されています。Simscape HDL ワークフロー アドバイザーは、確定的なリアルタイム動作のために、次の手順でこのソルバー設定を使用します。

set_param('sschdlex_IO334_BuckConverter/FPGA/Buck Converter/Solver Configuration','DoFixedCost','on')

アドバイザーを開くには、モデルに対して関数sschdladvisorを実行します。

sschdladvisor('sschdlex_IO334_BuckConverter')

実装モデルを生成するには、Simscape HDL ワークフロー アドバイザーで、タスクの既定の設定を維持し、タスクを実行します。[すべて実行] ボタンをクリックして、アドバイザーでタスクを実行します。[実装モデルを生成] タスクでモデルへのリンクを確認します。このモデルは元のモデルと同じ名前をもち、接頭辞 gmStateSpaceHDL_ が付きます。

HDL コード生成用の実装モデルの準備

実装モデルを開くには、[実装モデルを生成] タスクのリンクをクリックします。

open_system('gmStateSpaceHDL_sschdlex_IO334_BuckConverte');

このモデルには、元の降圧コンバーター モデルの線形スイッチド システム Simulink 置換モデルが含まれています。Simscape モデルが置き換えられたことがわかります。

open_system('gmStateSpaceHDL_sschdlex_IO334_BuckConverte/FPGA/Buck Converter');

実装モデルは、Simscape サブシステムを、状態空間計算を実行する HDL 互換のアルゴリズムに置き換えます。このサブシステム内を移動すると、状態空間方程式をモデル化するいくつかの遅延、加算器、および Matrix Multiply ブロックが確認されます。このサブシステム内の From ブロックと Goto ブロックは、元のモデルと同じ入力を HDL Subsystem に提供します。

open_system('gmStateSpaceHDL_sschdlex_IO334_BuckConverte/FPGA/Buck Converter/HDL Subsystem/HDL Algorithm')

降圧コンバーター出力信号のデータ型は、HDL コード生成用に単精度浮動小数点に設定されています。

set_param('gmStateSpaceHDL_sschdlex_IO334_BuckConverte/FPGA/Signal Specification','OutDataTypeStr','single');

HDL 実装モデルのデスクトップ シミュレーションの実行と HDL アルゴリズムの検証

降圧コンバーターの線形スイッチド システムの状態空間モデルを Simulink でシミュレートし、信号をシミュレーション データ インスペクターに表示することができます。実行の比較により、数値結果が一致することが示されます。

HDL 実装モデルをシミュレートします。

sim('gmStateSpaceHDL_sschdlex_IO334_BuckConverte')

Warning: Unable to resolve the name 'CloneDetector.ExclusionEditorUIService.getInstance'.

HDL 実装モデルが元の Simscape モデルと一致することを確認するために、状態空間検証モデルを生成します。[実装モデルを生成] タスクで、[実装モデルの妥当性確認ロジックの生成] チェック ボックスをオンにして、このタスクを実行します。モデルをシミュレートしてもアサーションは表示されませんが、これは、数値結果が一致することを示します。HDL 実装モデルの Simscape アルゴリズムに対する検証を参照してください。

HDL ワークフロー アドバイザー

HDL ワークフロー アドバイザーは、HDL コード生成および FPGA 設計のプロセスをサポートします。このアドバイザーを使用して以下のことを行います。

モデルに HDL コード生成との互換性があるか確認し、非互換の設定を修正。

HDL コード、テスト ベンチ、およびそのコードとテスト ベンチをビルドして実行するスクリプトを生成。

合成およびタイミングの解析を実行し、生成されたコードを SoC、FPGA、Speedgoat I/O のモジュールに展開。

モデル内の FPGA サブシステム用にアドバイザーを実行します。モデル内のサブシステム用に HDL ワークフロー アドバイザーを開くには、関数hdladvisorを使用します。以下に例を示します。

hdladvisor('gmStateSpaceHDL_sschdlex_IO334_BuckConverte/FPGA')

アドバイザー内のタスクの詳細については、該当するタスクを右クリックして [これはなに?] を選択します。HDL ワークフロー アドバイザーのご利用の前にを参照してください。

Simulink Real-Time インターフェイス モデルを生成するワークフロー スクリプトの実行

ラピッド プロトタイピングのために、HDL ワークフロー アドバイザーの設定をスクリプトにエクスポートします。このスクリプトは、コマンド ラインから実行する MATLAB® ファイルです。スクリプトを変更して実行するか、設定を HDL ワークフロー アドバイザーのユーザー インターフェイスにインポートすることができます。スクリプトを使用した HDL ワークフローの実行を参照してください。

この例では、HDL ワークフロー スクリプトの実行方法を説明します。Simulink Real-Time インターフェイス モデルを生成するには、次の MATLAB スクリプトを開いて実行します。

edit('hdlworkflow_buck_IO334')

リアルタイム シミュレーション用の Simulink Real-Time インターフェイス モデルの準備

ワークフロー スクリプトを実行すると、RTL コードと IP コアが生成され、Vivado プロジェクトが作成され、FPGA ビットストリームがビルドされて、その後 Simulink Real-Time インターフェイス モデルが生成されます。

Speedgoat リアルタイム ターゲット マシンにモデルを展開する前に、以下を行います。

1. Speedgoat リアルタイム ターゲット マシンの CPU で実行されているすべてのブロックのサンプル時間を 50 us に設定します (FPGA のドライバー ブロックを含む)。

generated_model = gcs;

2. 信号 PCIe_V_out_frame、PCIe_V_diode_frame、および PCIe_I_inductor_frame に対して、シミュレーション データ インスペクターの設定 [入力処理] を [Columns as channels (frame based)] に設定します。File Log ブロックのマスク内で、ログの記号を右クリックして [インストルメンテーションのプロパティ] ダイアログ ボックスに移動します。ログの記号を表示するために、モデルの更新が必要な場合があります。

set_param(generated_model, 'SimulationCommand', 'update');

あるいは、以下のコマンドを使用して、信号のログをフレーム ベース モードに設定することができます。

Simulink.sdi.setSignalInputProcessingMode([generated_model,'/File Log/Demux'], 1,'frame');

ターゲット マシンへの接続とリアルタイム シミュレーションの実行

これで、Speedgoat リアルタイム ターゲット マシンにモデルを展開できるようになりました。降圧コンバーター モデルは、IO334 上の FPGA に自動的に読み込まれます。

Speedgoat リアルタイム ターゲット マシンに接続します。

tg = slrealtime;

モデルをビルドしてターゲット マシンにダウンロードします。

rtwbuild(generated_model);

モデルの実行を開始します。

tg.start;

ファイルのログ ブロックは、ターゲット マシンの SSD 上に信号を保存します。モデルが停止すると、データはホスト コンピューターに自動的にアップロードされます。このデータはシミュレーション データ インスペクターで可視化されます。リアルタイム シミュレーションの結果が元の Simscape モデルと一致することを確認できます。

Simulink.sdi.setSubPlotLayout(3,1);

allIDs = Simulink.sdi.getAllRunIDs;

run.getAllSignals

Simulink.sdi.view

あるいは、IO334 のアナログ出力で信号を測定できます。以下の図は、MATLAB 内の信号のプロットを示しています。