平均化スイッチを含む Simscape 三相 PMSM 駆動用の HDL コードの生成

この例では、平均化スイッチを含む三相 PMSM Simscape™ モデル用に HDL コードを生成して結果を合成する方法を示します。

平均化スイッチを含む Simscape モデル

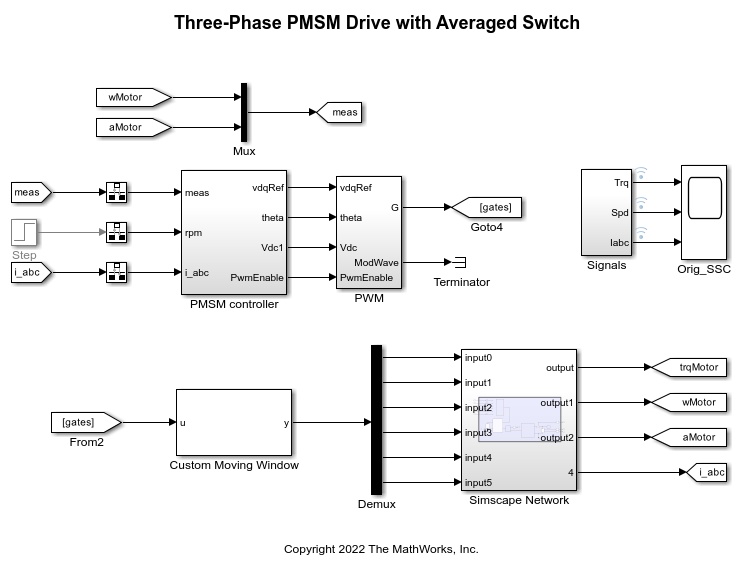

平均化スイッチをもつコンバーター ブロックを使用して Simscape モデル用の HDL コードを生成して FPGA に展開できます。この例では、平均化スイッチで構成された 6 パルス三相制御コンバーター ブロックをもつ三相 PMSM モデルを使用します。このモデルのスイッチング周波数は 50 kHz です。システムを HDL 互換にするために、平均化スイッチではゲート入力に区分的定数近似法を使用します。なお、平均化スイッチを使用するこのモデルでは、分割ローカル ソルバーでデッド タイム (すべてのゲート入力が 0 に設定されているとき) に不安定性が生じることがあります。

合成ツール パスの設定

生成された HDL コードを合成する場合は、HDL Coder™ を使用してコードを生成する前に、合成ツールのパスを設定します。たとえば、合成ツールが Xilinx® Vivado® の場合は、HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアにリストされている Xilinx Vivado の最新バージョンをインストールします。

次に、関数hdlsetuptoolpathを使用して、インストールした Xilinx Vivado 実行可能ファイルへのツール パスを設定します。

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2020.2\bin\vivado.bat')

三相 PMSM 駆動モデル

MATLAB® コマンド プロンプトからモデルを開きます。

ModelName = 'ee_pmsm_drive_averaged_switch_hdl';

open_system(ModelName)

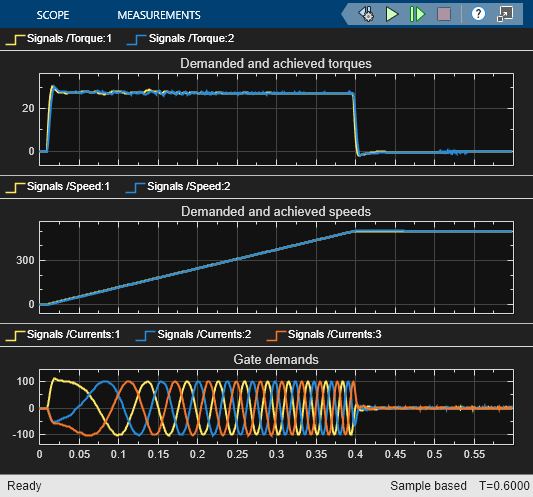

モデルの動作を確認するには、モデルをシミュレートします。

sim(ModelName)

open_system([ModelName '/Orig_SSC'])

Simscape Network サブシステム内のコンポーネントを確認するには、以下を入力します。

open_system('ee_pmsm_drive_averaged_switch_hdl/Simscape Network')

HDL コード生成では、Converter(Three-Phase) ブロック パラメーターの [設定] タブで、[ゲート入力の区分的定数近似に使用される整数 (無効は 0)] パラメーターの値が 10 に設定されます。Solver Configuration (Simscape)ブロックの [ローカル ソルバーを使用] チェック ボックスをオンにすることで、モデルは分割ソルバーを使用するように設定されます。

HDL 実装モデルの生成

Simscape HDL ワークフロー アドバイザーは、Simscape プラント モデルを HDL コード生成用の HDL 互換の実装モデルに変換します。HDL 実装モデルを生成するには、以下を実行します。

1. Simscape HDL ワークフロー アドバイザーを開きます。

sschdladvisor('ee_pmsm_drive_averaged_switch_hdl')

2. [実装モデルの生成] タスクのドロップダウン リストで [実装モデルを生成] タスクを右クリックし、リストから [選択したタスクまで実行] を選択します。リソース利用を改善するために、[実装モデルを生成] タスク ウィンドウで [状態空間のパラメーターを RAM にマッピング] を [オン] に設定します。

タスクが成功すると、HDL 実装モデル gmStateSpaceHDL_ee_pmsm_drive_averaged_swit へのリンクが表示されます。

HDL コードの生成

HDL コード生成用にコンフィギュレーション パラメーターの値を変更するには、gmStateSpaceHDL_ee_pmsm_drive_averaged_swit/Simscape Network/HDL Subsystem に移動します。HDL Algorithm サブシステムを右クリックし、[HDL コード] リストから HDL Block Properties を選択します。[HDL プロパティ] ダイアログ ボックスで DistributedPipelining を On に設定します。[適用] をクリックし、[OK] をクリックします。次に、gmStateSpaceHDL_ee_pmsm_drive_averaged_swit/Simscape Network/HDL Subsystem/HDL Algorithm/State Update/Algebraic Clump2/Mode Vector To Index ブロックに移動します。ブロックを右クリックし、[HDL コード] リストから HDL Block Properties を選択します。[HDL プロパティ] ダイアログ ボックスで InputPipeline および OutputPipeline パラメーターの値を 2 に設定し、[適用] をクリックしてから [OK] をクリックします。Multiply State ブロックおよび Multiply F ブロックを右クリックし、2 つのブロックの SharingFactor を 8 に設定します。モデルを保存し、次の手順に進みます。

モデル コンフィギュレーション パラメーターを HDL コード生成用に推奨される既定値に設定します。

hdlsetup('gmStateSpaceHDL_ee_pmsm_drive_averaged_swit')

HDL ワークフロー アドバイザー

HDL ワークフロー アドバイザーは、HDL コード生成に必要なタスクおよび FPGA 設計のプロセスをサポートします。各タスクの結果に関するフィードバックが提供されます。タスクが完了すると、対応する合成ツールのいずれかから合成結果レポートが提供されます。

HDL 実装モデル内のサブシステム HDL Subsystem を HDL ワークフロー アドバイザーで開きます。

hdladvisor('gmStateSpaceHDL_ee_pmsm_drive_averaged_swit/Simscape Network/HDL Subsystem')

モデル ウィンドウから HDL ワークフロー アドバイザーを開くこともできます。HDL Subsystem を右クリックし、リストから HDL Workflow Advisor を選択します。

ターゲット デバイスおよび合成ツールを設定

HDL コードを生成する前に、コードをターゲット プラットフォームに展開する場合は、合成ツールを指定します。

HDL ワークフロー アドバイザーを開きます。

[ターゲットを設定] タスク フォルダーの [ターゲット デバイスおよび合成ツールを設定] タスクで、[ターゲット ワークフロー] を

Generic ASIC/FPGAとして、[合成ツール] をXilinx Vivadoとして指定します。残りのフィールドには自動入力されます。[ファミリ] をKintex7、[デバイス] をxc7k325t、[パッケージ] をfbg676、[速度] を -1 として指定します。[ターゲット周波数を設定] ウィンドウで、[ターゲット周波数] を 150 として指定します。

実行するタスクを選択し、[このタスクを実行] をクリックします。

HDL コード生成

[HDL コード生成] タスク フォルダーで [HDL オプションの設定] をクリックしてから、[HDL コード生成の設定] ボタンをクリックします。これにより、[コンフィギュレーション パラメーター] ダイアログ ボックスが開きます。[HDL コード生成]、[最適化]、[パイプライン] で

[適応パイプライン]を選択し、[適用] をクリックします。[HDL コード生成]、[グローバル設定]、[クロック設定] セクションで

[オーバーサンプリング係数]を 300 に設定します。[適用] をクリックし、[OK] をクリックします。HDL コードを生成するには、[HDL コード生成] タスク フォルダーでタスクを実行します。

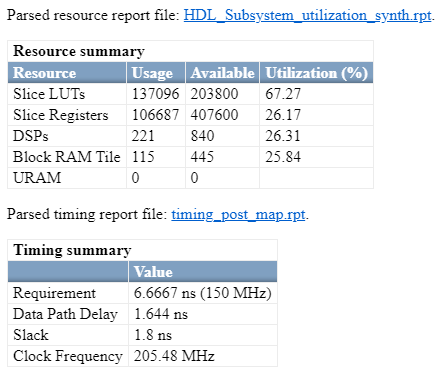

生成された HDL コードの合成

HDL Coder は、ターゲット プラットフォームで HDL コードを合成し、指定したターゲット デバイスに基づいて設計の面積およびタイミング レポートを生成します。指定した FPGA デバイス用にロジック合成を実行し、合成レポートを取得できます。

[FPGA 合成および分析] タスク フォルダーで以下のようにします。

サポートされている FPGA 合成ツール用の FPGA 合成プロジェクトを作成します。

サポートされている FPGA 合成ツールを起動して、合成、マッピングおよび配置/配線タスクを実行します。FPGA 合成を実行するには、[合成および P/R を実行] サブタスク フォルダーの下にある [合成の実行] タスクを右クリックします。これにより、Xilinx Vivado が開始し、Vivado の [合成] ステップが実行されます。元のモデルに合成ツールで取得したクリティカル パスに関する注釈を付けることができます。