HDL 互換 Simulink モデルの作成

この例では、HDL コード生成用の Simulink® モデルを作成する方法を説明します。HDL コード生成と互換性のある MATLAB® アルゴリズムを作成するには、Create HDL- or HLS-Compatible MATLAB Algorithmsを参照してください。

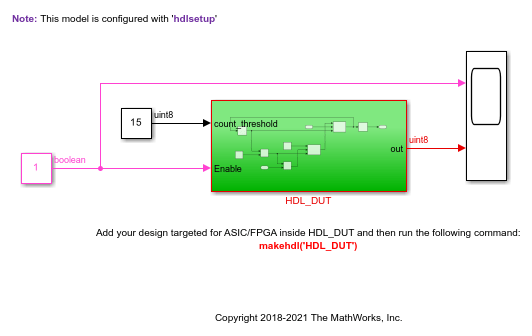

モデルは簡単な加算カウンター アルゴリズムであり、指定した上限に到達するとゼロに戻ります。この手順を実行しないでモデルを直接開くには、簡単なカウンター モデルを参照してください。

[空の DUT] テンプレートの使用

HDL と互換性のある Simulink モデルを作成するには、[空の DUT] テンプレートを使用します。テンプレートは関数 hdlsetup を使用して HDL コード生成用にあらかじめ構成されています。

MATLAB ツールストリップで

ボタンをクリックします。

ボタンをクリックします。Simulink のスタート ページで [HDL Coder] セクションに移動し、[空の DUT] テンプレートを選択します。

書き込み可能な作業フォルダーに

hdlcoder_simple_up_counter.slxのファイル名でモデルを保存します。

[空の DUT] テンプレートには、HDL コードを生成するテスト対象の設計 (DUT) に対応する HDL_DUT サブシステムがあります。DUT の機能を検証するため、テンプレートには HDL_DUT サブシステムの外に、DUT への入力を提供し、出力値をログ記録するテスト ベンチが含まれています。DUT およびテスト ベンチへのモデルの分割を参照してください。

HDL Coder ライブラリからのブロックの選択

カウンター アルゴリズムを設計するには、[HDL Coder] ブロック ライブラリのブロックを使用します。このライブラリに含まれるブロックは、HDL コード生成用に事前設定されています。HDL コード生成をサポートするブロック ライブラリを表示するために Simulink ライブラリ ブラウザーをフィルター処理するには、次のようにします。

[アプリ] タブで、[HDL Coder] を選択します。

[HDL コード] タブから [HDL ブロック プロパティ] 、 [HDL ブロック ライブラリを開く] を選択します。

あるいは、コマンド ラインで「hdllib」と入力します。

hdllib

[HDL Coder] ライブラリのブロックは Simulink で使用できます。HDL Coder™ がない場合、モデル内のブロックのシミュレーションを実行できますが、HDL コードは生成できません。

次のブロック ライブラリ内には HDL でサポートされた追加のブロックがあります。

DSP System Toolbox HDL Support

Communications Toolbox HDL Support

Vision HDL Toolbox

Wireless HDL Toolbox

ライブラリ ブラウザーを既定のビューに戻すには、ライブラリ ブラウザーで、 ボタンをクリックします。あるいは、コマンド ラインで次のように入力します。

ボタンをクリックします。あるいは、コマンド ラインで次のように入力します。

hdllib('off')DUT 向けのアルゴリズムの開発

HDL_DUTサブシステムをダブルクリックします。[HDL Coder] ライブラリからモデルにブロックをドラッグします。次の表に、カウンターを設計するためにモデルに追加するブロックを示します。ブロックの動作について確認したり、そのブロックのブロック パラメーターを指定したりするには、ブロックをダブルクリックします。ブロック ライブラリ ブロック数 ブロック パラメーター Constant Sources 2定数値: 1 と 0

出力データ型: uint8

Switch Signal Routing 21 番目の入力が通過する条件: u2 > しきい値 Delay Discrete 2遅延の長さ: 1 Sum Math Operations 1アキュムレータのデータ型: Inherit:1 番目の入力と同じ Relational Operator Logic and Bit Operations 1関係演算子: > 入力端子

In1とIn2の名前をそれぞれcount_thresholdとEnableに変更します。ブロックをモデルに配置して、それらを接続します。

Enable 信号は、カウンターが前の値から加算カウントするかどうかを指定します。Enable 信号が logical High である場合、カウンターはゼロから count_threshold 値まで加算カウントします。out の値が count_threshold 値と等しくなると、カウンターはゼロに戻り、再びカウントを開始します。Enable 信号が logical Low になると、カウンターは直前の値を保持します。

設計のためのテスト ベンチの作成

モデルの最上位レベルに移動して、入力設定を変更します。

count_thresholdへの Constant ブロック入力。この入力は、カウンターがカウントする最大値を示します。この例では、4 ビットの加算カウンターを設計する方法を示します。[定数値] を15(2^4 - 1) に設定して、[出力データ型] をuint8に設定します。すると、この Constant ブロックの出力データ型は

HDL_DUTサブシステム内の Constant ブロックの出力データ型に一致します。Enableへの Counter Free-Running ブロック入力。Counter Free-Running ブロックを削除します。このブロックを、1の値をもち、[出力データ型] がbooleanに設定されており、1の [サンプル時間] をもつ Constant ブロックで置き換えます。

簡単なモデルの作成も参照してください。

前の節では、上記で説明した手順に従って作成した hdlcoder_simple_up_counter.slx モデルを示しています。モデルを MATLAB で開くには [モデルを開く] ボタンをクリックします。

簡単なカウンター モデル

このモデルはゼロからしきい値である 15 までカウントし、ゼロに戻ります。[count_threshold] 端子に接続されている Constant ブロックの値を変更することで、しきい値を変更できます。[Enable] 端子は、カウンターが加算カウントするか、あるいは前の値を保持するかを指定します。[Enable] 端子に接続されている Constant ブロックの値を変更することで、カウンター アクションを変更できます。値 1 は、カウンターが加算カウントすることを示します。値を 0 にすると、前のカウント値が保持されます。

設計の機能のシミュレーションと検証

モデルの [終了時間] を 50 に設定します。 ボタンをクリックしてモデルのシミュレーションを行います。シミュレーション結果を確認するには、モデルの最上位レベルで Scope ブロックを開きます。

ボタンをクリックしてモデルのシミュレーションを行います。シミュレーション結果を確認するには、モデルの最上位レベルで Scope ブロックを開きます。

シミュレーション結果は、定数値 1 を生成している Enable 信号を表示します。out 信号は 0 から 15 までカウントし、ゼロに戻り、再び加算カウントします。

Simulink モデルからの HDL コードの生成

HDL コードを生成する前に、モデル設定が HDL コード生成と互換性があることを検証できます。この例で使用したカウンター モデルは HDL コード生成と互換性があります。モデルについて HDL 互換性を検証し更新するには、HDL コード アドバイザーを使用します。HDL コード アドバイザーを使用した Simulink モデルの HDL 互換性のチェックを参照してください。

Simulink モデルからの HDL コードの生成を参照してください。

参考

hdllib | checkhdl | hdlsetup | hdlcodeadvisor