Simulink での HDL アルゴリズムのモデル化に関する基本的なガイドライン

Simulink® で HDL アルゴリズムを開発する場合は、これらのガイドラインを使用してください。これには、設計をモデル化する際の HDL でサポートされたブロックの使用に関するガイドラインやアルゴリズムを開発する際の設計を分割する方法に関するガイドラインが含まれます。

各ガイドラインに準拠要件のレベルを示す重大度レベルが割り当てられています。詳細については、HDL モデリング ガイドラインの重大度レベルを参照してください。

HDL でサポートされたブロックの使用

ガイドライン ID

1.1.1

重大度

強く推奨

説明

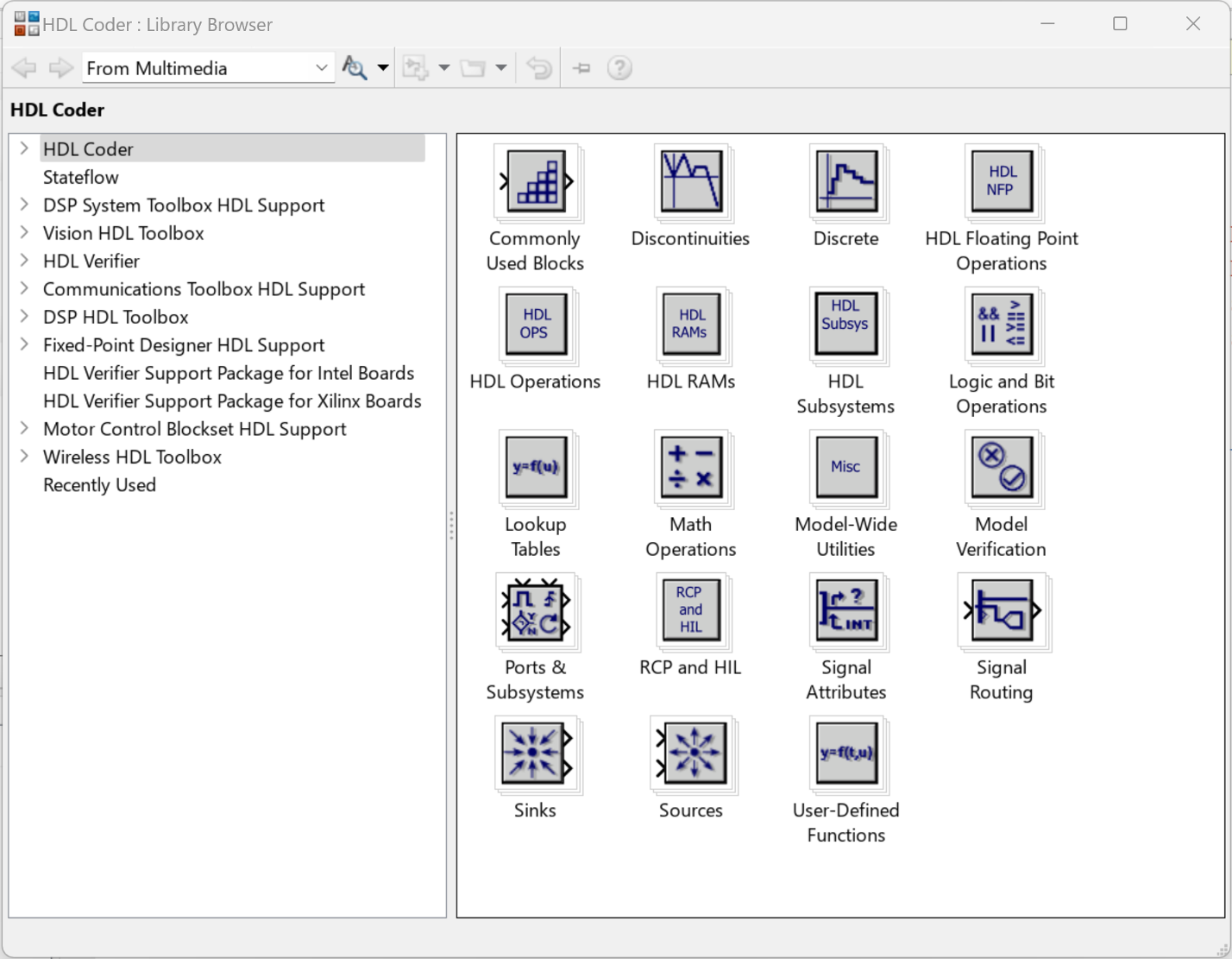

Simulink モデルを作成するときは、[Simulink ライブラリ ブラウザー] 、 [HDL Coder] ライブラリのブロックを使用します。このライブラリに含まれるいくつかのブロックは、HDL コード生成用に事前設定されています。このライブラリ内のブロックは Simulink で使用できます。HDL Coder™ がない場合、モデル内のブロックのシミュレーションを実行できますが、HDL コードは生成できません。

次のブロック ライブラリ内には HDL でサポートされた追加の Simulink ブロックがあります。

DSP HDL Toolbox™

Vision HDL Toolbox™

Wireless HDL Toolbox™

HDL でサポートされたブロックのみをライブラリ ブラウザーで表示するには、次の手順に従います。

[アプリ] タブで、[HDL Coder] を選択します。[HDL コード] タブが表示されます。[HDL ブロック プロパティ] 、 [HDL ブロック ライブラリを開く] を選択します。

あるいは、MATLAB® コマンド ウィンドウで「

hdllib」と入力します。hdllib

ライブラリ ブラウザーを既定のビューに戻すには、次のコマンドを入力します。

hdllib('off')メモ

サポートされているブロックの内容は将来のリリースで変更されます。本製品の新しいバージョンをインストールするたびに、サポートされるブロックのライブラリを再作成してください。

DUT およびテスト ベンチへのモデルの分割

ガイドライン ID

1.1.2

重大度

推奨

説明

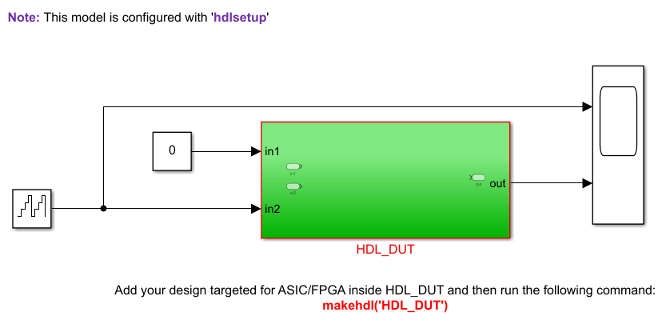

HDL コード生成用の Simulink モデルを作成する場合、HDL コードを生成する Subsystem がテスト対象の設計 (DUT) になります。このサブシステムには、ターゲットの FPGA または ASIC デバイス上に実装できる Simulink ブロックが含まれます。DUT 内のロジックを機能、設計のサンプルレートなどに基づいてさらに小さいサブシステムに分割できます。HDL コードを生成するときに、DUT は最上位のモジュールまたはエンティティになり、DUT 内のサブシステムはサブモジュールまたはより小さいエンティティになります。

DUT サブシステム外のブロックはテスト ベンチの一部になります。テスト ベンチには HDL コード生成でサポートされていないブロックを含めることができます。次のためにテスト ベンチをシミュレートします。

Simulink モデルの DUT の機能を検証する。

生成されるモデルと元のモデルが機能的に同等かどうかを検証する。

たとえば、Simulink モデル テンプレート [Blank_DUT] を開くと、このモデルは Simulink エディターで開きます。

このモデルでは、[HDL_DUT] サブシステムが DUT で、このサブシステム外のブロックがテスト ベンチを作成します。HDL アルゴリズムを [HDL_DUT] サブシステム内に開発できます。このテンプレート モデルは HDL コード生成用にあらかじめ構成されています。

2 バイト文字を使用しない

ガイドライン ID

1.1.3

重大度

強く推奨

説明

下流の合成ツールおよびシミュレーション ツールでは、日本語や中国語の文字などの 2 バイト文字はサポートされません。HDL Coder では以下の使用がサポートされません。

モデル名やブロック名での 2 バイト文字の使用。

モデル名やブロック名でのオペレーティング システムの予約語の使用。これには、

CR、con、prn、aux、ptr、null、ipt1、ipt2、ipt3、ipt4、com1、com2、com3、com4などが含まれます。コメントでの 2 バイト文字の使用。これは、コメントは生成コードに伝播されるためです。代わりに英語のコメントを使用してください。

モデルの機能や属性のドキュメント化

ガイドライン ID

1.1.4

重大度

推奨

説明

生成された HDL コードを管理しやすくするために、参照情報を次の方法でモデル設定の一部としてドキュメント化できます。

設計およびテストベンチに使用する HDL コードのカスタム ファイル ヘッダー コメントとフッター コメント

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [グローバル設定] 、 [コーディング スタイル] タブで、[カスタム ファイルのヘッダー コメント] パラメーターと [カスタム ファイルのフッター コメント] パラメーターを使用して、生成されたすべての HDL ファイルにヘッダーまたはフッターとして表示するカスタム コメントを入力できます。詳細については、カスタム ファイルのヘッダー コメントおよびCustom File Footer Commentを参照してください。

モデルおよびブロックの注釈、テキスト コメント、要件コメント

モデルの注釈、テキスト コメント、または要件コメントの形式で生成コードに注釈を追加できます。たとえば、ブロック線図に Simulink の注釈としてテキストを直接入力したり、モデルに DocBlock を配置してテキスト コメントを挿入したりできます。ブロック線図の注釈をモデルのブロックに関連付けるには、注釈をそれらのブロックに線でつなぎます。これにより、注釈が生成コードのブロックの横にコメントとして表示されます。詳細については、注釈またはコメント付きの HDL コードの生成を参照してください。

ブロックの機能と属性のファイルごとのカスタム ヘッダー コメント

設計で使用するサブシステムの [ブロック プロパティ] の [説明] セクション。この情報は HDL コードにコメント ヘッダーとして表示されます。たとえば、次の図は設計の

Vector FFTSubsystem に対する追加されたブロック コメントを示しています。

ブロック コメントは生成された HDL コードにヘッダーとして表示されます。

-- Simulink subsystem description for vector_fft_implementation_example/Vector_FFT: -- -- Created by: John -- Function: Vector FFT -- This model shows... -- Revision 1.0 -- Revision 1.1 added functionality to... -- -- ------------------------------------------------------------- LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.numeric_std.ALL; ENTITY Vector_FFT IS