注釈またはコメント付きの HDL コードの生成

HDL Coder™ ソフトウェアを使用して、Simulink® のモデルの注釈、テキスト コメント、または要件から、生成された HDL コードにテキストの注釈を作成できます。

Simulink の注釈

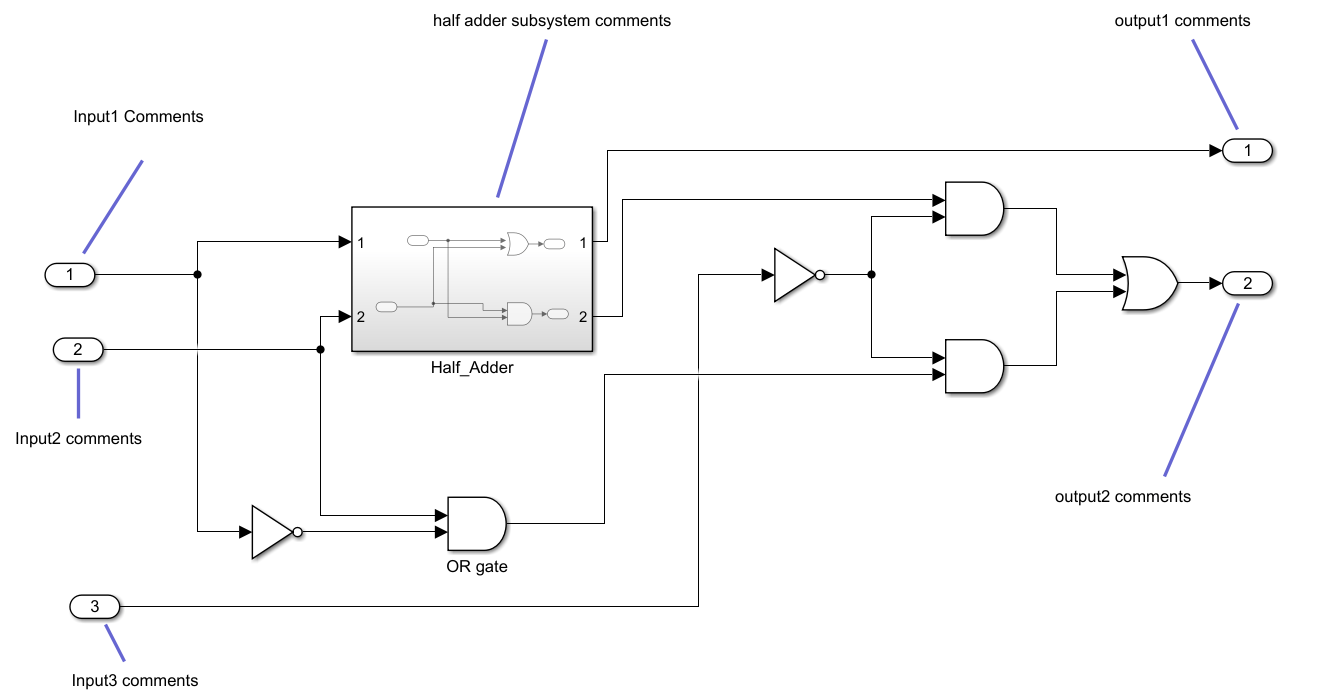

Simulink 注釈を使用することで、Inport ブロックや Outport ブロックなどのブロック用のコメントを含むコードを生成できます。Simulink 注釈をモデルに追加すると、HDL Coder は、その注釈のテキストを生成されたコードでプレーン テキストのコメントとしてレンダリングします。コメントは、モデルの階層構造内で注釈を含むサブシステムと同じレベルに生成されます。下図では、Inport、Outport、およびその他のブロック用の Simulink 注釈が含まれているモデルを示しています。

次のコードの抜粋は、生成された VHDL® コードを表示します。コードには、ブロック用のテキスト コメントが含まれます。

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE IEEE.numeric_std.ALL; ENTITY Sub_Circuit IS PORT( -- Input1 Comments In1 : IN std_logic; -- Input2 comments In2 : IN std_logic; -- Input3 comments In3 : IN std_logic; -- output1 comments Out1 : OUT std_logic; -- output2 comments Out2 : OUT std_logic ); END Sub_Circuit; ARCHITECTURE rtl OF Sub_Circuit IS -- Component Declarations COMPONENT Half_Adder PORT( In1 : IN std_logic; In2 : IN std_logic; Out1 : OUT std_logic; Out2 : OUT std_logic ); END COMPONENT; BEGIN -- half adder subsystem comments u_Half_Adder : Half_Adder PORT MAP( In1 => In1, In2 => In2, Out1 => Half_Adder_out1, Out2 => Half_Adder_out2 ); NOT1_out1 <= NOT In3; AND3_out1 <= Half_Adder_out2 AND NOT1_out1; NOT_out1 <= NOT In1; OR_gate_out1 <= In2 AND NOT_out1; AND5_out1 <= NOT1_out1 AND OR_gate_out1; AND6_out1 <= AND3_out1 OR AND5_out1; Out1 <= Half_Adder_out1; Out2 <= AND6_out1; END rtl;

Constant ブロックの場合、注釈を HDL コード内のコメントに変換するには、[コンフィギュレーション パラメーター] ウィンドウで次のようにします。

[HDL コード生成]、[グローバル設定] ペインの [コーディング スタイル] タブで、[中間信号を最小にする] チェック ボックスをオフにします。

[HDL コード生成]、[レポート] ペインで [トレーサビリティ スタイル] を

[Comment Based]に設定します。

注釈の詳細については、モデルの注釈付けを参照してください。

信号の説明

Simulink モデル内の信号の説明を指定すると、生成された HDL コードでは、その説明が信号宣言ステートメントの上にコメントとして表示されます。信号の説明を指定するには、信号を右クリックして [プロパティ] を選択し、[信号プロパティ] ダイアログ ボックスを開きます。[ドキュメンテーション] タブを選択し、[説明] フィールドに信号の説明を入力します。信号の説明では、ASCII 文字を使用します。生成されたコードに非 ASCII 文字があると、下流の合成ツールや lint ツールの妨げになる可能性があります。場合によっては、信号に対して行われる最適化により、生成されたコードでは一部の信号の説明が HDL コメントに変換されないか、特定の信号について説明する HDL コメントの複製が作成されることがあります。

テキスト コメント

DocBlock ブロックを使用してモデルでテキスト コメントを入力すると、HDL Coder は、DocBlock ブロックのテキストを生成されたコードでプレーン テキストのコメントとしてレンダリングします。コメントは、モデルの階層構造内で DocBlock ブロックを含むサブシステムと同じレベルに生成されます。

DocBlock ブロックの [ドキュメント タイプ] パラメーターを [テキスト] に設定します。HDL Coder は、[HTML] や [RTF] のオプションをサポートしません。

DocBlock ブロックの詳細については、DocBlockを参照してください。

要件コメントおよびハイパーリンク

Requirements Toolbox™ を使用することで、要件をモデル要素に割り当て、生成コードでその要件をコメントとして生成できます。以下に例を示します。

以下のコマンドを使用してモデル

hdlcoder_simple_up_counterを開きます。openExample("hdlcoder_simple_up_counter");要件エディター (Requirements Toolbox)を開き、

Delay_requirements.slreqxという名前の新しい要件セットを作成します。詳細については、MATLAB または Simulink での要件の作成 (Requirements Toolbox)を参照してください。

以下の詳細を指定して要件を作成します。

カスタム ID: 1

概要: Requirement 1

説明: Sample text 1

同様に、以下の詳細を指定して別の要件を作成します。

カスタム ID: 2

概要: Requirement 2

説明: Sample text 2

ヒント

要件パースペクティブを使用して、Simulink エディターから離れることなくリンクを作成できます。詳細については、Simulink での要件の表示とリンク (Requirements Toolbox)を参照してください。

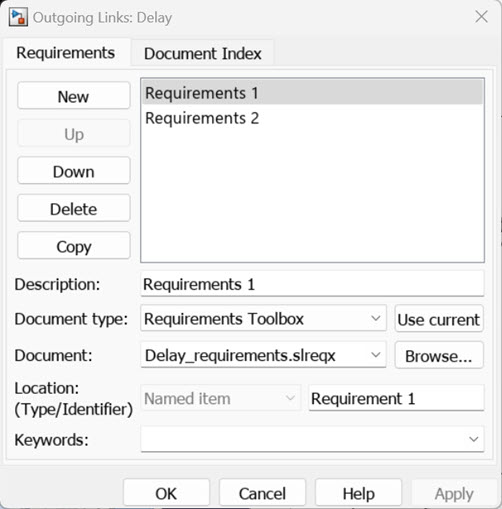

HDL_DUTサブシステムを開きます。Delayという名前の Delay ブロックを右クリックします。コンテキスト メニューに要件ビューアー アプリのオプションを追加するには、[アプリの選択] をポイントし、[要件ビューアー] をクリックします。次に、要件ビューアー アプリのセクションで、[外向きリンク エディター] を選択します。要件をリンクします。[新規] ボタンをクリックします。[説明] を

Requirements 1に設定し、[ドキュメント タイプ] をRequirements Toolboxに設定し、[ドキュメント] をDelay_requirements.slreqxに設定し、[場所 (タイプ/識別子)] をRequirement 1に設定します。

手順 4 と 5 を繰り返し、Requirement 2 を Subsystem にリンクします。

[適用] および [OK] をクリックします。

生成されたコードにハイパーリンク コメントとして要件を含めるには、[コンフィギュレーション パラメーター] ダイアログ ボックスで以下のようにします。

[HDL コード生成]、[レポート] ペインで、[トレーサビリティ レポートの生成] を選択します。

[HDL コード生成]、[グローバル設定] ペインの [コメント] タブで、[ブロック コメントに要件を含める] を選択します。

あるいは、コマンド ラインからコードを生成する場合は、関数

makehdlを使用してTraceabilityおよびRequirementCommentsプロパティを設定します。makehdl("HDL_DUT","Traceability","on","RequirementComments","on");

生成された HDL コードには、

hdlcoder_simple_up_counterモデル内の Delay ブロックとHDL_DUTサブシステムのコメントが含まれており、モデルの各ブロックに関連する要件へのリンクが含まれています。//------------------------------------------------------------- // Module: HDL_DUT // Source Path: hdlcoder_simple_up_counter/HDL_DUT // Hierarchy Level: 0 // Model version: 9.2 // // Block requirements for <Root>/HDL_DUT // 1. Delay_requirements.slreqx:Requirement 2 // // ------------------------------------------------------------- module HDL_DUT (clk, reset, clk_enable, count_threshold, Enable, ce_out, out); input clk; input reset; input clk_enable; input [7:0] count_threshold; // uint8 input Enable; output ce_out; output [7:0] out; // uint8 // Block requirements for <S1>/Delay1 // 1. Delay_requirements.slreqx:Requirement 1 always @(posedge clk or posedge reset) begin : Delay1_process if (reset == 1'b1) begin Delay1_out1 <= 8'b00000000; end else begin if (enb) begin Delay1_out1 <= Switch1_out1; end end end assign out = Delay1_out1; assign ce_out = clk_enable; endmodule // HDL_DUT