設計の変更によるリソース共有の改善

この例では、設計の一部を変更することで、リソース共有によるモデル設計の最適化の機会を高める方法を示します。リソース共有は、ターゲット FPGA デバイスでの設計の面積使用を改善する HDL Coder の最適化です。この最適化では、機能的に等価な複数のリソースを特定し、それらを単一のリソースに置き換えます。詳細については、リソース共有を参照してください。

現在のモデルの解析

次のコードを実行して、必要なサンプル ファイルを一時フォルダーにコピーします。

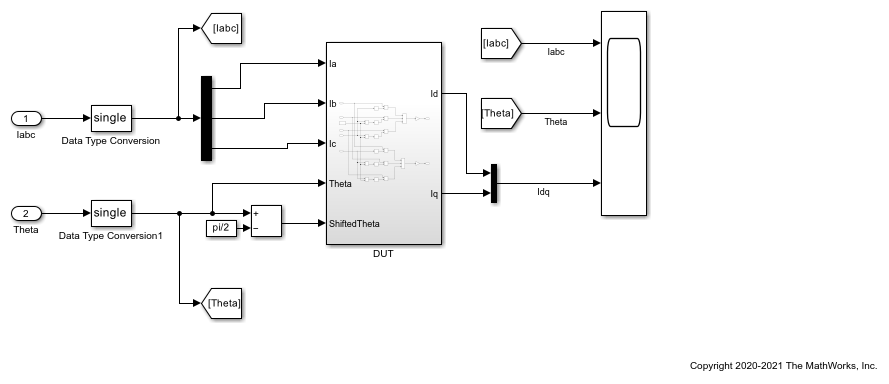

design_name = 'hdlcoderParkTransform'; design_new_name = 'hdlcoderParkTransformCopy'; copyfile(fullfile([design_name,'.slx']), fullfile([design_new_name,'.slx']), 'f'); % Open the model. open_system(design_new_name);

% Set a SharingFactor of 6 on the subsystem of interest and generate % HDL along with the corresponding reports from the model. subsystem = [design_new_name '/DUT']; hdlset_param(subsystem, 'SharingFactor', 6); makehdl(subsystem);

### Working on the model <a href="matlab:open_system('hdlcoderParkTransformCopy')">hdlcoderParkTransformCopy</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderParkTransformCopy/DUT')">hdlcoderParkTransformCopy/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderParkTransformCopy', { 'HDL Code Generation' } )">hdlcoderParkTransformCopy</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderParkTransformCopy'.

### Begin compilation of the model 'hdlcoderParkTransformCopy'...

### Working on the model 'hdlcoderParkTransformCopy'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 42 cycles.

### Output port 2: 42 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoderParkTransformCopy', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderParkTransformCopy'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdl_prj/hdlsrc/hdlcoderParkTransformCopy/gm_hdlcoderParkTransformCopy.slx')">hdl_prj/hdlsrc/hdlcoderParkTransformCopy/gm_hdlcoderParkTransformCopy.slx</a>

### Begin VHDL Code Generation for 'hdlcoderParkTransformCopy'.

### MESSAGE: The design requires 6 times faster clock with respect to the base rate = 1e-05.

### Begin VHDL Code Generation for 'DUT_tc'.

### Working on DUT_tc as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/DUT_tc.vhd.

### Code Generation for 'DUT_tc' completed.

### Working on hdlcoderParkTransformCopy/DUT/nfp_sin_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_sin_single.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_add_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_add_single.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_sub_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_sub_single.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_mul_single.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_mul_single_block.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_add_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_add_single_block.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_add2_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_add2_single.vhd.

### Working on hdlcoderParkTransformCopy/DUT/nfp_sub_single as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/nfp_sub_single_block.vhd.

### Working on hdlcoderParkTransformCopy/DUT as hdl_prj/hdlsrc/hdlcoderParkTransformCopy/DUT.vhd.

### Generating package file hdl_prj/hdlsrc/hdlcoderParkTransformCopy/DUT_pkg.vhd.

### Code Generation for 'hdlcoderParkTransformCopy' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformCopy', '/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformCopy/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformCopy/DUT_report.html

### HDL check for 'hdlcoderParkTransformCopy' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

生成されたストリーミングおよび共有レポートを確認すると、共有可能と特定されたグループがいくつかあることがわかります。

Resource Type Group Size Block Name

_________________ ____________ ____________

Trigonometry 6 sine

Sum 2 AddSub2

Sum 2 AddSub1

Product 6 Product

Product 2 Gainネイティブ浮動小数点リソース レポートには、必要な演算子が次のように表示されます。

Resource Usage

_________________________ ________

Adders 4

Multipliers 2

Sin 1

Subtractors 2高水準リソース レポートには、設計のリソース利用の推定結果が次のように表示されます。

Resource Usage

_________________________ ________

Multipliers 9

Adders/Subtractors 152

Registers 1121

Total 1-Bit Registers 15896

RAMs 0

Multiplexers 857

I/O Bits 228

Static Shift operators 5

Dynamic Shift operators 13モデルで合成ワークフローを実行することもできます。このモデルの合成結果は次のようになります。

Resource Usage

_________________________ ________

Slice LUTs 29381

Slice Registers 24140

DSPs 50

Block Ram Tile 0

URAM 0合成ワークフローの詳細については、Simulink モデルからの HDL コード生成と FPGA 合成を参照してください。

モデル内のパターンの検出

モデルをさらに解析すると、リソース共有を改善するために変更できるパターンがいくつか見つかります。

そのようなパターンの 1 つは、名前が AddSub で始まり、出力が Sin ブロックに送られる、Add ブロックと Subtract ブロックにあります。

2 つ目のパターンは、Gain ブロックが続く Sum (加算または減算) ブロックに該当します。

これらのパターンのいずれにも、強調表示されたブロックに最適なリソース共有を妨げる相違がいくつかあります。次のような相違です。

まず、Gain ブロックの近くの領域にある Sum ブロックの符号が異なります。符号は、上から下の順に +++ と --- です。

この不一致は次のように変更して修正できます。

下の Sum ブロックの符号を

---から+++に切り替えます。下の 3 つの Sin ブロックを Cos ブロックにします。

Cos ブロックおよび下の 2 つの Sum ブロックへの入力を

Inport 5 ShiftedThetaからInport 4 Thetaに変更します。

次に、さまざまな領域にある Sum ブロックの符号が異なります。符号は、上から下の順に +-、++、+-、++ です。

両方の符号が正のブロックは、2 つの符号が異なるブロックとは別に共有されています。両方の符号が正のブロックと 2 つの符号が異なるブロックのこの分離により、必要なリソースが多くなっています。モデルをさらに簡潔にすれば、モデル内の Sum ブロックの数を減らすことができ、リソース共有も改善します。Sum ブロックへの入力も同様であり、必要な Sum ブロックの数を 2 つに削減できます。符号の不一致は、その後に Unary Minus ブロックを導入して簡単に解決できます。

これで相違が解決され、元のモデルよりも多くのリソースが共有されるようになります。

この編集後のモデルは hdlcoderParkTransformShare.slx という名前で保存されています。次のコマンドを使用して、このバージョンのモデルを一時ディレクトリにコピーします。

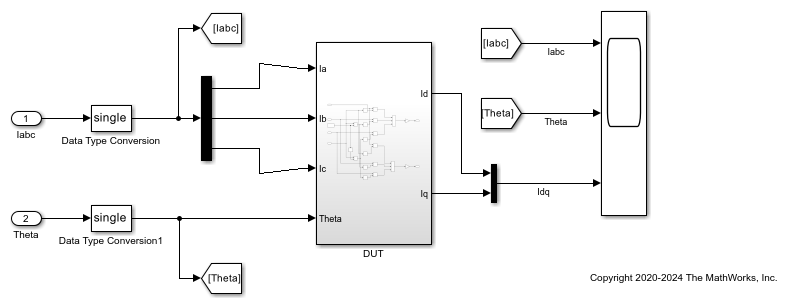

design_name = 'hdlcoderParkTransformShare'; design_new_name = 'hdlcoderParkTransformShareCopy'; copyfile(fullfile([design_name,'.slx']), fullfile([design_new_name,'.slx']), 'f'); % Open the model. open_system(design_new_name);

最適化されたモデルの結果の比較

このモデルはリソース共有用に改善されており、より多くのリソースを共有してリソース利用を改善できます。対象のサブシステムで SharingFactor を 3 に設定し、最適化されたモデルから対応するレポートと共に HDL を生成します。

subsystem = [design_new_name '/DUT']; hdlset_param(subsystem, 'SharingFactor', 6); makehdl(subsystem);

### Working on the model <a href="matlab:open_system('hdlcoderParkTransformShareCopy')">hdlcoderParkTransformShareCopy</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderParkTransformShareCopy/DUT')">hdlcoderParkTransformShareCopy/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderParkTransformShareCopy', { 'HDL Code Generation' } )">hdlcoderParkTransformShareCopy</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderParkTransformShareCopy'.

### Begin compilation of the model 'hdlcoderParkTransformShareCopy'...

### Working on the model 'hdlcoderParkTransformShareCopy'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 38 cycles.

### Output port 2: 38 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoderParkTransformShareCopy', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderParkTransformShareCopy'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/gm_hdlcoderParkTransformShareCopy.slx')">hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/gm_hdlcoderParkTransformShareCopy.slx</a>

### Delay absorption obstacles can be diagnosed by running this script: <a href="matlab:run('hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/highlightDelayAbsorption')">hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/highlightDelayAbsorption.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/clearhighlighting.m')">hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/gm_hdlcoderParkTransformShareCopy_vnl')">gm_hdlcoderParkTransformShareCopy_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderParkTransformShareCopy'.

### MESSAGE: The design requires 6 times faster clock with respect to the base rate = 6.

### Begin VHDL Code Generation for 'DUT_tc'.

### Working on DUT_tc as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT_tc.vhd.

### Code Generation for 'DUT_tc' completed.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_sincos_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_sincos_single.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_sub_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_sub_single.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_mul_single.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_add_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_add_single.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_mul_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_mul_single_block.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT/nfp_uminus_single as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/nfp_uminus_single.vhd.

### Working on hdlcoderParkTransformShareCopy/DUT as hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT.vhd.

### Generating package file hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT_pkg.vhd.

### Code Generation for 'hdlcoderParkTransformShareCopy' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy', '/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex70693517/hdl_prj/hdlsrc/hdlcoderParkTransformShareCopy/DUT_report.html

### HDL check for 'hdlcoderParkTransformShareCopy' complete with 0 errors, 0 warnings, and 2 messages.

### HDL code generation complete.

設計の変更後のネイティブ浮動小数点リソース レポートには、必要な演算子が更新されて次のように表示されます。

Resource Usage

_________________________ ________

Adders 2

Multipliers 2

SinCos 1

Subtractors 1

Unary Minus 1共有後に [加算器]、[乗算器]、および [減算器] の数が少なくなったことがわかります。

共有後の高水準リソース レポートには、設計のリソース利用の推定結果が次のように表示されます。

Resource Usage

_________________________ ________

Multipliers 13

Adders/Subtractors 178

Registers 1012

Total 1-Bit Registers 16888

RAMs 0

Multiplexers 610

I/O Bits 196

Static Shift operators 8

Dynamic Shift operators 8モデルで合成を実行した後、次のような結果が表示されます。

Resource Usage

_________________________ ________

Slice LUTs 8792

Slice Registers 8419

DSPs 13

Block Ram Tile 0

URAM 0共有後に [Slice LUTs]、[Slice Registers]、および [DSPs] の数が少なくなったことがわかります。

クローン検出アプリケーションによる繰り返しパターンの自動置き換えを使用してリソース共有をさらに改善する方法については、クローン検出と置換によるリソース共有の改善を参照してください。