クロックレート パイプラインを使用したクロック周波数の向上

この例では、クロックレート パイプラインを適用して設計内の遅いパスを最適化することで、レイテンシを少なくし、クロック周波数を高め、使用面積を減らす方法を示します。クロックレート パイプラインの使用方法の詳細については、クロックレート パイプラインを参照してください。

はじめに

Simulink® を使用したアルゴリズム設計により、生成された HDL 設計に遅いレートのデータパスが導入されることがあります。これらのパスは、アルゴリズムのデータ レートが HDL のクロック レートよりも遅いレートで動作するため、Simulink の遅いサンプル時間の演算に対応しています。

クロックレート パイプラインは、同じデータ レートで動作し、レート変更ブロックまたは Delay ブロックのいずれかで区切られた最大の部分領域をモデル内で特定します。これらの部分領域は、クロックレート パイプラインの有力な候補となることから、"クロックレート領域" と呼ばれます。クロックレート領域の出力がデータ レートの Delay ブロックの場合、HDL Coder はその Delay ブロックを吸収します。その結果、データ レートとクロック レートの比に等しい、いくつかのクロックレート パイプラインの割り当てになります。

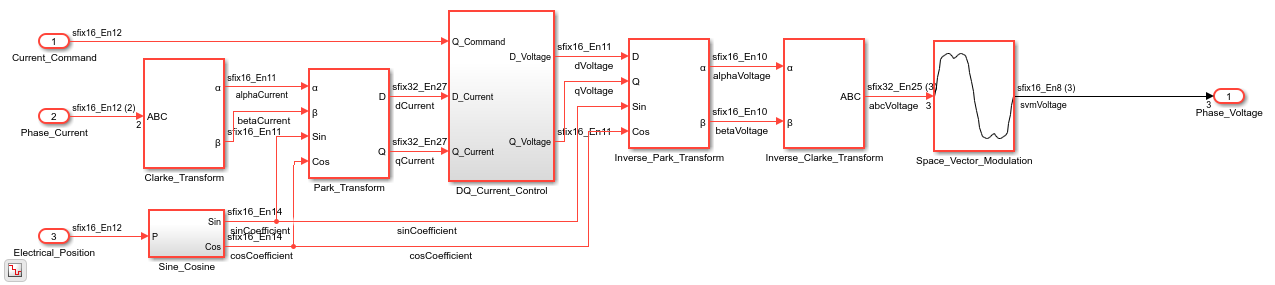

永久磁石同期機のベクトル制御のベクトル制御の例について考えます。これは、FPGA にマッピングするモーター制御の設計を示したものです。入力サンプルは、20  または 50 KHz の間隔で到達します。閉制御ループでは、コントローラーのレイテンシが目的の応答時間以内でなければなりません。出力端子に遅延があり、結果としてレイテンシが 20

または 50 KHz の間隔で到達します。閉制御ループでは、コントローラーのレイテンシが目的の応答時間以内でなければなりません。出力端子に遅延があり、結果としてレイテンシが 20  になります。

になります。

タイミングや面積などの設計の制約を満たすために、入力および出力パイプライン、分散型パイプライン、ストリーミング/共有など、複数の最適化を適用できます。さらに、マルチサイクルのパイプライン化された演算として、sqrt や divide などの自明でない数学関数を実装できます。これらの最適化によって導入されるパイプラインは、信号パスが動作するレートと同じ 20  で適用されるため、追加のパイプラインを導入することによって望ましくないレイテンシ オーバーヘッドが発生し、閉ループのレイテンシの割り当てに違反することがあります。

で適用されるため、追加のパイプラインを導入することによって望ましくないレイテンシ オーバーヘッドが発生し、閉ループのレイテンシの割り当てに違反することがあります。

ただし、FPGA では、このコントローラーを MHz の単位で実装できます。これは、導入されるパイプラインが MHz のレートで動作できるようになり、レイテンシへの影響が最小化されることを意味します。クロックレート パイプラインは、このレート差を利用してコントローラーをパイプライン化し、FPGA の面積とタイミングの特性を向上させます。この例では、クロックレート パイプラインを使用して、タイミングと面積の最適化を段階的に適用する方法を示します。

モデルの準備

クロックレート パイプラインを使用できるようにモデルを準備します。

hdlcoderFocCurrentFixptHdl モデルを開き、レート差を定義します。Simulink の信号パスが HDL で遅いパスになる理由は、信号パスがモデルの基本サンプル時間よりも遅いサンプル時間で動作しているか、Simulink の基本サンプル時間がクロック レートではなくデータ レートに対応しているかのいずれかです。このモデルの基本サンプル時間は 20  秒です。コントローラーの最終的な FPGA 実装のターゲットは 40 MHz (25 ナノ秒) です。

秒です。コントローラーの最終的な FPGA 実装のターゲットは 40 MHz (25 ナノ秒) です。

open_system('hdlcoderFocCurrentFixptHdl')

モデルのサンプル時間を 25 ナノ秒に設定すると、Simulink のシミュレーションのパフォーマンスが遅くなります。HDL Coder は、コンフィギュレーション パラメーターSimulink のレートを実際のハードウェアのレートとして扱うを選択した場合、FPGA クロック レートを Simulink の基本サンプル時間の何倍の速度にするかを自動的に決定できます。この場合、HDL Coder は、FPGA のターゲット周波数 40 MHz をモデルの基本周波数 50 KHz で除算することで、設計に必要なオーバーサンプリング値を計算します。

サブシステムの最適化を設定します。固定小数点設計では、HDL Coder はパイプラインを挿入する必要がある場合のみ、クロックレート パイプラインをサブシステムに適用します。パイプラインを導入する HDL Coder のオプションには、分散型パイプライン、共有、ストリーミング、入力/出力パイプライン、制約付き出力パイプライン、適応パイプライン、および浮動小数点実装などのマルチサイクル実装を導入するブロック実装があります。最適化は、サブシステムの階層を維持するためにローカルに適用するか、配下のサブシステムがフラットであればグルーバルに適用できます。ローカルの場合は、パイプラインと最適化の設定を個々のサブシステムに適用します。グローバルな最適化を適用するには、最上位のサブシステムで設定します。階層のフラット化の前提条件に関する詳細については、階層のフラット化を参照してください。

クロックレート パイプラインの適用

元のモデル hdlcoderFocCurrentFixptHdl のコピーを作成し、hdlcoderFocClockRatePipelining として保存します。この例では、クロックレート パイプラインの最適化を新しいモデルに適用し、元のモデルと比較します。

srcHdlModel = 'hdlcoderFocCurrentFixptHdl'; dstHdlModel = 'hdlcoderFocClockRatePipelining'; dstHdlDut = [dstHdlModel '/FOC_Current_Control']; gmHdlModel = ['gm_' dstHdlModel]; gmHdlDut = ['gm_' dstHdlDut]; open_system(srcHdlModel); save_system(srcHdlModel,dstHdlModel);

HDL コードを生成するアルゴリズムを含むサブシステム FOC_Current_Control が、テスト対象デバイス (DUT) です。DUT サブシステムを開きます。

open_system(dstHdlDut);

クロックレート パイプラインを適用します。クロックレート パイプラインは既定で有効であり、HDL コード生成時にクロックレート領域が自動的に検出されます。詳細については、クロックレート パイプラインを参照してください。

hdlset_param(dstHdlModel, 'ClockRatePipelining', 'on');

モデルに対して TargetFrequency を 40 MHz に設定し、TreatRatesAsHardwareRates を有効にしてクロックレート パイプラインのオーバーサンプリング値を設定し、モデルに対する分散型パイプラインを有効にすることで、クロック速度を上げるようにモデルを設定します。既定では、サブシステムは最上位の分散型パイプラインの設定を継承します。

hdlset_param(dstHdlModel, 'TargetFrequency', 40); hdlset_param(dstHdlModel, 'TreatRatesAsHardwareRates', 'on'); hdlset_param(dstHdlModel, 'DistributedPipelining', 'on'); save_system(dstHdlModel);

クロックレート パイプラインの影響を確認するには、HDL コードを生成し、コード生成レポートを開いて [クロック レート パイプライン] セクションを表示します。

makehdl(dstHdlDut);

### Working on the model <a href="matlab:open_system('hdlcoderFocClockRatePipelining')">hdlcoderFocClockRatePipelining</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocClockRatePipelining/FOC_Current_Control')">hdlcoderFocClockRatePipelining/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocClockRatePipelining', { 'HDL Code Generation' } )">hdlcoderFocClockRatePipelining</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocClockRatePipelining'.

### Begin compilation of the model 'hdlcoderFocClockRatePipelining'...

### Begin compilation of the model 'hdlcoderFocClockRatePipelining'...

### Working on the model 'hdlcoderFocClockRatePipelining'...

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocClockRatePipelining', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderFocClockRatePipelining'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoderFocClockRatePipelining/gm_hdlcoderFocClockRatePipelining.slx')">hdlsrc/hdlcoderFocClockRatePipelining/gm_hdlcoderFocClockRatePipelining.slx</a>

### Clock-rate pipelining obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc/hdlcoderFocClockRatePipelining/highlightClockRatePipelining')">hdlsrc/hdlcoderFocClockRatePipelining/highlightClockRatePipelining.m</a>

### To highlight blocks that obstruct distributed pipelining, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoderFocClockRatePipelining/highlightDistributedPipeliningBarriers')">hdlsrc/hdlcoderFocClockRatePipelining/highlightDistributedPipeliningBarriers.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoderFocClockRatePipelining/clearhighlighting.m')">hdlsrc/hdlcoderFocClockRatePipelining/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoderFocClockRatePipelining/gm_hdlcoderFocClockRatePipelining_vnl')">gm_hdlcoderFocClockRatePipelining_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderFocClockRatePipelining'.

### MESSAGE: The design requires 800 times faster clock with respect to the base rate = 2e-05.

### Begin VHDL Code Generation for 'FOC_Current_Control_tc'.

### Working on FOC_Current_Control_tc as hdlsrc/hdlcoderFocClockRatePipelining/FOC_Current_Control_tc.vhd.

### Code Generation for 'FOC_Current_Control_tc' completed.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Saturate_Output as hdlsrc/hdlcoderFocClockRatePipelining/Saturate_Output.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/DQ_Current_Control/D_Current_Control as hdlsrc/hdlcoderFocClockRatePipelining/D_Current_Control.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/DQ_Current_Control as hdlsrc/hdlcoderFocClockRatePipelining/DQ_Current_Control.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Clarke_Transform as hdlsrc/hdlcoderFocClockRatePipelining/Clarke_Transform.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Park_Transform as hdlsrc/hdlcoderFocClockRatePipelining/Park_Transform.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Sine_Cosine/Sine_Cosine_LUT as hdlsrc/hdlcoderFocClockRatePipelining/Sine_Cosine_LUT.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Sine_Cosine as hdlsrc/hdlcoderFocClockRatePipelining/Sine_Cosine.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Inverse_Park_Transform as hdlsrc/hdlcoderFocClockRatePipelining/Inverse_Park_Transform.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Inverse_Clarke_Transform as hdlsrc/hdlcoderFocClockRatePipelining/Inverse_Clarke_Transform.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Space_Vector_Modulation as hdlsrc/hdlcoderFocClockRatePipelining/Space_Vector_Modulation.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control as hdlsrc/hdlcoderFocClockRatePipelining/FOC_Current_Control.vhd.

### Generating package file hdlsrc/hdlcoderFocClockRatePipelining/FOC_Current_Control_pkg.vhd.

### Code Generation for 'hdlcoderFocClockRatePipelining' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocClockRatePipelining', '/tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocClockRatePipelining/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocClockRatePipelining/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocClockRatePipelining' complete with 0 errors, 2 warnings, and 4 messages.

### HDL code generation complete.

[クロック レート パイプライン] セクションの [詳細レポート] にクロックレート パイプラインの障害のリストがあります。障害を取り除くために、レポートにリストされている解決法を適用できます。たとえば、障害となっている両方のサブシステムのブロック パラメーター TreatAsAtomicUnit を無効にし、サブシステム内のブロックを、モデルの階層構造内でサブシステムと同じレベルにあるものとして扱います。その後、これらのサブシステムに対してクロックレート パイプラインを実行し、モデルを最適化できます。

set_param([dstHdlDut '/DQ_Current_Control/D_Current_Control'], 'TreatAsAtomicUnit', 'off'); set_param([dstHdlDut '/DQ_Current_Control/Q_Current_Control'], 'TreatAsAtomicUnit', 'off');

HDL コードを生成し、コード生成レポートの [クロック レート パイプライン] セクションを調べて、クロックレート パイプラインの障害がなくなっていることを確認します。コード生成レポートの [クロック レート パイプライン] セクションの詳細については、クロックレート パイプライン レポートを参照してください。

makehdl(dstHdlDut);

### Working on the model <a href="matlab:open_system('hdlcoderFocClockRatePipelining')">hdlcoderFocClockRatePipelining</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocClockRatePipelining/FOC_Current_Control')">hdlcoderFocClockRatePipelining/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocClockRatePipelining', { 'HDL Code Generation' } )">hdlcoderFocClockRatePipelining</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocClockRatePipelining'.

### Begin compilation of the model 'hdlcoderFocClockRatePipelining'...

### Begin compilation of the model 'hdlcoderFocClockRatePipelining'...

### Working on the model 'hdlcoderFocClockRatePipelining'...

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocClockRatePipelining', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderFocClockRatePipelining'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoderFocClockRatePipelining/gm_hdlcoderFocClockRatePipelining.slx')">hdlsrc/hdlcoderFocClockRatePipelining/gm_hdlcoderFocClockRatePipelining.slx</a>

### To highlight blocks that obstruct distributed pipelining, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoderFocClockRatePipelining/highlightDistributedPipeliningBarriers')">hdlsrc/hdlcoderFocClockRatePipelining/highlightDistributedPipeliningBarriers.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoderFocClockRatePipelining/clearhighlighting.m')">hdlsrc/hdlcoderFocClockRatePipelining/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoderFocClockRatePipelining/gm_hdlcoderFocClockRatePipelining_vnl')">gm_hdlcoderFocClockRatePipelining_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderFocClockRatePipelining'.

### MESSAGE: The design requires 800 times faster clock with respect to the base rate = 2e-05.

### Begin VHDL Code Generation for 'FOC_Current_Control_tc'.

### Working on FOC_Current_Control_tc as hdlsrc/hdlcoderFocClockRatePipelining/FOC_Current_Control_tc.vhd.

### Code Generation for 'FOC_Current_Control_tc' completed.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Saturate_Output as hdlsrc/hdlcoderFocClockRatePipelining/Saturate_Output.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/DQ_Current_Control/D_Current_Control as hdlsrc/hdlcoderFocClockRatePipelining/D_Current_Control.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/DQ_Current_Control/Q_Current_Control/Saturate_Output as hdlsrc/hdlcoderFocClockRatePipelining/Saturate_Output_block.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/DQ_Current_Control/Q_Current_Control as hdlsrc/hdlcoderFocClockRatePipelining/Q_Current_Control.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/DQ_Current_Control as hdlsrc/hdlcoderFocClockRatePipelining/DQ_Current_Control.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Clarke_Transform as hdlsrc/hdlcoderFocClockRatePipelining/Clarke_Transform.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Park_Transform as hdlsrc/hdlcoderFocClockRatePipelining/Park_Transform.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Sine_Cosine/Sine_Cosine_LUT as hdlsrc/hdlcoderFocClockRatePipelining/Sine_Cosine_LUT.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Sine_Cosine as hdlsrc/hdlcoderFocClockRatePipelining/Sine_Cosine.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Inverse_Park_Transform as hdlsrc/hdlcoderFocClockRatePipelining/Inverse_Park_Transform.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Inverse_Clarke_Transform as hdlsrc/hdlcoderFocClockRatePipelining/Inverse_Clarke_Transform.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control/Space_Vector_Modulation as hdlsrc/hdlcoderFocClockRatePipelining/Space_Vector_Modulation.vhd.

### Working on hdlcoderFocClockRatePipelining/FOC_Current_Control as hdlsrc/hdlcoderFocClockRatePipelining/FOC_Current_Control.vhd.

### Generating package file hdlsrc/hdlcoderFocClockRatePipelining/FOC_Current_Control_pkg.vhd.

### Code Generation for 'hdlcoderFocClockRatePipelining' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocClockRatePipelining', '/tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocClockRatePipelining/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocClockRatePipelining/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocClockRatePipelining' complete with 0 errors, 2 warnings, and 3 messages.

### HDL code generation complete.

生成されたモデルの最上位のサブシステム内を調べます。生成されたモデルから、設計にクロックレート パイプラインが適用され、速いレートで実行されていることがわかります。生成されたモデルにクロックレート パイプラインが適用されていないサブシステムがある場合は、元のモデルでサブシステムに最適化が設定されていたかどうかを確認します。

open_system(gmHdlDut); set_param(gmHdlModel, 'SimulationCommand', 'update'); set_param(gmHdlDut, 'ZoomFactor', 'FitSystem');

設計の入力でレート変換が発生してクロック レートになります。クロック レートはターゲット周波数により設定され、1/40 MHz、つまり 25 ns となります。すべてのパイプラインがこのレートで導入され、クロック レートで動作します。最後に、出力側の遅延がダウンサンプリング レート変換で置き換えられ、信号がデータ レートに戻っています。元のモデルと比較して、パイプラインをクロック レートで挿入することで、サンプル時間の追加遅延を発生させることなく、新しい設計のクロック周波数が向上しました。

検証モデルとコシミュレーション モデルを使用して、設計の機能的な動作に変更がないかを確認します。詳細については、検証を参照してください。

サブシステムに対するローカルな面積の最適化の適用

遅いパスのレート差は、このパスに沿った計算に複数のクロック サイクルが必要になる可能性があることを意味します。具体的には、許容されるレイテンシがクロックレートの割り当てで定義されます。パイプラインの追加によるクロック周波数の向上に加え、レイテンシの割り当てを利用したハードウェア リソースの再利用が可能です。遅いパス内に StreamingFactor オプションや SharingFactor オプションなどを設定して、リソース共有の最適化を適用します。この節では、リソース共有がクロックレート領域内でどのように適用されるかを示します。

リソース共有がクロックレート パスに適用された場合、HDL Coder は、面積の最適化のためのリソース共有で説明しているように、時間多重化のために共有リソース アーキテクチャをオーバーサンプリングします。ただし、遅いデータパスで共有またはストリーミングが要求された場合は、HDL Coder はオーバーサンプリングなしでリソース共有を実装します。

Park_Transform サブシステムと Inverse_Park_Transform サブシステムの中で、それぞれ 4 つの乗算器が使用されており、これらを共有できる可能性があります。さらに、Clarke_Transform サブシステムと Inverse_Clarke_Transform サブシステムでそれぞれ使用されている 2 つのゲインは、単なる 2 のべき乗のゲインでない限り、共有される可能性があり、結果は乗算ではなくシフトになります。その結果、Inverse_Clarke_Transform のゲインは共有できません。現在のモデルを開き、共有を適用できるサブシステムを強調表示します。

srcHdlModel = 'hdlcoderFocClockRatePipelining'; dstHdlModel = 'hdlcoderFocSharing'; dstHdlDut = [dstHdlModel '/FOC_Current_Control']; gmHdlModel = ['gm_' dstHdlModel]; gmHdlDut = ['gm_' dstHdlDut]; open_system(srcHdlModel); save_system(srcHdlModel,dstHdlModel); open_system(dstHdlDut); hilite_system([dstHdlDut '/Park_Transform']); hilite_system([dstHdlDut '/Inverse_Park_Transform']); hilite_system([dstHdlDut '/Clarke_Transform']);

リソース共有を適用するため、各サブシステムに対して共有する乗算器の数に共有係数を設定します。

hdlset_param([dstHdlDut '/Park_Transform'], 'SharingFactor', 4); hdlset_param([dstHdlDut '/Inverse_Park_Transform'], 'SharingFactor', 4); hdlset_param([dstHdlDut '/Clarke_Transform'], 'SharingFactor', 2); save_system(dstHdlModel);

makehdl コマンドを使用して HDL コードを生成します。

makehdl(dstHdlDut);

### Working on the model <a href="matlab:open_system('hdlcoderFocSharing')">hdlcoderFocSharing</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocSharing/FOC_Current_Control')">hdlcoderFocSharing/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocSharing', { 'HDL Code Generation' } )">hdlcoderFocSharing</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocSharing'.

### Begin compilation of the model 'hdlcoderFocSharing'...

### Begin compilation of the model 'hdlcoderFocSharing'...

### Working on the model 'hdlcoderFocSharing'...

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocSharing', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderFocSharing'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoderFocSharing/gm_hdlcoderFocSharing.slx')">hdlsrc/hdlcoderFocSharing/gm_hdlcoderFocSharing.slx</a>

### To highlight blocks that obstruct distributed pipelining, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoderFocSharing/highlightDistributedPipeliningBarriers')">hdlsrc/hdlcoderFocSharing/highlightDistributedPipeliningBarriers.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoderFocSharing/clearhighlighting.m')">hdlsrc/hdlcoderFocSharing/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoderFocSharing/gm_hdlcoderFocSharing_vnl')">gm_hdlcoderFocSharing_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderFocSharing'.

### MESSAGE: The design requires 800 times faster clock with respect to the base rate = 2e-05.

### Begin VHDL Code Generation for 'FOC_Current_Control_tc'.

### Working on FOC_Current_Control_tc as hdlsrc/hdlcoderFocSharing/FOC_Current_Control_tc.vhd.

### Code Generation for 'FOC_Current_Control_tc' completed.

### Working on hdlcoderFocSharing/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Saturate_Output as hdlsrc/hdlcoderFocSharing/Saturate_Output.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/DQ_Current_Control/D_Current_Control as hdlsrc/hdlcoderFocSharing/D_Current_Control.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/DQ_Current_Control/Q_Current_Control/Saturate_Output as hdlsrc/hdlcoderFocSharing/Saturate_Output_block.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/DQ_Current_Control/Q_Current_Control as hdlsrc/hdlcoderFocSharing/Q_Current_Control.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/DQ_Current_Control as hdlsrc/hdlcoderFocSharing/DQ_Current_Control.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/Clarke_Transform as hdlsrc/hdlcoderFocSharing/Clarke_Transform.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/Park_Transform as hdlsrc/hdlcoderFocSharing/Park_Transform.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/Sine_Cosine/Sine_Cosine_LUT as hdlsrc/hdlcoderFocSharing/Sine_Cosine_LUT.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/Sine_Cosine as hdlsrc/hdlcoderFocSharing/Sine_Cosine.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/Inverse_Park_Transform as hdlsrc/hdlcoderFocSharing/Inverse_Park_Transform.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/Inverse_Clarke_Transform as hdlsrc/hdlcoderFocSharing/Inverse_Clarke_Transform.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control/Space_Vector_Modulation as hdlsrc/hdlcoderFocSharing/Space_Vector_Modulation.vhd.

### Working on hdlcoderFocSharing/FOC_Current_Control as hdlsrc/hdlcoderFocSharing/FOC_Current_Control.vhd.

### Generating package file hdlsrc/hdlcoderFocSharing/FOC_Current_Control_pkg.vhd.

### Code Generation for 'hdlcoderFocSharing' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocSharing', '/tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocSharing/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocSharing/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocSharing' complete with 0 errors, 2 warnings, and 3 messages.

### HDL code generation complete.

生成されたモデルを確認して、HDL Coder が遅いデータパスで使用可能なレイテンシの割り当ての情報を使用してクロック レートで時間多重化を実装していることを確認します。

load_system(gmHdlDut); set_param(gmHdlModel, 'SimulationCommand', 'update'); set_param(gmHdlDut, 'ZoomFactor', 'FitSystem'); hilite_system([gmHdlDut '/ctr_0_799']); hilite_system([gmHdlDut '/Clarke_Transform/Clarke_Transform_shared']); hilite_system([gmHdlDut '/Park_Transform/Park_Transform_shared']); hilite_system([gmHdlDut '/Inverse_Park_Transform/Inverse_Park_Transform_shared']); open_system(gmHdlDut); Simulink.BlockDiagram.arrangeSystem(gmHdlDut);

時間多重化アーキテクチャは、シングルレート共有アーキテクチャとも呼ばれます。これについては、シングルレートのリソース共有アーキテクチャで説明しています。設計のさまざまな領域を Enabled Subsystem を使用してイネーブルおよびディセーブルにするために、グローバル スケジューラが作成されます。イネーブル/ディセーブル制御は、レイテンシの割り当て (0 ~ 799) までカウントする Limited Counter ブロック ctr_0_799 を使用して実装されています。共有領域は、自動で判別されるスケジュールの順序に従ってイネーブルになる Enabled Subsystem として実装されます。この設計には、4 か所で共有された乗算器のグループを含むサブシステムが 2 つ、2 か所で共有された乗算器のグループを含むサブシステムが 1 つあります。リソース共有の結果、設計の乗算器の数は、レイテンシのペナルティなしで 20 から 13 に減少しています。

モデルのフラット化によるグローバルな最適化の適用

グローバルなサブシステム間の最適化は、サブシステム フラット化機能を利用して適用できます。フラット化を使用すると、より多くの数のリソースを階層の同じレベルで共有できます。そのような共有をトリガーするには、最上位のサブシステムで共有またはストリーミングのいずれかを設定します。選択する共有係数の値は上限でなければなりません。適切な値を判断するには、設計のリソース使用率の解析が必要になります。

srcHdlModel = 'hdlcoderFocCurrentFixptHdl'; dstHdlModel = 'hdlcoderFocSharingWithFlattening'; dstHdlDut = [dstHdlModel '/FOC_Current_Control']; gmHdlModel = ['gm_' dstHdlModel]; gmHdlDut = ['gm_' dstHdlDut]; open_system(srcHdlModel); save_system(srcHdlModel,dstHdlModel); open_system(dstHdlDut); hdlset_param(dstHdlModel, 'ClockRatePipelining', 'on'); hdlset_param(dstHdlModel, 'TargetFrequency', 40); hdlset_param(dstHdlModel, 'TreatRatesAsHardwareRates', 'on'); hdlset_param(dstHdlModel, 'DistributedPipelining', 'on'); hdlset_param(dstHdlDut, 'FlattenHierarchy', 'on'); hilite_system([dstHdlDut '/Park_Transform']); hilite_system([dstHdlDut '/Inverse_Park_Transform']); hilite_system([dstHdlDut '/Clarke_Transform']); hilite_system([dstHdlDut '/Inverse_Clarke_Transform']);

Park_Transform サブシステムと Inverse_Park_Transform サブシステムの中で、それぞれ 4 つの乗算器が使用されており、これらを共有できる可能性があります。さらに、Clarke_Transform サブシステムと Inverse_Clarke_Transform サブシステムでそれぞれ使用されている 2 つのゲインは、単なる 2 のべき乗のゲインでない限り、共有される可能性があり、結果は乗算ではなくシフトになります。SharingFactor の値として上限の 4 を選択し、HDL コードを生成します。

hdlset_param(dstHdlDut, 'SharingFactor', 4);

save_system(dstHdlModel);

makehdl(dstHdlDut);

### Working on the model <a href="matlab:open_system('hdlcoderFocSharingWithFlattening')">hdlcoderFocSharingWithFlattening</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocSharingWithFlattening/FOC_Current_Control')">hdlcoderFocSharingWithFlattening/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocSharingWithFlattening', { 'HDL Code Generation' } )">hdlcoderFocSharingWithFlattening</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocSharingWithFlattening'.

### Begin compilation of the model 'hdlcoderFocSharingWithFlattening'...

### Begin compilation of the model 'hdlcoderFocSharingWithFlattening'...

### Working on the model 'hdlcoderFocSharingWithFlattening'...

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocSharingWithFlattening', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderFocSharingWithFlattening'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoderFocSharingWithFlattening/gm_hdlcoderFocSharingWithFlattening.slx')">hdlsrc/hdlcoderFocSharingWithFlattening/gm_hdlcoderFocSharingWithFlattening.slx</a>

### To highlight blocks that obstruct distributed pipelining, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoderFocSharingWithFlattening/highlightDistributedPipeliningBarriers')">hdlsrc/hdlcoderFocSharingWithFlattening/highlightDistributedPipeliningBarriers.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoderFocSharingWithFlattening/clearhighlighting.m')">hdlsrc/hdlcoderFocSharingWithFlattening/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoderFocSharingWithFlattening/gm_hdlcoderFocSharingWithFlattening_vnl')">gm_hdlcoderFocSharingWithFlattening_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderFocSharingWithFlattening'.

### MESSAGE: The design requires 800 times faster clock with respect to the base rate = 2e-05.

### Begin VHDL Code Generation for 'FOC_Current_Control_tc'.

### Working on FOC_Current_Control_tc as hdlsrc/hdlcoderFocSharingWithFlattening/FOC_Current_Control_tc.vhd.

### Code Generation for 'FOC_Current_Control_tc' completed.

### Working on hdlcoderFocSharingWithFlattening/FOC_Current_Control as hdlsrc/hdlcoderFocSharingWithFlattening/FOC_Current_Control.vhd.

### Generating package file hdlsrc/hdlcoderFocSharingWithFlattening/FOC_Current_Control_pkg.vhd.

### Code Generation for 'hdlcoderFocSharingWithFlattening' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocSharingWithFlattening', '/tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocSharingWithFlattening/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocSharingWithFlattening/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocSharingWithFlattening' complete with 0 errors, 2 warnings, and 3 messages.

### HDL code generation complete.

生成されたモデルを確認して、HDL Coder が遅いデータパスで使用可能なレイテンシの割り当ての情報を使用してクロック レートで時間多重化を実装していることを確認します。

open_system(gmHdlDut); set_param(gmHdlModel, 'SimulationCommand', 'update'); set_param(gmHdlDut, 'ZoomFactor', 'FitSystem'); hilite_system([gmHdlDut '/ctr_0_799']); hilite_system([gmHdlDut '/crp_temp_shared']); hilite_system([gmHdlDut '/crp_temp_shared1']); hilite_system([gmHdlDut '/crp_temp_shared2']); hilite_system([gmHdlDut '/crp_temp_shared3']); hilite_system([gmHdlDut '/crp_temp_shared4']);

この設計には、モデル全体で 4 か所以内で共有された乗算器のグループを含むサブシステムが 5 つあります。これらの 5 つのサブシステムは、名前の一部に crp_temp_shared を含みます。

要約すると、設計がフラット化されたことで、設計の乗算器の数は、レイテンシのペナルティなしで 20 から 7 に減少しています。

レイテンシの最小化

高度な操作として、出力 Delay_Register を削除し、代わりに DUT 出力端子のクロックレート パイプラインを許可するオプションを使用することで、出力レイテンシを減らすことができます。

hdlcoderFocSharing モデルのコピーとして新しいモデルを作成し、出力 Delay_Register を削除します。

srcHdlModel = 'hdlcoderFocSharing'; dstHdlModel = 'hdlcoderFocMinLatency'; dstHdlDut = [dstHdlModel '/FOC_Current_Control']; gmHdlModel = ['gm_' dstHdlModel]; gmHdlDut = ['gm_' dstHdlDut]; open_system(srcHdlModel); save_system(srcHdlModel,dstHdlModel); delete_line(dstHdlDut,'Space_Vector_Modulation/1','Delay_Register/1'); delete_line(dstHdlDut,'Delay_Register/1','Phase_Voltage/1'); delete_block([dstHdlDut,'/Delay_Register']) add_line(dstHdlDut,'Space_Vector_Modulation/1','Phase_Voltage/1'); open_system(dstHdlDut);

出力端子のクロックレート パイプラインのオプションは、コンフィギュレーション パラメーター ダイアログ ボックスにあります。[HDL コード生成]、[最適化]、[パイプライン] タブで、[DUT 出力端子のクロック レート パイプラインを許可] オプションをオンにします。このオプションのコマンド ライン プロパティの名前は、ClockRatePipelineOutputPorts です。ClockRatePipelineOutputPorts オプションをオンにし、出力レジスタを削除すると、生成された HDL コードは完全なサンプル ステップを待たずに出力を生成するようになります。代わりに、データの準備ができた時点で、数クロック サイクル以内に出力を生成します。生成された HDL コードは、次のサンプル ステップを待たずにクロック レートで出力を生成します。

hdlset_param(dstHdlModel, 'ClockRatePipelineOutputPorts', 'on'); save_system(dstHdlModel); makehdl(dstHdlDut);

### Working on the model <a href="matlab:open_system('hdlcoderFocMinLatency')">hdlcoderFocMinLatency</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocMinLatency/FOC_Current_Control')">hdlcoderFocMinLatency/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocMinLatency', { 'HDL Code Generation' } )">hdlcoderFocMinLatency</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocMinLatency'.

### Begin compilation of the model 'hdlcoderFocMinLatency'...

### Begin compilation of the model 'hdlcoderFocMinLatency'...

### Working on the model 'hdlcoderFocMinLatency'...

### Clock-rate pipelining was applied on signals connected to the DUT's output ports. The DUT output port values are therefore updated at the clock-rate. The following ports are phase-offset by the stated number of clock cycles.

### Phase of output port 1: 13 clock cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocMinLatency', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderFocMinLatency'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoderFocMinLatency/gm_hdlcoderFocMinLatency.slx')">hdlsrc/hdlcoderFocMinLatency/gm_hdlcoderFocMinLatency.slx</a>

### To highlight blocks that obstruct distributed pipelining, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoderFocMinLatency/highlightDistributedPipeliningBarriers')">hdlsrc/hdlcoderFocMinLatency/highlightDistributedPipeliningBarriers.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoderFocMinLatency/clearhighlighting.m')">hdlsrc/hdlcoderFocMinLatency/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoderFocMinLatency/gm_hdlcoderFocMinLatency_vnl')">gm_hdlcoderFocMinLatency_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderFocMinLatency'.

### MESSAGE: The design requires 800 times faster clock with respect to the base rate = 2e-05.

### Begin VHDL Code Generation for 'FOC_Current_Control_tc'.

### Working on FOC_Current_Control_tc as hdlsrc/hdlcoderFocMinLatency/FOC_Current_Control_tc.vhd.

### Code Generation for 'FOC_Current_Control_tc' completed.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/Clarke_Transform as hdlsrc/hdlcoderFocMinLatency/Clarke_Transform.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Saturate_Output as hdlsrc/hdlcoderFocMinLatency/Saturate_Output.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/DQ_Current_Control/D_Current_Control as hdlsrc/hdlcoderFocMinLatency/D_Current_Control.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/DQ_Current_Control/Q_Current_Control/Saturate_Output as hdlsrc/hdlcoderFocMinLatency/Saturate_Output_block.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/DQ_Current_Control/Q_Current_Control as hdlsrc/hdlcoderFocMinLatency/Q_Current_Control.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/DQ_Current_Control as hdlsrc/hdlcoderFocMinLatency/DQ_Current_Control.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/Inverse_Clarke_Transform as hdlsrc/hdlcoderFocMinLatency/Inverse_Clarke_Transform.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/Inverse_Park_Transform as hdlsrc/hdlcoderFocMinLatency/Inverse_Park_Transform.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/Park_Transform as hdlsrc/hdlcoderFocMinLatency/Park_Transform.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/Sine_Cosine/Sine_Cosine_LUT as hdlsrc/hdlcoderFocMinLatency/Sine_Cosine_LUT.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/Sine_Cosine as hdlsrc/hdlcoderFocMinLatency/Sine_Cosine.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control/Space_Vector_Modulation as hdlsrc/hdlcoderFocMinLatency/Space_Vector_Modulation.vhd.

### Working on hdlcoderFocMinLatency/FOC_Current_Control as hdlsrc/hdlcoderFocMinLatency/FOC_Current_Control.vhd.

### Generating package file hdlsrc/hdlcoderFocMinLatency/FOC_Current_Control_pkg.vhd.

### Code Generation for 'hdlcoderFocMinLatency' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocMinLatency', '/tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocMinLatency/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3692017/tp2693ca09/hdlcoder-ex01953685/hdlsrc/hdlcoderFocMinLatency/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocMinLatency' complete with 0 errors, 2 warnings, and 3 messages.

### HDL code generation complete.

DUT 出力をサンプリングする方法を示す ### Phase of output port 1: というメッセージが makehdl コマンドによって生成されたことに注目してください。このメッセージに示されるクロック サイクル数は DUT の出力をサンプリングできる速度、すなわち、設計のレイテンシです。設計の合計レイテンシは、データレートのサンプル ステップ 20  から数ナノ秒まで減少しています。

から数ナノ秒まで減少しています。

生成されたモデルを確認して、出力がクロック レートの 25 ナノ秒で動作する新しい DUT サブシステムが作成されていることを確認します。

open_system(gmHdlDut); set_param(gmHdlModel, 'SimulationCommand', 'update'); set_param(gmHdlDut, 'ZoomFactor', 'FitSystem');

このオプションを使用すると、生成された HDL コードに元のシミュレーション モデルにはなかった追加のレイテンシが導入されます。その際に、出力端子のサンプル時間がクロック レートに変更されています。テストハーネスでは設計の出力はデータ レートで生成されると想定しているため、これによって妥当性確認と検証のフローで結果に誤差が生じる可能性があります。この問題に対処するために、検証モデルではダウンサンプリング レート変換を挿入して出力をデータ レートに戻します。そのため、検証モデルでは、引き続きデータ レートで出力を比較します。HDL テストベンチでは、生成された HDL の出力がクロック レートであるため、新しい DUT 出力をクロック レートで比較します。

概要

クロックレート パイプラインは、設計の遅いパスを最適化してパイプライン化する手法です。クロックレート パイプラインでは、HDL Coder の次の構造と最適化に対するパイプラインが必ずクロック レートで導入されます。

パイプライン化された数学演算: sqrt または recip のニュートン・ラフソン法、三角関数の CORDIC アルゴリズムなど、いくつかの数学ブロックはマルチサイクルのパイプライン化された HDL 実装を実装します。ブロックが遅いパスで動作する場合、これらのパイプラインはクロック レートで導入されます。

浮動小数点マッピング: 上記のように、浮動小数点ライブラリ マッピングでは、浮動小数点演算の実装時にクロックレート パイプラインを利用します。

パイプライン方式の最適化: 入力/出力パイプライン、適応パイプライン、分散型パイプラインなど、すべてのパイプライン方式の最適化で、遅いパスにクロックレートのレジスタが使用されます。

リソース共有とストリーミング: リソース共有アーキテクチャの時間多重化はクロック レートで実装されます。

遅いパスとして識別されるのは、パスで Simulink の遅いサンプル時間を使用している場合と、オーバーサンプリング値が 1 より大きい場合です。クロックレート パイプラインを使用すると、設計の合計レイテンシを損なわずに設計の速度と面積の特性を改善できます。