面積の最適化のためのリソース共有

この例では、HDL Coder™ でサブシステム レベルの共有最適化を使用する方法を示します。

はじめに

面積効率の高いハードウェアを実装するにはリソース共有を使用します。これは、HDL Coder でサポートされているサブシステムレベルの最適化です。

HDL Coder では、既定では、Simulink® ブロックがハードウェア モジュール実装に 1 対 1 でマッピングされたハードウェアが実装されます。リソース共有最適化を使用すると、N 個の機能的に等価な Simulink ブロックを単一のハードウェア モジュールに N 対 1 でマッピングし、ハードウェア リソースを共有できます。ユーザーは SharingFactor 実装パラメーターを使用して N を指定します。

時間多重化されたアーキテクチャでは面積の最適化を完了するまでのレイテンシが長くなるため、HDL Coder は、どのリソースが共有されているかに応じてタイミングの不一致を管理します。共有リソースが基本サンプル レートで動作していれば、リソース共有は局所的なマルチレート アーキテクチャとして実装されます (この例では、このアーキテクチャについて説明します)。共有リソースが基本サンプル レートよりも遅いサンプル レートで動作している場合は、HDL Coder はクロックレート パイプラインを呼び出して、レート差で定義されるレイテンシの割り当てを使用した実装を合成します。この場合、リソース共有アーキテクチャはシングル レート実装となり、共有されたすべての演算を完了するまでに複数のタイム ステップを要します。この実装の詳細については、シングルレートのリソース共有アーキテクチャで説明しています。

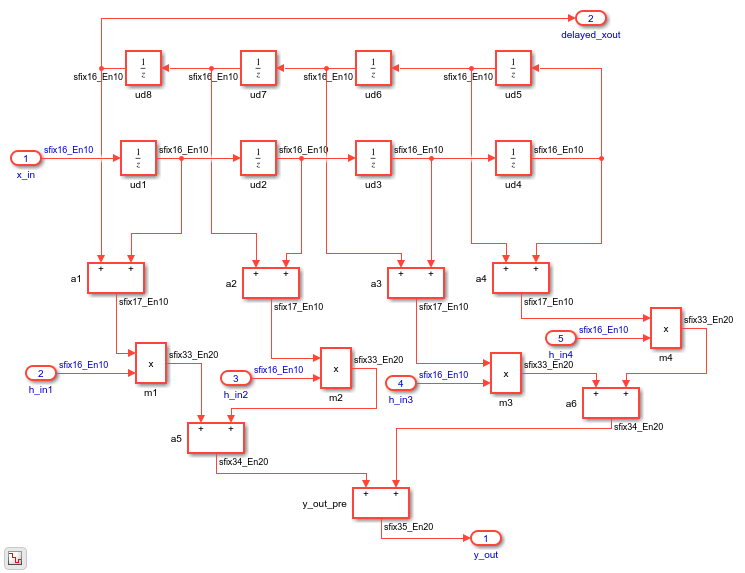

この例では、リソース共有の局所的なマルチレート アーキテクチャについても説明します。次の対称 FIR フィルター モデルについて考えます。機能的に等価な 4 つの Product ブロックがあり、ハードウェアの 4 つの乗算器にマッピングされています。リソース利用レポートに、使用されているハードウェア リソースのリストが表示されます。

load_system('sfir_fixed'); open_system('sfir_fixed/symmetric_fir'); hdlset_param('sfir_fixed', 'ResourceReport', 'on'); makehdl('sfir_fixed/symmetric_fir');

### Working on the model <a href="matlab:open_system('sfir_fixed')">sfir_fixed</a>

### Generating HDL for <a href="matlab:open_system('sfir_fixed/symmetric_fir')">sfir_fixed/symmetric_fir</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('sfir_fixed', { 'HDL Code Generation' } )">sfir_fixed</a> for HDL code generation parameters.

### Running HDL checks on the model 'sfir_fixed'.

### Begin compilation of the model 'sfir_fixed'...

### Working on the model 'sfir_fixed'...

### Working on... <a href="matlab:configset.internal.open('sfir_fixed', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_sfir_fixed'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/sfir_fixed/gm_sfir_fixed.slx')">hdlsrc/sfir_fixed/gm_sfir_fixed.slx</a>

### Begin VHDL Code Generation for 'sfir_fixed'.

### Working on sfir_fixed/symmetric_fir as hdlsrc/sfir_fixed/symmetric_fir.vhd.

### Code Generation for 'sfir_fixed' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/sfir_fixed', '/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/sfir_fixed/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/sfir_fixed/symmetric_fir_report.html

### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

N 対 1 のマッピングのためのリソースの共有

面積リソースを削減するために、サブシステムの SharingFactor パラメーターを正の整数値に設定して共有最適化を呼び出すことができます。このパラメーターは、N 対 1 のハードウェア マッピングにおける N を指定します。この例では、Product ブロックが 4 つあるため、SharingFactor を 4 に設定して HDL を生成することで 1 つの乗算器をもつ HDL コードを生成します。

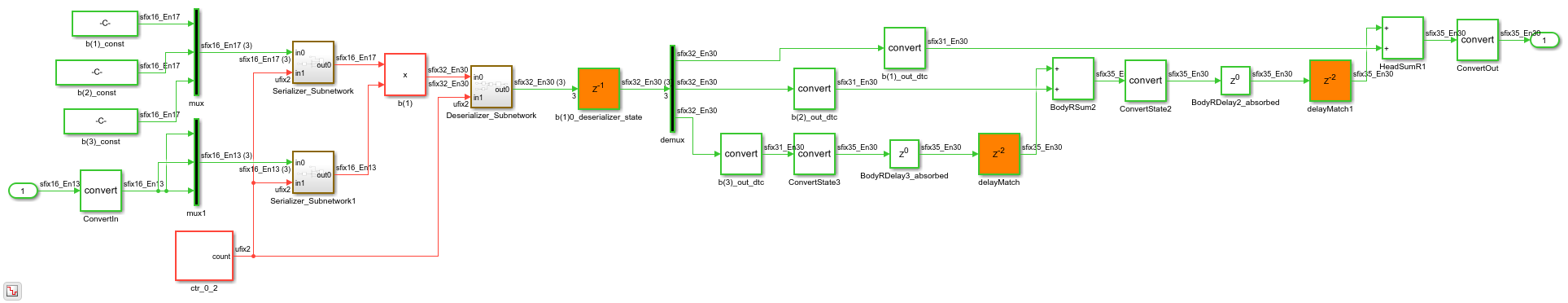

コード生成モデルに共有アーキテクチャが反映されます。共有ブロックへの入力が共有リソース全体で速いレートで時間多重化されます (この例では 4 倍の速さであり、赤で示してあります)。その後、出力がそれぞれのコンシューマーに遅いレートで送られます (緑で示してあります)。

hdlset_param('sfir_fixed/symmetric_fir', 'SharingFactor', 4); hdlset_param('sfir_fixed', 'GenerateValidationModel', 'on'); makehdl('sfir_fixed/symmetric_fir'); open_system('gm_sfir_fixed/symmetric_fir'); set_param('gm_sfir_fixed', 'SimulationCommand', 'update');

### Working on the model <a href="matlab:open_system('sfir_fixed')">sfir_fixed</a>

### Generating HDL for <a href="matlab:open_system('sfir_fixed/symmetric_fir')">sfir_fixed/symmetric_fir</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('sfir_fixed', { 'HDL Code Generation' } )">sfir_fixed</a> for HDL code generation parameters.

### Running HDL checks on the model 'sfir_fixed'.

### Begin compilation of the model 'sfir_fixed'...

### Working on the model 'sfir_fixed'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('sfir_fixed', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_sfir_fixed'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/sfir_fixed/gm_sfir_fixed.slx')">hdlsrc/sfir_fixed/gm_sfir_fixed.slx</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/sfir_fixed/gm_sfir_fixed_vnl')">gm_sfir_fixed_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'sfir_fixed'.

### MESSAGE: The design requires 4 times faster clock with respect to the base rate = 1.

### Begin VHDL Code Generation for 'symmetric_fir_tc'.

### Working on symmetric_fir_tc as hdlsrc/sfir_fixed/symmetric_fir_tc.vhd.

### Code Generation for 'symmetric_fir_tc' completed.

### Working on sfir_fixed/symmetric_fir as hdlsrc/sfir_fixed/symmetric_fir.vhd.

### Generating package file hdlsrc/sfir_fixed/symmetric_fir_pkg.vhd.

### Code Generation for 'sfir_fixed' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/sfir_fixed', '/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/sfir_fixed/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/sfir_fixed/symmetric_fir_report.html

### HDL check for 'sfir_fixed' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

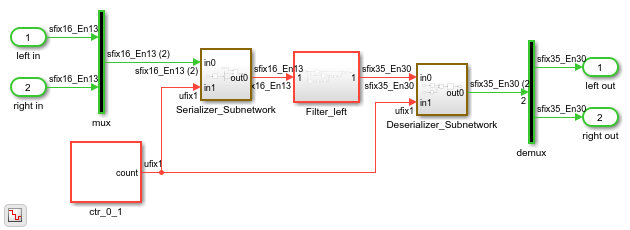

共有最適化は、時分割多重化を使用して実装されます。Simulink では共有リソースの出力を事前定義されたサンプル レートでサンプリングする必要があります。HDL Coder は、共有リソースをデータ レートよりも速いレートでオーバークロックします。前述の例では、Sharingfactor が 4 に設定されているため、共有リソースの入力のマルチプレクサー (シリアライザー) と出力のデマルチプレクサー (デシリアライザー) を含む共有アーキテクチャが入力データの 4 倍のレートで動作します。

遅延の均衡化と機能的等価性

リソース共有アーキテクチャの時間多重化を実装するレート変換によって、追加のレイテンシが導入されます。機能的等価性を維持するために、遅延の均衡化により、一致する遅延が並列のマージ パスに挿入されます。生成された検証モデルで、共有ハードウェア アーキテクチャの演算を元のモデルと比較して、機能的等価性を検証できます。

sim('gm_sfir_fixed_vnl'); open_system('gm_sfir_fixed_vnl/Compare/Assert_y_out/compare: y_out') open_system('gm_sfir_fixed_vnl/Compare/Assert_delayed_xout/compare: delayed_xout')

SharingFactor による乗法的オーバーサンプリングの制御

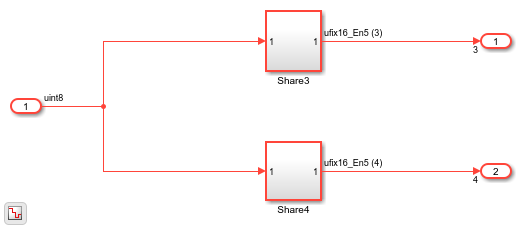

設計全体の正味のオーバーサンプリングは、モデルで設定されているすべての SharingFactor の値の LCM と等しくなります。hdlcoder_uniform_oversampling.slx の例について考えます。これには 2 つのサブシステムが含まれており、サブシステム Share3 には共有できる Gain ブロックが 3 つ、Share4 には共有できる Gain ブロックが 4 つあります。

saved_warning_state = warning('off', 'hdlcoder:makehdl:DeprecateMaxOverSampling'); warning('off', 'hdlcoder:makehdl:DeprecateMaxComputationLatency'); load_system('hdlcoder_uniform_oversampling'); open_system('hdlcoder_uniform_oversampling/Subsystem'); set_param('hdlcoder_uniform_oversampling', 'SimulationCommand', 'update'); hdlsaveparams('hdlcoder_uniform_oversampling/Subsystem');

%% Set Model 'hdlcoder_uniform_oversampling' HDL parameters

hdlset_param('hdlcoder_uniform_oversampling', 'GenerateValidationModel', 'on');

hdlset_param('hdlcoder_uniform_oversampling', 'HDLSubsystem', 'hdlcoder_uniform_oversampling');

% Set SubSystem HDL parameters

hdlset_param('hdlcoder_uniform_oversampling/Subsystem/Share3', 'SharingFactor', 3);

% Set SubSystem HDL parameters

hdlset_param('hdlcoder_uniform_oversampling/Subsystem/Share4', 'SharingFactor', 4);

Share3 の SharingFactor は 3 に設定され、Share4 の SharingFactor は 4 に設定されています。HDL Coder は各サブシステムに局所的なリソース共有を適用するため、結果として HDL 実装に必要なオーバーサンプリングは LCM(3, 4)| = 12 倍になります。このオーバーサンプリングが HDL コード生成時に報告されます。

makehdl('hdlcoder_uniform_oversampling/Subsystem');

### Working on the model <a href="matlab:open_system('hdlcoder_uniform_oversampling')">hdlcoder_uniform_oversampling</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_uniform_oversampling/Subsystem')">hdlcoder_uniform_oversampling/Subsystem</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_uniform_oversampling', { 'HDL Code Generation' } )">hdlcoder_uniform_oversampling</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_uniform_oversampling'.

### Begin compilation of the model 'hdlcoder_uniform_oversampling'...

### Working on the model 'hdlcoder_uniform_oversampling'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_uniform_oversampling', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_uniform_oversampling'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling.slx')">hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling.slx</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling_vnl')">gm_hdlcoder_uniform_oversampling_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoder_uniform_oversampling'.

### MESSAGE: The design requires 12 times faster clock with respect to the base rate = 0.1.

### Begin VHDL Code Generation for 'Subsystem_tc'.

### Working on Subsystem_tc as hdlsrc/hdlcoder_uniform_oversampling/Subsystem_tc.vhd.

### Code Generation for 'Subsystem_tc' completed.

### Working on hdlcoder_uniform_oversampling/Subsystem/Share3 as hdlsrc/hdlcoder_uniform_oversampling/Share3.vhd.

### Working on hdlcoder_uniform_oversampling/Subsystem/Share4 as hdlsrc/hdlcoder_uniform_oversampling/Share4.vhd.

### Working on hdlcoder_uniform_oversampling/Subsystem as hdlsrc/hdlcoder_uniform_oversampling/Subsystem.vhd.

### Generating package file hdlsrc/hdlcoder_uniform_oversampling/Subsystem_pkg.vhd.

### Code Generation for 'hdlcoder_uniform_oversampling' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling', '/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling/Subsystem_report.html

### HDL check for 'hdlcoder_uniform_oversampling' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

このオーバーサンプリングの乗法効果を回避する 1 つの方法は、すべてのサブシステムの SharingFactor を使用可能なオーバーサンプリングの割り当てに設定することです。上記の例では、オーバーサンプリングの割り当てが 4 倍のみであれば、Share3 と Share4 の両方の SharingFactor を 4 に設定します。この場合、HDL Coder は、SharingFactor よりも少ないリソースを共有し、残りのサイクルはアイドルにしておくことができます。

hdlset_param('hdlcoder_uniform_oversampling/Subsystem/Share3', 'SharingFactor', 4); makehdl('hdlcoder_uniform_oversampling/Subsystem');

### Working on the model <a href="matlab:open_system('hdlcoder_uniform_oversampling')">hdlcoder_uniform_oversampling</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_uniform_oversampling/Subsystem')">hdlcoder_uniform_oversampling/Subsystem</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_uniform_oversampling', { 'HDL Code Generation' } )">hdlcoder_uniform_oversampling</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_uniform_oversampling'.

### Begin compilation of the model 'hdlcoder_uniform_oversampling'...

### Working on the model 'hdlcoder_uniform_oversampling'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_uniform_oversampling', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_uniform_oversampling'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling.slx')">hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling.slx</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoder_uniform_oversampling/gm_hdlcoder_uniform_oversampling_vnl')">gm_hdlcoder_uniform_oversampling_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoder_uniform_oversampling'.

### MESSAGE: The design requires 4 times faster clock with respect to the base rate = 0.1.

### Begin VHDL Code Generation for 'Subsystem_tc'.

### Working on Subsystem_tc as hdlsrc/hdlcoder_uniform_oversampling/Subsystem_tc.vhd.

### Code Generation for 'Subsystem_tc' completed.

### Working on hdlcoder_uniform_oversampling/Subsystem/Share3 as hdlsrc/hdlcoder_uniform_oversampling/Share3.vhd.

### Working on hdlcoder_uniform_oversampling/Subsystem/Share4 as hdlsrc/hdlcoder_uniform_oversampling/Share4.vhd.

### Working on hdlcoder_uniform_oversampling/Subsystem as hdlsrc/hdlcoder_uniform_oversampling/Subsystem.vhd.

### Generating package file hdlsrc/hdlcoder_uniform_oversampling/Subsystem_pkg.vhd.

### Code Generation for 'hdlcoder_uniform_oversampling' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling', '/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_uniform_oversampling/Subsystem_report.html

### HDL check for 'hdlcoder_uniform_oversampling' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

オーバーサンプリング係数が LCM(4,4) = 4 になります。この値がコード生成時に報告されています。ベスト プラクティスとして、SharingFactor の値は使用可能なオーバーサンプリングの割り当てに設定することをお勧めします。設計に含まれる共有可能なリソースが指定した SharingFactor の値よりも少ない場合、HDL Coder は、共有可能な使用できるリソースを共有し、それらを SharingFactor の値でオーバークロックします。リソース共有と共にオーバークロックを使用する他の最適化 (ストリーミングなど) も適用する場合や、リソース共有を複数の入れ子になったサブシステムで適用する場合は、この一般的なガイドラインに従うとオーバーサンプリング係数が大きくなる可能性があります。

ブロック サポート、Atomic サブシステム、拡張

HDL Coder は、4 つのブロック タイプのリソース共有をサポートします。Product、Gain、Atomic サブシステム、および MATLAB Function です。MATLAB Function ブロックについては、固定小数点型の MATLAB Datapath アーキテクチャを使用します。このアーキテクチャは、浮動小数点型に対する既定の設定です。MATLAB Function ブロックの [HDL ブロック プロパティ] ダイアログ ボックスで HDL アーキテクチャを指定できます。

機能的に等価な Product ブロックおよび Gain ブロックの共有は、HDL 実装において乗算器を共有することを意味します。2 つの Product ブロックは、次の場合に機能的に等価となります。

入力および出力のデータ型が同じである。

ブロック パラメーター設定が同じである。

HDL ブロック プロパティが同じである。

Gain ブロックの場合は、さらに定数の値とデータ型も同じである場合に機能的に等価となります。ゲイン定数のデータ型が 2 つの Gain ブロックで同じであれば、ゲイン定数の値が異なっていても、HDL Coder はそれらを共有できます。同様に、Gain ブロックを定数入力をもつ Product ブロックとして実装できる場合は、データ型が設計内の別の Product ブロックと同じであれば、HDL Coder はそれらを共有できます。

3 つ目のブロック タイプの Atomic サブシステムは、Atomic サブシステム内にカプセル化されている機能的に等価なロジックを共有するのに使用できます。2 つの Atomic サブシステムは、次の場合に機能的に等価となり共有できます。

Simulink チェックサムが同じである。

HDL ブロック プロパティが同じである。

Atomic サブシステムの共有

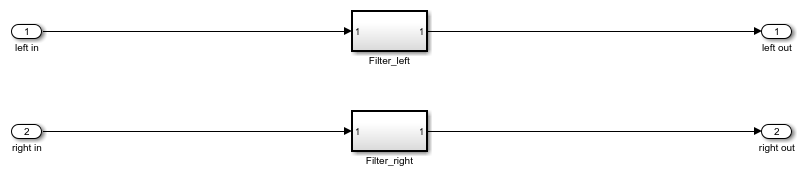

次の例は、左右のチャネルに同じフィルターを適用するオーディオ フィルター モデルを示しています。HDL Coder では、既定ではハードウェアに 2 つのフィルター モジュールを生成します。

load_system('hdlcoder_audiofiltering'); open_system('hdlcoder_audiofiltering/Audio filter');

2 つのオーディオ チャネルのフィルターを共有するには、それらを含むサブシステムで SharingFactor の値を 2 と指定します。これにより、次に示すように、1 つのフィルターのみを使用するアーキテクチャが生成されます。

hdlset_param('hdlcoder_audiofiltering/Audio filter', 'SharingFactor', 2); makehdl('hdlcoder_audiofiltering/Audio filter'); open_system('gm_hdlcoder_audiofiltering/Audio filter'); set_param('gm_hdlcoder_audiofiltering', 'SimulationCommand', 'update');

### Working on the model <a href="matlab:open_system('hdlcoder_audiofiltering')">hdlcoder_audiofiltering</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_audiofiltering/Audio filter')">hdlcoder_audiofiltering/Audio filter</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_audiofiltering', { 'HDL Code Generation' } )">hdlcoder_audiofiltering</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_audiofiltering'.

### Begin compilation of the model 'hdlcoder_audiofiltering'...

### Working on the model 'hdlcoder_audiofiltering'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_audiofiltering', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_audiofiltering'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx')">hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_audiofiltering'.

### MESSAGE: The design requires 2 times faster clock with respect to the base rate = 0.00012207.

### Begin VHDL Code Generation for 'Audio_filter_tc'.

### Working on Audio_filter_tc as hdlsrc/hdlcoder_audiofiltering/Audio_filter_tc.vhd.

### Code Generation for 'Audio_filter_tc' completed.

### Working on hdlcoder_audiofiltering/Audio filter/Filter_left as hdlsrc/hdlcoder_audiofiltering/Filter_left.vhd.

### Working on hdlcoder_audiofiltering/Audio filter as hdlsrc/hdlcoder_audiofiltering/Audio_filter.vhd.

### Generating package file hdlsrc/hdlcoder_audiofiltering/Audio_filter_pkg.vhd.

### Code Generation for 'hdlcoder_audiofiltering' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering', '/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering/Audio_filter_report.html

### HDL check for 'hdlcoder_audiofiltering' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

階層全体でのリソース共有の機会

SharingFactor はサブシステムレベルのパラメーターであるため、異なる階層レベルのサブシステムごとに、異なる共有の値を指定できます。オーディオ フィルターの例では、各チャネルのフィルターで 3 つの Gain ブロックをそれぞれ使用しています。

open_system('hdlcoder_audiofiltering/Audio filter/Filter_left');

上位の階層レベルでのリソースの共有

最上位の DUT で SharingFactor の値を 2 と指定して、2 つのチャネルでフィルターを共有できます。それぞれのフィルター サブシステムで SharingFactor の値を 3 と指定して、各チャネルで 3 つの Gain ブロックの共有を有効にできます。ここで HDL コードを生成すると、左右のフィルターが共有されます。最上位の階層レベルのフィルターが 1 つだけになります。

hdlset_param('hdlcoder_audiofiltering/Audio filter', 'SharingFactor', 2); hdlset_param('hdlcoder_audiofiltering/Audio filter/Filter_left', 'SharingFactor', 3); hdlset_param('hdlcoder_audiofiltering/Audio filter/Filter_right', 'SharingFactor', 3); makehdl('hdlcoder_audiofiltering/Audio filter'); open_system('gm_hdlcoder_audiofiltering/Audio filter'); set_param('gm_hdlcoder_audiofiltering', 'SimulationCommand', 'update');

### Working on the model <a href="matlab:open_system('hdlcoder_audiofiltering')">hdlcoder_audiofiltering</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_audiofiltering/Audio filter')">hdlcoder_audiofiltering/Audio filter</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_audiofiltering', { 'HDL Code Generation' } )">hdlcoder_audiofiltering</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_audiofiltering'.

### Begin compilation of the model 'hdlcoder_audiofiltering'...

### Working on the model 'hdlcoder_audiofiltering'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 2 cycles.

### Output port 2: 2 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_audiofiltering', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_audiofiltering'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx')">hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_audiofiltering'.

### MESSAGE: The design requires 6 times faster clock with respect to the base rate = 0.00012207.

### Begin VHDL Code Generation for 'Audio_filter_tc'.

### Working on Audio_filter_tc as hdlsrc/hdlcoder_audiofiltering/Audio_filter_tc.vhd.

### Code Generation for 'Audio_filter_tc' completed.

### Working on hdlcoder_audiofiltering/Audio filter/Filter_left as hdlsrc/hdlcoder_audiofiltering/Filter_left.vhd.

### Working on hdlcoder_audiofiltering/Audio filter as hdlsrc/hdlcoder_audiofiltering/Audio_filter.vhd.

### Generating package file hdlsrc/hdlcoder_audiofiltering/Audio_filter_pkg.vhd.

### Code Generation for 'hdlcoder_audiofiltering' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering', '/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdlcoder_audiofiltering/Audio_filter_report.html

### HDL check for 'hdlcoder_audiofiltering' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

下位の階層レベルでのリソースの共有

下位の階層レベルにある 3 つの Gain ブロック (フィルター サブシステムの内部) も共有されています。リソース使用が減少し、乗算器が 6 つから 1 つだけに減っています。

open_system('gm_hdlcoder_audiofiltering/Audio filter/Filter_left'); set_param('gm_hdlcoder_audiofiltering', 'SimulationCommand', 'update');

最適化と共有の組み合わせ

リソース共有は、ストリーミグ最適化などの他の最適化と組み合わせることができます。

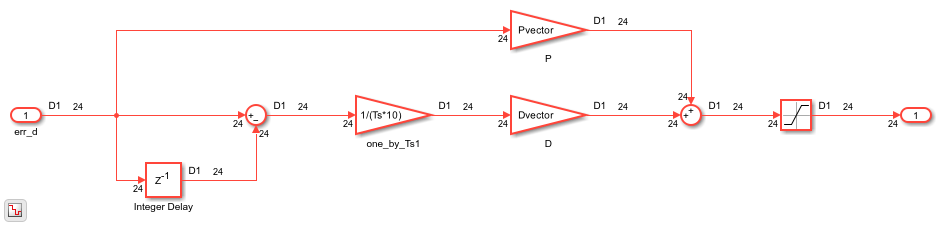

次のモデルについて考えてみます。24 要素のベクトルのデータパスと 3 つのベクトルの Gain ブロックがあり、既定では 72 の乗算器にマッピングされます。ストリーミングでベクトルのデータパスをスカラー化し、共有で 3 つの Gain ブロックを共有できます。

load_system('hdl_areaopt1'); open_system('hdl_areaopt1/Controller'); set_param('hdl_areaopt1', 'SimulationCommand', 'update');

設計で使用する乗算器をストリーミングと共有によって 1 つに削減

両方の最適化を呼び出すために、StreamingFactor を 24 に設定し、SharingFactor を 3 に設定します。前者で乗算器の数が 72 から 3 に減ります。後者で 3 つのスカラーの乗算器が 1 つに削減されます。

hdlset_param('hdl_areaopt1/Controller', 'StreamingFactor', 24); hdlset_param('hdl_areaopt1/Controller', 'SharingFactor', 3); makehdl('hdl_areaopt1/Controller'); open_system('gm_hdl_areaopt1/Controller'); set_param('gm_hdl_areaopt1', 'SimulationCommand', 'update');

### Working on the model <a href="matlab:open_system('hdl_areaopt1')">hdl_areaopt1</a>

### Generating HDL for <a href="matlab:open_system('hdl_areaopt1/Controller')">hdl_areaopt1/Controller</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdl_areaopt1', { 'HDL Code Generation' } )">hdl_areaopt1</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdl_areaopt1'.

### Begin compilation of the model 'hdl_areaopt1'...

### Working on the model 'hdl_areaopt1'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 2 cycles.

### Working on... <a href="matlab:configset.internal.open('hdl_areaopt1', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdl_areaopt1'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdl_areaopt1/gm_hdl_areaopt1.slx')">hdlsrc/hdl_areaopt1/gm_hdl_areaopt1.slx</a>

### Begin VHDL Code Generation for 'hdl_areaopt1'.

### MESSAGE: The design requires 72 times faster clock with respect to the base rate = 2.

### Begin VHDL Code Generation for 'Controller_tc'.

### Working on Controller_tc as hdlsrc/hdl_areaopt1/Controller_tc.vhd.

### Code Generation for 'Controller_tc' completed.

### Working on hdl_areaopt1/Controller as hdlsrc/hdl_areaopt1/Controller.vhd.

### Generating package file hdlsrc/hdl_areaopt1/Controller_pkg.vhd.

### Code Generation for 'hdl_areaopt1' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdl_areaopt1', '/tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdl_areaopt1/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3698416/tp5c5cf959/hdlcoder-ex96854632/hdlsrc/hdl_areaopt1/Controller_report.html

### HDL check for 'hdl_areaopt1' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.