HDL Coder での複数のクロックの使用

この例では、HDL Coder™ で複数の最上位の同期クロック入力端子をインスタンス化する方法を示します。

クロック モードの概要

HDL Coder には 2 つのクロック モードがあります。一方のモードでは、テスト対象デバイス (DUT) に対して単一のクロック入力が生成されます。もう一方のモードでは、DUT の Simulink® レートごとに同期基本クロック入力が生成されます。HDL Coder では、既定では DUT に単一のクロック端子を使用する HDL 設計が作成されます。単一クロック モードでは、Simulink モデルに複数のレートが存在する場合、モデルの遅いレートで実行される部分のクロックを制御するためにタイミング コントローラーが作成されます。タイミング コントローラーは、必要なレートと位相の情報をもつ一連のクロック イネーブルを生成して設計のクロックを制御します。生成される各クロック イネーブルは基本クロック レートよりも整数倍遅いレートになります。各出力信号のレートは、出力データをサンプリングする正しいタイミングを示すクロック イネーブルの出力信号に関連付けられます。

複数クロック同期モードでは、生成されるコードに DUT への基本入力として一連のクロック端子が含まれます。各クロック端子はモデルの個々のレートに対応します。レート間の変換には、そのレートのクロックと位相がずれた特定のレートのクロック イネーブルが必要です。それらの位相がずれた信号はタイミング コントローラーで生成されます。複数のクロック モデルには複数のタイミング コントローラーが必要になることがあります。

マルチレート モデルで複数のクロックを使用する場合は、それぞれの Simulink レートで遅延ブロックなどの順序論理を追加することをお勧めします。特定の Simulink レートに順序論理がないと、そのレートの個別のクロック端子は HDL Coder で生成されません。たとえば、Downsample ブロックで構成されるマルチレート モデルでは、Downsample ブロックの後に単位遅延ブロックを追加して、そのダウンサンプリング レートのクロック端子を生成します。

最初の例では、単一クロック モードでマルチレート CIC 内挿フィルターを使用します。この例では、異なるレートで実行される複数の出力信号をもつモデルを示すために、フィルターの入力が出力としても表示されます。

load_system('hdlcoder_clockdemo'); open_system('hdlcoder_clockdemo/DUT'); set_param('hdlcoder_clockdemo', 'SimulationCommand', 'update');

単一クロック モードの DUT のタイミング インターフェイス

単一クロック モードでは、DUT の HDL コードに、追加される Simulink ブロック線図には表示されない一連の 3 つの信号が含まれます。それらは、クロック、基本クロック イネーブル、およびリセットの信号を含むクロック バンドルとしてまとめられます。これらの信号は VHDL エンティティ宣言に含まれ、生成されるコード全体で使用されます。

hdlset_param('hdlcoder_clockdemo', 'Traceability', 'on'); makehdl('hdlcoder_clockdemo/DUT');

### Working on the model <a href="matlab:open_system('hdlcoder_clockdemo')">hdlcoder_clockdemo</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_clockdemo/DUT')">hdlcoder_clockdemo/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_clockdemo', { 'HDL Code Generation' } )">hdlcoder_clockdemo</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_clockdemo'.

### Begin compilation of the model 'hdlcoder_clockdemo'...

### Working on the model 'hdlcoder_clockdemo'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_clockdemo', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_clockdemo'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_clockdemo/gm_hdlcoder_clockdemo.slx')">hdlsrc/hdlcoder_clockdemo/gm_hdlcoder_clockdemo.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_clockdemo'.

### Begin VHDL Code Generation for 'DUT_tc'.

### Working on DUT_tc as hdlsrc/hdlcoder_clockdemo/DUT_tc.vhd.

### Code Generation for 'DUT_tc' completed.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_clockdemo', 'Traceability')">Traceability</a>

### Working on hdlcoder_clockdemo/DUT as hdlsrc/hdlcoder_clockdemo/DUT.vhd.

### Generating package file hdlsrc/hdlcoder_clockdemo/DUT_pkg.vhd.

### Code Generation for 'hdlcoder_clockdemo' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_clockdemo', '/tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_clockdemo/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_clockdemo/DUT_report.html

### HDL check for 'hdlcoder_clockdemo' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

単一クロック モードのクロック概要レポート

HDL DUT コードのファイル コメント ブロックにクロック概要情報が表示されます。単一クロック モードでは、このレポートに各クロック イネーブル出力信号のサンプル レートの詳細を示すテーブルが含まれます。また、各ユーザー出力信号とそれに関連付けられたクロック イネーブル出力信号を示すテーブルもレポートに含まれます。HTML レポートの生成時、クロック概要レポートも毎回生成されます。

複数クロック同期 HDL コードの生成

この設計の複数の同期クロックを生成するには、ClockInputs プロパティを multiple に設定しなければなりません。コマンド ラインで makehdl を使用して ClockInputs プロパティを変更するか、[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成]、[グローバル設定] タブで クロック入力の設定を Multiple に変更します。

makehdl('hdlcoder_clockdemo/DUT', 'ClockInputs', 'multiple');

### Working on the model <a href="matlab:open_system('hdlcoder_clockdemo')">hdlcoder_clockdemo</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_clockdemo/DUT')">hdlcoder_clockdemo/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_clockdemo', { 'HDL Code Generation' } )">hdlcoder_clockdemo</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_clockdemo'.

### Begin compilation of the model 'hdlcoder_clockdemo'...

### Working on the model 'hdlcoder_clockdemo'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_clockdemo', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_clockdemo'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_clockdemo/gm_hdlcoder_clockdemo.slx')">hdlsrc/hdlcoder_clockdemo/gm_hdlcoder_clockdemo.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_clockdemo'.

### Begin VHDL Code Generation for 'DUT_tc'.

### Working on DUT_tc as hdlsrc/hdlcoder_clockdemo/DUT_tc.vhd.

### Code Generation for 'DUT_tc' completed.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_clockdemo', 'Traceability')">Traceability</a>

### Working on hdlcoder_clockdemo/DUT as hdlsrc/hdlcoder_clockdemo/DUT.vhd.

### Generating package file hdlsrc/hdlcoder_clockdemo/DUT_pkg.vhd.

### Code Generation for 'hdlcoder_clockdemo' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_clockdemo', '/tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_clockdemo/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_clockdemo/DUT_report.html

### HDL check for 'hdlcoder_clockdemo' complete with 0 errors, 1 warnings, and 1 messages.

### HDL code generation complete.

複数クロック モードのクロック概要情報

複数クロック モードでは、クロック概要の内容が異なります。こちらのレポートにはクロックのテーブルが含まれます。このテーブルには、基本 DUT クロックごとに 1 つのエントリが含まれます。これは、モデルの各クロックと最も速いクロックの間の相対クロック比を示します。単一クロック モードと同様、この情報は HDL DUT のファイル コメント ブロックと HTML レポートの両方で提供されます。

複数クロック モードでのクロック バンドル信号名の変更

複数クロック モードでは、ClockInputPort、ResetInputPort、ClockEnableInputPort などのパラメーターを使用して各サンプル レートに対応する名前を設定することで、クロック、リセット、およびクロック イネーブル信号の名前をカスタマイズできます。これらの名前を指定する際には、cell 配列形式を使用して、異なるレート間で適切なマッピングが確実に行われるようにします。クロック バンドル名のカスタマイズの詳細については、マルチレート モデルからのコード生成を参照してください。

hdlset_param('hdlcoder_clockdemo','ClockInputPort',{'clk1','clk2'}) hdlset_param('hdlcoder_clockdemo','ResetInputPort',{'reset1','reset2'}) hdlset_param('hdlcoder_clockdemo','ClockEnableInputPort',{'clk_en1','clk_en2'}) makehdl('hdlcoder_clockdemo/DUT', 'ClockInputs', 'multiple');

### Working on the model <a href="matlab:open_system('hdlcoder_clockdemo')">hdlcoder_clockdemo</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_clockdemo/DUT')">hdlcoder_clockdemo/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_clockdemo', { 'HDL Code Generation' } )">hdlcoder_clockdemo</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_clockdemo'.

### Begin compilation of the model 'hdlcoder_clockdemo'...

### Working on the model 'hdlcoder_clockdemo'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_clockdemo', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_clockdemo'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_clockdemo/gm_hdlcoder_clockdemo.slx')">hdlsrc/hdlcoder_clockdemo/gm_hdlcoder_clockdemo.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_clockdemo'.

### Begin VHDL Code Generation for 'DUT_tc'.

### Working on DUT_tc as hdlsrc/hdlcoder_clockdemo/DUT_tc.vhd.

### Code Generation for 'DUT_tc' completed.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_clockdemo', 'Traceability')">Traceability</a>

### Working on hdlcoder_clockdemo/DUT as hdlsrc/hdlcoder_clockdemo/DUT.vhd.

### Generating package file hdlsrc/hdlcoder_clockdemo/DUT_pkg.vhd.

### Code Generation for 'hdlcoder_clockdemo' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_clockdemo', '/tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_clockdemo/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_clockdemo/DUT_report.html

### HDL check for 'hdlcoder_clockdemo' complete with 0 errors, 1 warnings, and 1 messages.

### HDL code generation complete.

複数クロック モードと HDL Coder の最適化

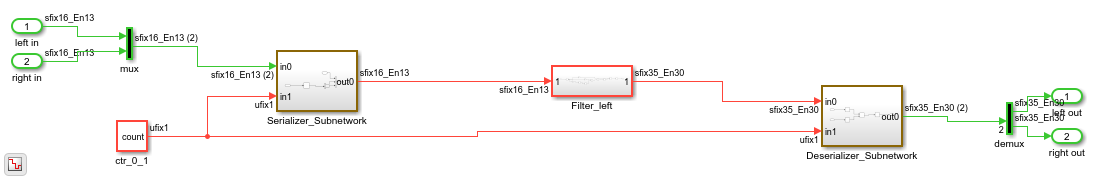

複数の同期クロックは、Simulink レートが 1 つだけの設計にも便利です。各種の最適化において、元のモデルで示されているクロック レートよりも速いクロック レートが必要になることがあります。次の例は、左右のチャネルに同じフィルターを適用するオーディオ フィルター モデルを示しています。HDL Coder では、既定ではハードウェアに 2 つのフィルター モジュールを生成します。この構成では、単一クロック モードの場合と同様に、複数クロック モードでもクロックは 1 つしか生成されません。

bdclose hdlcoder_clockdemo; load_system('hdlcoder_audiofiltering'); open_system('hdlcoder_audiofiltering/Audio filter'); hdlset_param('hdlcoder_audiofiltering', 'ClockInputs', 'Multiple'); hdlset_param('hdlcoder_audiofiltering/Audio filter', 'SharingFactor', 0); makehdl('hdlcoder_audiofiltering/Audio filter', 'Traceability', 'on');

### Working on the model <a href="matlab:open_system('hdlcoder_audiofiltering')">hdlcoder_audiofiltering</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_audiofiltering/Audio filter')">hdlcoder_audiofiltering/Audio filter</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_audiofiltering', { 'HDL Code Generation' } )">hdlcoder_audiofiltering</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_audiofiltering'.

### Begin compilation of the model 'hdlcoder_audiofiltering'...

### Working on the model 'hdlcoder_audiofiltering'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_audiofiltering', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_audiofiltering'...

### Copying DUT to the generated model....

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx')">hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_audiofiltering'.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_audiofiltering', 'Traceability')">Traceability</a>

### Working on hdlcoder_audiofiltering/Audio filter/Filter_left as hdlsrc/hdlcoder_audiofiltering/Filter_left.vhd.

### Working on hdlcoder_audiofiltering/Audio filter as hdlsrc/hdlcoder_audiofiltering/Audio_filter.vhd.

### Code Generation for 'hdlcoder_audiofiltering' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_audiofiltering', '/tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_audiofiltering/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_audiofiltering/Audio_filter_report.html

### HDL check for 'hdlcoder_audiofiltering' complete with 0 errors, 1 warnings, and 0 messages.

### HDL code generation complete.

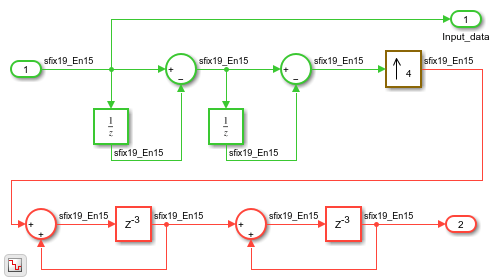

複数クロック モードでのリソース共有の使用

左右の同一のチャネルの Atomic サブシステムにリソース共有を適用すると、フィルターが 1 つだけ生成されます。Simulink のタイミング要件を満たすには、下の図に示すように、単一のフィルターを元の Simulink モデルの 2 倍のクロック レートで実行します。リソース共有の最適化で 2 番目のクロック レートが作成されるため、ユーザーは複数クロック同期モードを使用して両方のレートの外部クロックを提供できます。この構成では、複数クロック モードでもクロックは 1 つしか生成されません。次のメッセージが表示されます。

The design requires 2 times faster clock with respect to the base rate = 0.00012207.

bdclose gm_hdlcoder_audiofiltering; hdlset_param('hdlcoder_audiofiltering/Audio filter', 'SharingFactor', 2); makehdl('hdlcoder_audiofiltering/Audio filter', 'Traceability', 'on'); open_system('gm_hdlcoder_audiofiltering/Audio filter'); set_param('gm_hdlcoder_audiofiltering', 'SimulationCommand', 'update');

### Working on the model <a href="matlab:open_system('hdlcoder_audiofiltering')">hdlcoder_audiofiltering</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_audiofiltering/Audio filter')">hdlcoder_audiofiltering/Audio filter</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_audiofiltering', { 'HDL Code Generation' } )">hdlcoder_audiofiltering</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_audiofiltering'.

### Begin compilation of the model 'hdlcoder_audiofiltering'...

### Working on the model 'hdlcoder_audiofiltering'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_audiofiltering', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_audiofiltering'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx')">hdlsrc/hdlcoder_audiofiltering/gm_hdlcoder_audiofiltering.slx</a>

### Begin VHDL Code Generation for 'hdlcoder_audiofiltering'.

### MESSAGE: The design requires 2 times faster clock with respect to the base rate = 0.00012207.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_audiofiltering', 'Traceability')">Traceability</a>

### Working on hdlcoder_audiofiltering/Audio filter/Filter_left as hdlsrc/hdlcoder_audiofiltering/Filter_left.vhd.

### Working on hdlcoder_audiofiltering/Audio filter as hdlsrc/hdlcoder_audiofiltering/Audio_filter.vhd.

### Generating package file hdlsrc/hdlcoder_audiofiltering/Audio_filter_pkg.vhd.

### Code Generation for 'hdlcoder_audiofiltering' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_audiofiltering', '/tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_audiofiltering/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3702271/tpa4c9511c/hdlcoder-ex81165063/hdlsrc/hdlcoder_audiofiltering/Audio_filter_report.html

### HDL check for 'hdlcoder_audiofiltering' complete with 0 errors, 1 warnings, and 1 messages.

### HDL code generation complete.