コシミュレーション モデルの生成

要件

この機能を使用するには、HDL Verifier™ のライセンスが必要です。

DUT サブシステムに未接続の出力端子がないことを確認します。未接続のブロック端子の終端とブロックのコメント化の使用を参照してください。

コシミュレーション モデルとは

コシミュレーション モデルは、Simulink® シミュレーションおよび設計の HDL シミュレーターとのコシミュレーション用に構成され自動的に生成された Simulink モデルです。HDL Coder™ はテスト ベンチ生成プロセスの一部としてコシミュレーション モデルの自動生成をサポートします。

コシミュレーション モデルの内容は次のとおりです。

Simulink サブシステムで実現された、設計の動作モデル。

HDL Verifier を使用して設計をコシミュレートするように構成された対応する HDL Cosimulation ブロック。HDL Coder は、HDL Cosimulation ブロックを Siemens® ModelSim™、Cadence Incisive®、Synopsys® VCS®、または Xilinx® Vivado® のいずれかのシミュレーターで使用できるように構成します。

指定したテスト ベンチのスティミュラスから算出されたテスト入力データ。

DUT および HDL cosimulation の出力およびこれらの信号間のエラーの観察と比較ができる Scope ブロック。

DUT からのスティミュラスと応答信号を取得して、それらを使用してコシミュレーションを駆動する Goto ブロックおよび From ブロック。

元の DUT の出力とコシミュレーションの出力との差異をレポートする比較/アサーション メカニズム。

モデルの生成に加えて、コシミュレーション ツールを起動して構成する TCL スクリプトが HDL Coder で生成されます。スクリプト ファイル内のコメントは、コシミュレーション ツール用にコード ジェネレーターによって定義されたクロック、リセット、およびその他のタイミング信号の情報を記述します。

モデル コンフィギュレーション パラメーターを使用したコシミュレーション モデルの生成

この例では、コシミュレーション モデルを生成するプロセスを説明します。モデル例 hdl_cosim_demo1 は簡単な MAC (積和演算) アルゴリズムを実装します。MATLAB® コマンド ラインでこのモデル名を入力してモデルを開きます。

openExample('hdl_cosim_demo1');次の図は最上位モデルを示しています。

DUT は MAC サブシステムです。

コシミュレーション モデルの生成はテスト ベンチの生成時に実行されます。ベスト プラクティスとして、以下のようにテスト ベンチを生成する前に HDL コードを生成します。

[コンフィギュレーション パラメーター] ダイアログ ボックスを開きます。Simulink モデルの空白を右クリックし、[モデル コンフィギュレーション パラメーター] を選択します。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] ペインで、[HDL を生成] を

hdl_cosim_demo1/MACに設定します。[適用] をクリックします。

[生成] をクリックします。次のような進行状況を示すメッセージが HDL Coder で表示されます。

### Applying HDL Code Generation Control Statements ### Starting HDL Check. ### HDL Check Complete with 0 error, 0 warning and 0 message. ### Begin VHDL Code Generation ### Working on hdl_cosim_demo1/MAC as hdlsrc\MAC.vhd ### HDL Code Generation Complete.

次に、コシミュレーション モデルの生成を含めるようテスト ベンチ オプションを構成します。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [テスト ベンチ] ペインを選択します。

ドロップダウン メニューで [シミュレーション ツール] を選択します。次に、[コシミュレーション モデル] チェック ボックスをオンにします。

必要なテスト ベンチ オプションを構成します。HDL Coder で生成されたスクリプト ファイルにオプション設定が記録されます (コシミュレーション スクリプト ファイルを参照)。

[適用] をクリックします。

次に、テスト ベンチ コードとコシミュレーション モデルを生成します。

[テスト ベンチ] ペインの下部で [テスト ベンチを生成] をクリックします。次のような進行状況を示すメッセージが HDL Coder で表示されます。

### Begin TestBench Generation ### Generating new cosimulation model: gm_hdl_cosim_demo1_mq0.mdl ### Generating new cosimulation tcl script: hdlsrc/gm_hdl_cosim_demo1_mq0_tcl.m ### Cosimulation Model Generation Complete. ### Generating Test bench: hdlsrc\MAC_tb.vhd ### Please wait ... ### HDL TestBench Generation Complete.

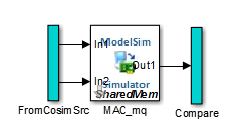

テスト ベンチの生成が完了すると、生成されたコシミュレート モデルが HDL Coder で開きます。次の図は生成されたモデルを示しています。

生成されたモデルを保存します。生成されたモデルは、保存しない限りメモリにのみに存在します。

コード生成メッセージに示されるように、通常の HDL テスト ベンチ ファイルに加えて以下のファイルが HDL Coder で生成されます。

コシミュレーション モデル (

gm_hdl_cosim_demo1_mq)TCL コシミュレーション スクリプトおよびコシミュレーション モデル (

gm_hdl_cosim_demo1_mq_tcl.m) の設定に関する情報を含むファイル

生成されたコシミュレーション モデルおよびスクリプトの命名規則で説明されているように、生成されたファイルの名前はモデル名から派生されます。

次の節生成されたモデルの構造ではモデルの機能を説明しています。コシミュレーションを実行する前に、これらの機能を理解しておいてください。

生成されたモデルの構造

生成されたモデルに配置されたコントロールを使用してコシミュレーションを設定して起動できます。この節では、MAC サブシステムの例から生成されたモデルについて説明します。

シミュレーション パス

モデルは 2 つの並列信号のパスで構成されています。モデル ウィンドウの上半分に位置する "シミュレーション パス" は元の DUT とほぼ同一です。シミュレーション パスの目的は通常の Simulink シミュレーションを実行し、コシミュレーションの結果と比較するための基準信号を提供することです。次の図にシミュレーション パスを示します。

ToCosimSrc および ToCosimSink とラベル付けされた 2 つのサブシステムはシミュレーション パスのパフォーマンスに影響を与えません。これらのサブシステムの目的は、DUT のスティミュラスと応答信号を取得して HDL cosimulation ブロックとのルートを確立することです (シミュレーションとコシミュレーション パス間の信号の経路指定を参照してください)。

コシミュレーション パス

モデル ウィンドウの下半分に位置する "コシミュレーション パス" には、生成された HDL Cosimulation ブロックが含まれます。次の図にコシミュレーション パスを示します。

FromCosimSrc サブシステムは、DUT を駆動する入力信号と同じ入力信号を受信します。gm_hdl_cosim_demo1_mq0 モデル内で、サブシステムは HDL Cosimulation ブロックにそのまま入力を渡します。この段階で、一部のデータ型の信号はさらに処理が必要です (シミュレーションとコシミュレーション パス間の信号の経路指定を参照してください)。

コシミュレーション パスの最後にある Compare サブシステムは、コシミュレーションの出力をシミュレーション パスによって生成された基準出力と比較します。この比較で誤差が検出されると、Compare サブシステム内の Assertion ブロックによって警告メッセージが表示されます。必要であれば、アサーションを無効にし、Compare サブシステムの他の処理を制御することができます。詳細については、アサーションおよびスコープの表示の制御を参照してください。

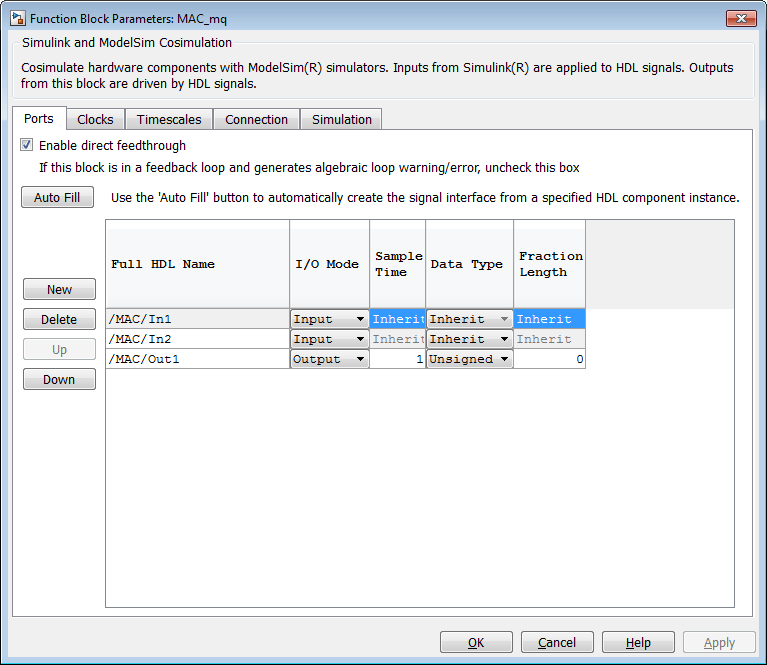

HDL Coder では HDL Cosimulation ブロックに、DUT のコンパイルされた I/O インターフェイスが事前設定されます。次の図は、Mac_mq HDL Cosimulation ブロックの [Port] ペインを示しています。

HDL Coder によって、[Full HDL Name]、[Sample Time]、[Data Type] およびモデルに必要な他のフィールドが設定されます。また、HDL Coder では、[Timescales] ペインおよび [Tcl] ペインの他の HDL Cosimulation ブロック パラメーターも構成されます。

ヒント

HDL Coder では、生成された HDL Cosimulation ブロックが [共有メモリ] 接続メソッド用に構成されます。

Start Simulator コントロール

ModelSim または Incisive® ユーザー - Start Simulator コントロールをダブルクリックすると、選択されたコシミュレーション ツールが起動され、スタートアップ コマンドがツールへ渡されます。Start Simulator アイコンに、次の図に示すスタートアップ コマンドが表示されます。

Start Simulator アイコンをダブルクリックしたときに実行されるコマンドによりコシミュレーション ツールが起動され設定されますが、コシミュレーションの実行は行われません。生成されたモデルでコシミュレーションを実行する方法は、コシミュレーションの起動で説明されています。

Synopsys VCS ユーザー - Start Simulator コントロールをダブルクリックすると、選択されたコシミュレーション ツールが起動され、スタートアップ コマンドがツールに渡されます。次の図は Synopsys VCS シミュレーターの Start Simulator アイコンを示しています。

Start Simulator アイコンをダブルクリックしたときに実行されるコマンドによりコシミュレーション ツールが起動され設定されますが、コシミュレーションの実行は行われません。生成されたモデルでコシミュレーションを実行する方法は、Synopsys VCS のコシミュレーションの起動で説明されています。

Vivado シミュレーター ユーザー - Start Simulator コントロールをダブルクリックすると、共有ライブラリ (DLL ファイル) が再生成されます。Start Simulator アイコンに、次の図に示す情報が表示されます。

シミュレーションとコシミュレーション パス間の信号の経路指定

生成されたモデルは、Goto ブロックおよび From ブロックを使用してシミュレーションとコシミュレーション パス間の信号の経路を指定します。たとえば、ToCosimSrc サブシステム内の Goto ブロックは各 DUT の入力信号を対応する FromCosimSrc サブシステム内の From ブロックにルートします。次の図は、各サブシステム内の Goto ブロックおよび From ブロックを示しています。

上の図は簡単なスカラー入力を示しています。複雑なベクトル データ型の信号はさらに処理が必要です。詳細は、生成されたコシミュレーション モデル内の複素信号およびベクトル信号を参照してください。

アサーションおよびスコープの表示の制御

Compare サブシステムにより、スコープの信号およびアサーションからの警告メッセージの表示を制御できます。次の図は gm_hdl_cosim_demo1_mq0 モデルの Compare サブシステムを示しています。

DUT の各出力について、アサーション チェック サブシステム (Assert_OutN ) が HDL Coder で生成されます。このサブシステムは元の DUT の出力 (dut ref) とそれに対応するコシミュレーションの出力 (cosim) の差分 (err) を算出します。サブシステムはこの比較結果を Assertion ブロックへルートします。比較結果がゼロではない場合、Assertion ブロックは誤差をレポートします。

次の図は gm_hdl_cosim_demo1_mq0 モデルの Assert_Out1 サブシステムを示しています。

このサブシステムは、モデルの最上位での表示のため、dut ref、cosim および err 信号も Scope ブロックにルートします。

既定の設定では、生成されたコシミュレーション モデルはすべてのアサーションとすべての Scope ブロックの表示を有効にします。アサーションを無効にしたり、Scope ブロックを非表示にするには、Compare サブシステムのボタンを使用します。

ヒント

アサーション メッセージは警告であり、シミュレーションは停止しません。

コシミュレーションの起動

生成されたモデルでコシミュレーションを実行するには、次の手順に従います。

Compareサブシステムをダブルクリックして Scopes ブロックとアサーションの設定を構成します。コシミュレーションの開始前に Scope ブロックの表示またはアサーションの警告を無効にする場合は、次の図に示す

Compareサブシステムのボタンを使用します。

Start Simulator コントロールをダブルクリックします。

Start Simulator コントロールによって HDL シミュレーター (この場合、Siemens ModelSim で使用する HDL Verifier) が起動されます。

これにより、HDL シミュレーターによってスタートアップ スクリプトが実行されます。この例では、スタートアップ スクリプトは

gm_hdl_cosim_demo1_mq0_tcl.m内に配置された Tcl コマンドで構成されています。HDL シミュレーターによるスタートアップ スクリプトの実行が完了すると、次のようなメッセージが表示されます。# Ready for cosimulation...

生成されたモデルの Simulink エディター内でシミュレーションを開始します。

コシミュレーションの実行中、HDL シミュレーターは次のようなメッセージを表示します。

# Running Simulink Cosimulation block. # Chip Name: --> hdl_cosim_demo1/MAC # Target language: --> vhdl # Target directory: --> hdlsrc # Fri Jun 05 4:26:34 PM Eastern Daylight Time 2009 # Simulation halt requested by foreign interface. # done

Scope ブロックの表示を有効にしている場合、コシミュレーションの最後に比較スコープに次の信号が表示されます。

cosim:HDL Cosimulation ブロックによる結果の出力信号。dut ref:DUTからの基準出力信号。err:これらの 2 つの出力の差分 (誤差)。

次の図はこれらの信号を示しています。

Synopsys VCS のコシミュレーションの起動

Synopsys VCS シミュレーター用の生成されたモデルでコシミュレーションを実行するには、次の手順に従います。

Compareサブシステムをダブルクリックして Scopes ブロックとアサーションの設定を構成します。コシミュレーションの開始前に Scope ブロックの表示またはアサーションの警告を無効にする場合は、次の図に示す

Compareサブシステムのボタンを使用します。

Start Simulator コントロールをダブルクリックします。

Start Simulator コントロールによって HDL シミュレーター (この場合、Synopsys VCS で使用する HDL Verifier) が起動されます。

これにより、HDL シミュレーターによってスタートアップ スクリプトが実行されます。この例では、スタートアップ スクリプトは

gm_hdl_cosim_demo1_vc_cosim.m内に配置されたlaunchVCS(HDL Verifier) 関数で構成されています。HDL シミュレーターによるスタートアップ スクリプトの実行が完了すると、VCS シミュレーターが起動します。VCS コマンド プロンプトで次のコマンドを実行して、Simulink シミュレーターと VCS の間の接続を確立します。

run

このコマンドにより、HDL シミュレーターのコシミュレーションの準備が整います。

生成されたモデルの Simulink エディター内でシミュレーションを開始します。

Scope ブロックの表示を有効にしている場合、コシミュレーションの最後に比較スコープに次の信号が表示されます。

cosim:HDL Cosimulation ブロックによる結果の出力信号。dut ref:DUTからの基準出力信号。err:これらの 2 つの出力の差分 (誤差)。

VCS コマンド プロンプトで次のコマンドを実行して、生成されたテスト ベンチについてのコード カバレッジ レポートを生成します。

do cosimVCS.postsim.tcl

メモ

コード カバレッジ レポートは、[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [テスト ベンチ] ペインで [HDL コード カバレッジ] を選択した場合にのみ生成できます。

コシミュレーションを再開するには、VCS コマンド プロンプトで次のコマンドを実行します。

restart do cosimVCS.presim.tcl run

コシミュレーション スクリプト ファイル

生成されたスクリプト ファイルには以下の 2 つのセクションがあります。

コシミュレーションに関連するモデル設定を記述するコメント セクション。

TCL コードの複数の行を変数に格納する関数

tclCmds。コシミュレーションを起動すると、コシミュレーション ツールによってこれらのコマンドが実行されます。

ヘッダー コメント セクション

以下のリストは、hdl_cosim_demo1 モデル用に生成されたスクリプト ファイルのコメント セクションを示しています。

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % Auto generated cosimulation 'tclstart' script %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % Source Model : hdl_cosim_demo1.mdl % Generated Model : gm_hdl_cosim_demo1.mdl % Cosimulation Model : gm_hdl_cosim_demo1_mq.mdl % % Source DUT : gm_hdl_cosim_demo1_mq/MAC % Cosimulation DUT : gm_hdl_cosim_demo1_mq/MAC_mq % % File Location : hdlsrc/gm_hdl_cosim_demo1_mq_tcl.m % Created : 2009-06-16 10:51:01 % % Generated by MATLAB 7.9 and HDL Coder 1.6 %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % ClockName : clk % ResetName : reset % ClockEnableName : clk_enable % % ClockLowTime : 5ns % ClockHighTime : 5ns % ClockPeriod : 10ns % % ResetLength : 20ns % ClockEnableDelay : 10ns % HoldTime : 2ns %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % ModelBaseSampleTime : 1 % OverClockFactor : 1 %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % Mapping of DutBaseSampleTime to ClockPeriod % % N = (ClockPeriod / DutBaseSampleTime) * OverClockFactor % 1 sec in Simulink corresponds to 10ns in the HDL % Simulator(N = 10) % %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%% % ResetHighAt : (ClockLowTime + ResetLength + HoldTime) % ResetRiseEdge : 27ns % ResetType : async % ResetAssertedLevel : 1 % % ClockEnableHighAt : (ClockLowTime + ResetLength + ClockEnableDelay + HoldTime) % ClockEnableRiseEdge : 37ns %%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%

コメント セクションは以下のサブセクションで構成されています。

ヘッダー コメント: このセクションは、生成されたモデルとそのソースおよび生成された DUT とそのソースのファイル名を記述します。

テスト ベンチの設定: このセクションは、コシミュレーション モデルの生成に影響する

makehdltbプロパティ値を記述します。生成された Tcl スクリプトは、これらの値を使用してコシミュレーション ツールを初期化します。サンプル時間情報: 次の 2 つのセクションは、モデルの基本サンプル時間とオーバーサンプリング係数を記述します。HDL Coder は

ModelBaseSampleTimeとOverClockFactorを使用して、モデルのクロック周期を HDL コシミュレーションのクロック周期にマップします。クロック、クロック イネーブルおよびリセットの波形: このセクションは、

clk、clk_enableおよびreset信号のデューティ比の計算を記述します。

Tcl コマンド セクション

以下のリストは、 hdl_cosim_demo1 モデル用に生成されたスクリプト ファイルの Tcl コマンド セクションを示しています。

function tclCmds = gm_hdl_cosim_demo1_mq_tcl

tclCmds = {

'do MAC_compile.do',...% Compile the generated code

'vsimulink work.MAC',...% Initiate cosimulation

'add wave /MAC/clk',...% Add wave commands for chip input signals

'add wave /MAC/reset',...

'add wave /MAC/clk_enable',...

'add wave /MAC/In1',...

'add wave /MAC/In2',...

'add wave /MAC/ce_out',...% Add wave commands for chip output signals

'add wave /MAC/Out1',...

'set UserTimeUnit ns',...% Set simulation time unit

'puts ""',...

'puts "Ready for cosimulation..."',...

};

end生成されたコシミュレーション モデル内の複素信号およびベクトル信号

複素数またはベクトル データ型の入力信号は、コシミュレーション パスに追加の要素を挿入する必要があります。この節では、これらの要素を説明します。

複素信号

生成されたコシミュレーション モデルは複素数入力を実数部と虚数部に自動的に分けます。次の図は、2 つの複素数入力信号を受信する FromCosimSrc サブシステムを示しています。このサブシステムは、入力をサブシステムの出力に渡す前に実数部と虚数部に分けます。

このモデルは、コシミュレーション パス全体に渡って、実数部と虚数部の分離を維持します。Compare サブシステムは、信号要素の比較とスコープ表示を、実数部と虚数部でそれぞれ実行します。

ベクトル信号

生成されたコシミュレーション モデルはベクトル入力を平坦化します。次の図は、次元 2 の 2 つのベクトル入力信号を受信する FromCosimSrc サブシステムを示しています。このサブシステムは、入力をサブシステムの出力に渡す前にスカラーに平坦化します。

コマンド ラインからのコシミュレーション モデルの生成

コマンド ラインからコシミュレーション モデルを生成するには、GenerateCosimModel プロパティを makehdltb 関数に渡します。GenerateCosimModel は次のいずれかのプロパティ値を取ります。

'ModelSim':Siemens ModelSim を HDL Verifier で使用するために構成されたコシミュレーション モデルを生成します。'Incisive':Cadence Incisive を HDL Verifier で使用するために構成されたコシミュレーション モデルを生成します。'VCS':Synopsys VCS を HDL Verifier で使用するために構成されたコシミュレーション モデルを生成します。'Vivado Simulator':Xilinx Vivado を HDL Verifier で使用するために構成されたコシミュレーション モデルを生成します。

次のコマンドでは、makehdltb は Siemens ModelSim を HDL Verifier で使用するために構成されたコシミュレーション モデルを生成します。

makehdltb('hdl_cosim_demo1/MAC','GenerateCosimModel','ModelSim');

生成されたコシミュレーション モデルおよびスクリプトの命名規則

生成されたコシミュレーション モデルの命名規則は以下のとおりです。

prefix_modelname_toolid_suffix、ここで、

prefixは、文字列gmです。modelnameは、生成されたモデルの名前です。toolidは、[使用するコシミュレーション モデル:] で選択された HDL シミュレーターを示す識別子です。オプションを選択します。有効なtoolid文字列は'mq'、'in'、'vc'、または'vs'です。suffix は生成されたモデルごとに一意の名前を付けるための整数です。suffix は、そのモデルでテスト ベンチを生成するたびにインクリメントされます。たとえば、元のモデルの名前が

testの場合、連続して生成されるコシミュレーション モデルの名前はgm_test_toolid_0、gm_test_toolid_1などのようになります。

生成されたコシミュレーション スクリプトの命名規則は、ファイル名の拡張子が .m であることを除き、モデルの命名規則と同じです。

コシミュレーション モデル生成の制限

コシミュレーション モデルの生成用にモデルを構成する場合、以下の制限に注意してください。

シミュレーション パス内で、DUT へのソース ブロックのサンプル時間を明示的に指定してください。ソース ブロックの既定のサンプル時間 (

-1) の使用は、生成されたモデルのコシミュレーション パスでサンプル時間の伝播の問題を起こす場合があります。HDL Coder のコシミュレーション モデルの生成では、連続サンプル時間はサポートされていません。シミュレーション パス内のソース ブロックには、サンプル時間

0またはInfを使用しないでください。[クロックの入力] を

[複数]に設定すると、HDL Coder ではコシミュレーション モデルの生成はサポートされません。組み合わせ出力パス (生成されたコード内にレジスタがない場合に発生) は、コシミュレーション内で 1 サイクルの余分なレイテンシが発生します。シミュレーションとコシミュレーションとの出力の比較における不一致を回避するため、HDL Cosimulation ブロックの [Ports] ペインにある [直達を許可] オプションが自動的に選択されます。

代わりに、出力パイプラインを指定することでレイテンシを回避することもできます (OutputPipelineを参照してください)。これにより、コード生成中に出力が完全に登録されます。

HDL Cosimulation ブロックでは double データ型はサポートしていません。HDL コードおよびコシミュレーション モデルを生成する場合は、シミュレーション パス内での double データ型の使用は避けてください。