このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

生成された IP コアの実行と検証

IP コア設計から生成されたビットストリームをターゲット FPGA デバイス上で実行、検証します。入力は、デバイスの FPGA 部分に生成されたビットストリームです。出力は、ターゲット FPGA で実行している、シミュレートおよび検証した設計です。ワークフローの詳細については、FPGA および SoC ハードウェアをターゲットにする方法の概要を参照してください。

オブジェクト

関数

トピック

- ターゲット FPGA ボードまたは SoC デバイスのプログラム

ターゲット Intel または Xilinx ハードウェアをプログラムする方法。

- Choose a Method to Interact with IP Cores on Target Hardware

Choose a software interface method to interact with IP cores running on target hardware.

- FPGA I/O ホスト インターフェイス スクリプトの生成と管理

ホスト インターフェイス スクリプトがどのようなものであるかを示し、ホスト インターフェイス スクリプトを生成して管理する方法を説明する。

- Use FPGA I/O to Rapidly Prototype HDL IP Core

Create and author a host interface script by configuring interfaces and port mapping information to control HDL IP core.

- 生成された HDL IP コアの JTAG AXI Manager を使用したデバッグと制御

リファレンス設計への HDL Verifier AXI Manager IP の自動挿入を指定する。

- Debug Write Registers Using Readback in Generated IP Cores

This example describes the different techniques to read the input registers such as AXI4 or AXI4-Lite in your design.

- FPGA Data Capture を使用した IP コアのデバッグ

この例では、HDL Coder™ で生成する IP コアを FPGA Data Capture のみを使用してデバッグする方法と AXI Manager および FPGA Data Capture の両方を一緒に使用してデバッグする方法を示します。

- HDL Coder によるテスト ポイント信号のモデル化およびデバッグ

モデル内の信号にテスト ポイントを追加し、生成された HDL コードで、それらの信号をデバッグする方法を示す例。

- Debug IP Core Using Hardware-Software Deployment

Debug a Zynq® design using HDL Coder™ and Embedded Coder® features.

- Prototype IP Core on Zynq with MATLAB FPGA I/O Host Interface

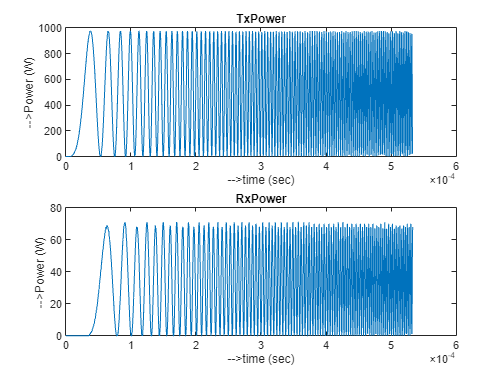

Implement a QPSK communication algorithm on a AMD® Zynq radio using MATLAB for signal transmission and reception.