FPGA I/O ホスト インターフェイス スクリプトの生成と管理

ホスト インターフェイス スクリプトを使用して、MATLAB® からハードウェア上でアルゴリズムのプロトタイプを作成できます。ホスト インターフェイス スクリプトには、ハードウェアに接続してハードウェアでアルゴリズムを実行しながら操作するために使用できる単純な MATLAB コマンドが含まれています。たとえば、パラメーターを調整したり、データを取得して詳細な解析を行ったりすることができます。

前提条件

生成されたホスト インターフェイス スクリプトを実行するには、ハードウェア ボードが必要です。ハードウェア ボードをセットアップする方法の詳細については、Guided Hardware Setup for AMD Boardsを参照してください。

Xilinx® Vivado® などのサードパーティ製合成ツールの最新バージョンが必要です。HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアを参照してください。MATLAB セッションでは、関数

hdlsetuptoolpathを使用して、インストールされている合成ツールへのパスを設定します。

ホスト インターフェイス スクリプトの生成

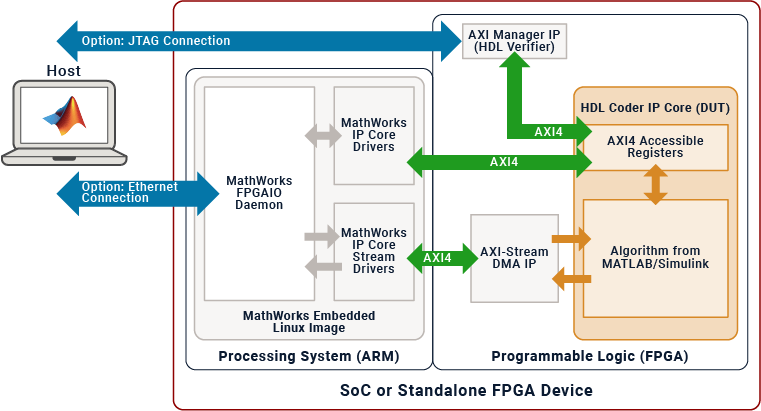

HDL Coder™ を使用して IP コアを生成するときにホスト インターフェイス スクリプトを生成できます。このプロセス中に、ホストとターゲットのインターフェイスを選択する必要があります。これにより、MATLAB がハードウェア ボードと通信する方法が指定されます。ホスト インターフェイス スクリプトのターゲット インターフェイスを指定するには、[HDL コード] タブで [ホスト インターフェイス スクリプト]、[ホスト ターゲット インターフェイス] を選択し、ドロップダウン メニュー オプションから [イーサネット] または [JTAG] のいずれかを選択します。ホストとターゲットのインターフェイスのオプションは次のとおりです。

イーサネット — [イーサネット] オプションを使用するには、ターゲット ボードに組み込みの ARM プロセッサが搭載されている必要があります。

JTAG AXI Manager — 組み込みの ARM プロセッサのないスタンドアロンの FPGA ボードでは、このオプションを使用します。

Simulink® ツールストリップを使用してホスト インターフェイス スクリプトを生成するには、以下のようにします。

Simulink モデルを開き、IP コアを生成するテスト対象設計 (DUT) を選択します。

[HDL Coder] タブを開きます。[アプリ] タブで、[HDL Coder] をクリックします。

JTAG インターフェイスを使用するには、[HDL コード] タブで [設定]、[ターゲット設定] をクリックします。[Insert AXI Manager (HDL Verifier required)] を

JTAGに設定します。ホスト インターフェイス スクリプトを生成するには、[HDL コード] タブで [ホスト インターフェイス スクリプト]、[ホスト インターフェイス スクリプト] をクリックします。IP コアを生成せずにホスト インターフェイス スクリプトを生成できます。生成された IP コアにアクセスするために、ホスト インターフェイス スクリプトが使用するターゲット インターフェイスを構成するには、[ホスト インターフェイス スクリプト] ドロップダウンの矢印を選択し、[ホスト ターゲット インターフェイス] を

[JTAG]または[イーサネット]のいずれかに設定します。JTAG インターフェイスを使用するには、HDL Verifier™ のライセンスが必要です。

HDL ワークフロー アドバイザーを使用してホスト インターフェイス スクリプトを生成するには、以下のようにします。

Simulink モデルを開き、IP コアを生成するテスト対象設計 (DUT) を選択します。

HDL Coder アプリを開きます。

HDL ワークフロー アドバイザーの [タスク 1.1 ターゲット デバイスおよび合成ツールを設定] をクリックし、ターゲット デバイスおよび合成ツールを構成します。

[1.2 ターゲットのリファレンス設計を設定] で [リファレンス設計] プロパティを設定します。[タスク 1.2 ターゲットのリファレンス設計を設定] で JTAG インターフェイスを使用するには、[Insert AXI Manager (HDL Verifier required)] を

[JTAG]に設定します。[1.3 ターゲット インターフェイスを設定] で、DUT の端子を各種インターフェイスにマッピングします。HDL Coder は、ホスト インターフェイス スクリプトの生成時にこれらのインターフェイス設定を使用します。

[4.2. ソフトウェア インターフェイスを生成] をクリックし、[ホスト インターフェイス スクリプトの生成] を選択します。[4.2. ソフトウェア インターフェイスを生成] を右クリックし、[選択したタスクまで実行] を選択します。

ホスト インターフェイス スクリプト ファイル

ホスト インターフェイス スクリプト ファイルを生成する際には、IP コア用に構成したリファレンス設計とターゲット インターフェイス テーブルのマッピングに基づいて、2 つの MATLAB ファイルを作成します。

インターフェイス スクリプト (

gs_<modelName>_interface.m: このスクリプトは、MATLAB から FPGA へのインターフェイスとなるfpgaハードウェア オブジェクトを作成します。インターフェイス スクリプトには、ハードウェアに接続して FPGA をプログラムする MATLAB コマンド、およびハードウェアでのアルゴリズムの実行時にアルゴリズムとデータを交換する方法を示した例が含まれます。インターフェイス セットアップ関数 (

gs_<modelName>_setup.m: この関数は、ハードウェア インターフェイスおよび DUT アルゴリズムからの端子を使用してfpgaオブジェクトを構成します。セットアップ関数には、端子名、方向、データ型、およびインターフェイス マッピング情報をもつ DUT 端子オブジェクトが含まれます。この関数は、これらの DUT 端子を対応するインターフェイスにマッピングします。

インターフェイス スクリプト ファイル

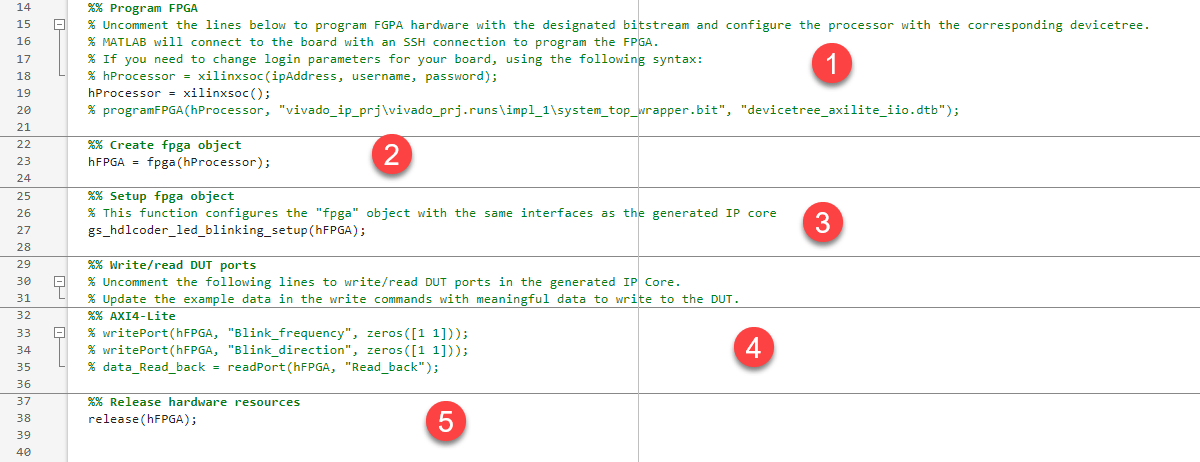

インターフェイス スクリプト ファイルは、データの読み書きのために FPGA ハードウェアへの接続を作成します。このスクリプト ファイルは以下を行います。

ハードウェア ボード上のプロセッサへの接続を表す

intelsocオブジェクトまたはxilinsocオブジェクトを作成します。このスクリプト ファイルには、生成されたビットストリームおよび対応するデバイス ツリーを使用して FPGA をプログラムするprogramFPGAコマンドが含まれています。このセクションは、イーサネット ホスト ターゲット インターフェイスを生成する場合にのみ存在します。ハードウェア ボード上の FPGA への接続を表す

fpgaハードウェア オブジェクトを作成します。目的のハードウェア インターフェイスおよび DUT アルゴリズムからの端子を使用して

fpgaオブジェクトを構成します。DUT 端子との間でデータを読み書きするコマンドが含まれています。これらを使用して、ハードウェア上で動作するアルゴリズムを実行できます。これらのコマンドは、単なる例です。それらを更新してから、スクリプトを実行してアルゴリズムを実行してください。

fpgaオブジェクトで使用されているハードウェア リソースを解放して接続をクリーンアップします。

セットアップ関数ファイル

セットアップ関数ファイルは、生成された IP コアと同じインターフェイスを使用して fpga オブジェクトを構成します。セットアップ スクリプトは再利用可能なファイルです。IP コアに変更を加えた場合は、セットアップ スクリプトを更新するか再生成する必要があります。次のイメージでは、DUT とセットアップ スクリプトの端子およびインターフェイスのマッピング、およびその関係を示しています。

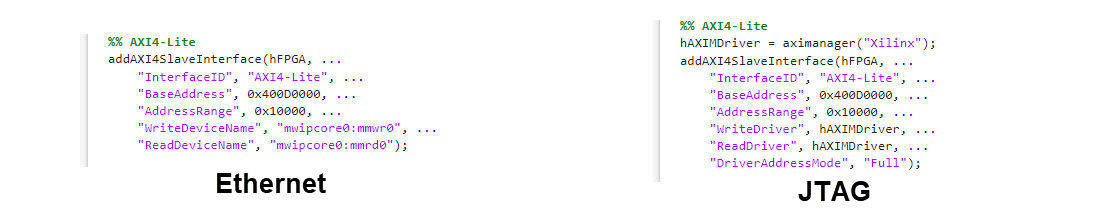

セットアップ関数ファイルは、ターゲット インターフェイスがイーサネットなのか JTAG なのかによって異なります。ターゲット インターフェイスを JTAG に設定すると、HDL Coder は、設計内の AXI レジスタとの通信用の読み取りおよび書き込みドライバーとして aximanager ハードウェア オブジェクトを使用します。次のイメージでは、イーサネット インターフェイスの場合と JTAG インターフェイスの場合のセットアップ関数を比較しています。

ハードウェアでのホスト インターフェイス スクリプトの使用

ラピッド プロトタイピングでは、元の設計を変更する方法に基づいてホスト インターフェイス スクリプトをカスタマイズします。ホスト インターフェイス スクリプトの生成後、以下のようにします。

イーサネットまたは JTAG のいずれかを使用して、ホスト コンピューターをターゲット ハードウェア ボードに接続します。

データ要件に合わせて、インターフェイス スクリプト ファイル内の読み取りコマンドおよび書き込みコマンドを変更します。ターゲット ボードで実行されている展開済みの DUT IP コアまたはアルゴリズムで、変更したスクリプト インターフェイスを使用します。

ホスト インターフェイス スクリプトの各セクションを実行して、ハードウェア ボードに接続し、FPGA をプログラムし、

fpgaオブジェクトを作成して、インターフェイスをセットアップします。インターフェイスは、インターフェイス セットアップ関数ファイルに基づいてセットアップされます。これらのセクションを実行する必要があるのは 1 回だけです。変更した読み取りコマンドおよび書き込みコマンドを実行し、これらのコマンドで反復を継続します。MATLAB コマンド ラインを使用して特定のコマンドを実行できます。

プロトタイピングが完了した後に、ハードウェア ボードへの接続を解放します。

次のイメージでは、ホスト インターフェイス スクリプトを使用する方法、および各手順とインターフェイス スクリプト ファイルの関係を示します。

ホスト インターフェイス スクリプトを反復してテストした後には、以下を行うことができます。

スクリプトをテストまたは検証ワークフローに統合する。

ライブ スクリプトを作成し、対話的に設計のプロトタイプを作成する。例については、Prototype Generated IP Core on Hardware using FPGA I/Oを参照してください。

ホスト インターフェイス スクリプトの管理

ホスト インターフェイス スクリプト ファイルを管理するには、ファイルを更新するか再生成します。既存のパラメーターの変更や軽微なエラーの修正など、軽微な変更を行う場合は、ホスト インターフェイス スクリプト ファイルを更新します。DUT 端子のマッピングの変更、ターゲット ハードウェア デバイスのベンダーの変更、ターゲット ソフトウェア ツールの変更など、大きな変更を行う場合は、ホスト インターフェイス スクリプト ファイルを再生成します。ホスト インターフェイス スクリプト ファイルを再生成すると、HDL Coder では既存のファイルの上書きに関する警告が表示されます。上書きされないようにするために、既存のファイルの名前を変更できます。