生成された HDL IP コアの JTAG AXI Manager を使用したデバッグと制御

この例では、リファレンス設計への HDL Verifier™ AXI Manager IP の自動挿入を指定する方法を示します。この例では、HDL Coder™ で生成された FPGA IP コアを MATLAB® または Simulink® を使用して構成する方法も示します。

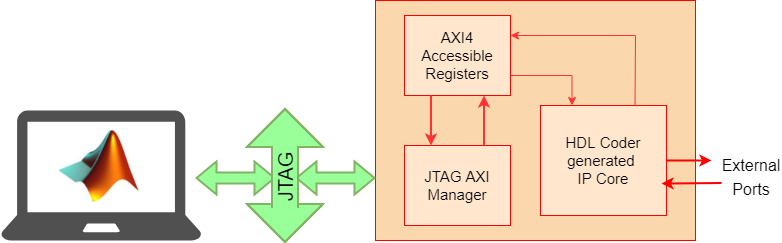

オンボードのメモリ位置にアクセスし、FPGA ロジックの調査や制御を MATLAB または Simulink から迅速に行うには、JTAG AXI Manager IP を使用します。MATLAB では、作成した aximanager System object™ を物理 JTAG ケーブルを介して AXI Manager IP に接続し、MATLAB コマンド ラインから下位メモリの位置に対して読み取りや書き込みのコマンドを実行できます。Simulink では、AXI Manager Read (HDL Verifier) ブロックと AXI Manager Write (HDL Verifier) ブロックで AXI Manager IP を駆動し、HDL Coder で生成されたテスト対象デバイス (DUT) の出力端子と入力端子に対して JTAG インターフェイスから読み取りや書き込みの操作を実行できます。

この例では、ZedBoard™ を使用して FPGA 設計を実装します。

生成された HDL IP コアの JTAG AXI Manager を使用したデバッグと制御

要件

HDL Verifier™ Support Packages for Xilinx FPGA Boards

HDL Coder™ Support Package for AMD® FPGA and SoC Devices

HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアにリストされている、サポートされているバージョンの Xilinx® Vivado™ Design Suite

ZedBoard

AXI Manager IP を含むリファレンス設計の生成

Xilinx Vivado ツール パスを設定します。hdlsetuptoolpath関数を実行するときに独自の Xilinx Vivado インストール パスを使用します。

hdlsetuptoolpath("ToolName","Xilinx Vivado","ToolPath", ... vivadopath);

JTAG AXI Manager の挿入の有効化

1. MATLAB コマンド プロンプトで次のコマンドを実行して hdlcoder_led_blinking モデルを開きます。

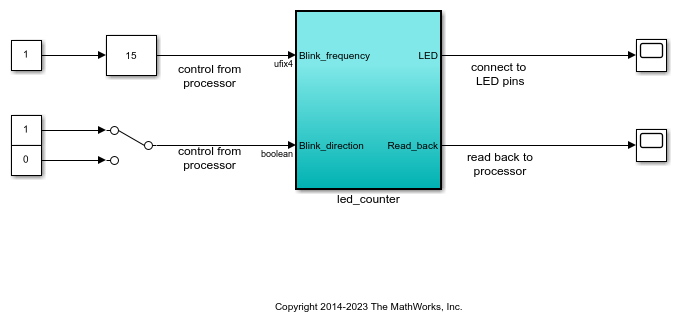

open_system("hdlcoder_led_blinking")

この例では、led_counter サブシステムをハードウェアに実装します。このサブシステムは、ハードウェア上の LED を点滅させるカウンターをモデル化したものです。2 つの入力端子 Blink_frequency および Blink_direction は LED の点滅頻度および方向をそれぞれ決定する制御端子です。出力端子 LED はハードウェア上の LED に接続します。出力端子 Read_back を使用してデータを MATLAB に読み戻すことができます。

2. HDL ワークフロー アドバイザーを開きます。hdlcoder_led_blinking/led_counter サブシステムを選択します。[アプリ] タブで、[HDL Coder] をクリックします。[HDL コード] タブの [アシスタンス] セクションで、[ワークフロー アドバイザー] をクリックします。

3. [ターゲットを設定]、[ターゲット デバイスおよび合成ツールを設定] タスクで、[ターゲット ワークフロー] を IP Core Generation に設定します。

4. [ターゲット プラットフォーム] を ZedBoard に設定します。このオプションが表示されない場合は、[さらに取得] を選択してサポート パッケージ インストーラーを開きます。サポート パッケージ インストーラーで、Xilinx Zynq Platform を選択し、サポート パッケージ インストーラーの手順に従ってインストールを完了します。

5. [このタスクを実行] をクリックして [ターゲット デバイスおよび合成ツールを設定] タスクを実行します。

6. [ターゲットを設定]、[ターゲットのリファレンス設計を設定] タスクで、[Default system] を選択し、[Insert JTAG AXI Manager (HDL Verifier required)] リファレンス設計パラメーターを JTAG に設定します。

7. [このタスクを実行] をクリックして [ターゲットのリファレンス設計を設定] タスクを実行します。

HDL IP コアの生成と AXI Manager IP を含むプロジェクトの作成

DUT 内の各端子を IP コアのターゲット インターフェイスのいずれかにマッピングします。この例では、入力端子 "Blink_frequency" と "Blink_direction" を AXI4-Lite インターフェイスにマッピングするため、それらの端子の AXI インターフェイスを介してアクセスできるレジスタが HDL Coder で生成されます。出力端子 "LED" については、この例では、ZedBoard の LED ハードウェアに接続する外部インターフェイス LEDs General Purpose [0:7] にマッピングします。

1. [ターゲットを設定]、[ターゲット インターフェイスを設定] タスクで、"Blink_frequency"、"Blink_direction"、および "Read_back" に対して AXI4-Lite を選択します。

2. "LED" に対して LEDs General Purpose [0:7] を選択します。

3. JTAG AXI Manager を含むリファレンス設計プロジェクトを作成します。

プロジェクトを作成するには、[プロジェクトを作成] タスクを右クリックし、[選択したタスクまで実行] を選択します。

Vivado プロジェクトで、JTAG AXI Manager IP がリファレンス設計に挿入されていることを確認できます。[ターゲット周波数を設定] タスクのターゲット周波数が 100 MHz 以下の場合、このリファレンス設計を使用して、DUT のクロックで JTAG AXI Manager IP が駆動されます。

[ターゲット周波数を設定] タスクのターゲット周波数が 100 MHz を超える場合は、このリファレンス設計を使用して、タイミングの問題を回避するために clk_wiz_IO によって生成される 50 MHz の固定クロックで JTAG AXI Manager IP が駆動されます。

ホスト インターフェイス モデルの生成

DUT を Simulink モデルのAXI Manager Read (HDL Verifier)ブロックとAXI Manager Write (HDL Verifier)ブロックに置き換えて、ホスト インターフェイス モデルを生成します。次の手順に従ってホスト インターフェイス モデルを生成します。

1. [組み込みシステムの統合]、[ソフトウェア インターフェイスを生成] タスクで、[ホスト ターゲット インターフェイス] を JTAG AXI Manager (HDL Verifier) に設定します。

2. [ホスト インターフェイス モデルの生成] を選択します。

3. [このタスクを実行] をクリックします。

次のスクリーン ショットは、gm_hdlcoder_led_blinking_Hostinterface.slx ホスト インターフェイス モデルを示しています。このホスト インターフェイス モデルを Simulink テスト ベンチとして使用して DUT のレジスタを調整できます。

ワークフローの残りの手順を実行して、ビットストリームを生成し、ターゲット デバイスをプログラムします。

JTAG AXI Manager を使用した HDL Coder IP コアの制御

HDL Coder IP コアを制御する Simulink モデル

1. gm_hdlcoder_led_blinking_Hostinterface モデルを開きます。

2. gm_hdlcoder_led_blinking_Hostinterface、led_counter、AXI4SlaveWrite サブシステムに移動します。AXI Manager Write (HDL Verifier)ブロックを構成します。

次の図は、現在の HDL ワークフロー アドバイザーの構成に対応する AXI Manager Write ブロックの既定の構成を示しています。

3. gm_hdlcoder_led_blinking_Hostinterface、led_counter、AXI4SlaveRead サブシステムに移動します。AXI Manager Read (HDL Verifier)ブロックを構成します。

次の図は、現在の HDL ワークフロー アドバイザーの構成に対応する AXI Manager Read ブロックの既定の構成を示しています。

gm_hdlcoder_led_blinking_Hostinterface モデルを実行して、Simulink から読み取りと書き込みの処理を実行します。

次の図は、"Read_back" レジスタ (LED の出力) の時間経過に伴うサンプル数を示しています。

MATLAB コマンド ライン インターフェイス

AXI Manager IP のオブジェクトを作成して、MATLAB コマンド ラインから DUT を制御することもできます。

1. AXI Manager オブジェクトを作成します。

h = aximanager("Xilinx")

2. LED の点滅頻度を変更します。

h.writememory("400D0100",0)

LED の点滅頻度が低くなったことを確認します。LED の点滅頻度を 0 から 15 に変更して頻度を上げます。

h.writememory("400D0100",15)

3. 現在のカウンター値を読み取ります。

h.readmemory("400D0108",1)

4. 完了したらオブジェクトを削除して JTAG リソースを解放します。オブジェクトを削除しないと、他の JTAG の操作が失敗します。

delete(h)

カスタム リファレンス設計の JTAG AXI Manager

[Insert AXI Manager (HDL Verifier required)] リファレンス設計パラメーターは、カスタム リファレンス設計に既定で追加されます。パラメーターの既定値は off です。カスタム リファレンス設計で、次のプロパティを使用してこのパラメーターを制御できます。

AddMATLABAXIManagerParameter - Insert AXI Manager パラメーターの可視性を制御する。

MATLABAXIManagerDefaultValue - AXI Manager IP を挿入するかどうかを指定する。

次の図に示すように、カスタム リファレンス設計ワークフローの "plugin_rd.m" ファイルでプロパティを追加して、[Insert AXI Manager (HDL Verifier required)] パラメーターを [ターゲットのリファレンス設計を設定] タスクで表示するように設定し、既定値として JTAG を割り当てることができます。