FPGA Data Capture を使用した IP コアのデバッグ

この例では、HDL Coder™ で生成する IP コアを FPGA Data Capture のみを使用してデバッグする方法と AXI Manager および FPGA Data Capture の両方を一緒に使用してデバッグする方法を示します。この例では、FPGA Data Capture を使用して大量のデータを外部メモリに取得する方法も示します。

要件

AMD® Zynq® UltraScale+™ MPSoC ZCU102 評価キット。ZCU102 ハードウェアの設定の詳細については、Simulink モデルからの IP コアの生成入門を参照してください。

HDL Coder Support Package for AMD FPGA and SoC Devices

HDL Verifier™ Support Package for AMD FPGA and SoC Devices

HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアにリストされているサポート対象バージョンの AMD Vivado® Design Suite

はじめに

実際のハードウェアでの設計の実行中に IP コアの内部信号を監視すると、設計のデバッグと解析が行えるため便利です。この例では、生成された IP コアの内部信号を MATLAB® で FPGA Data Capture を使用して取得する方法を示します。

この例では、ブロッキング モードとノンブロッキング モードの FPGA Data Capture の使用方法を示します。取得モードの詳細については、CaptureMode (HDL Verifier)を参照してください。ノンブロッキング モードでは、AXI Manager と FPGA Data Capture を JTAG インターフェイスから同時に使用できます。ブロッキング モードでは MATLAB の実行が一時停止するため、このモードの使用時は他のアプリケーションは使用できません。一方、ノンブロッキング モードでは、FPGA Data Capture でハードウェアからデータを取得しながら、AXI Manager を使用して IP コアを構成できます。

この例では、大量のデータを外部メモリに取得するための FPGA Data Capture の使用方法も示します。取得データを格納するメモリ タイプを内部メモリまたは外部メモリのいずれかとして構成できます。内部メモリは内部 BRAM リソースを使用して取得データを格納し、外部メモリは FPGA に接続された外部 DDR メモリを使用して格納します。ターゲット ボードで利用できる外部 DDR メモリのサイズに応じて、大量のサンプルを取得することができます。FPGA Data Capture では、AMD デバイスでのみ、JTAG、PS イーサネット、または USB イーサネットの接続を介した外部メモリがサポートされます。

モデルを開きます。

open_system('hdlcoder_led_blinking_data_capture');

この例では、led_counter サブシステムをハードウェアに実装します。このサブシステムは、ハードウェア上の LED を点滅させるカウンターをモデル化したものです。2 つの入力端子 Blink_frequency および Blink_direction は LED の点滅頻度および方向をそれぞれ決定する制御端子です。出力端子 LED はハードウェア上の LED に接続します。出力端子 Read_back を使用してデータを MATLAB に読み戻すことができます。

led_counter サブシステムに、テスト ポイントとなる内部信号がいくつかあります。それらの内部信号を FPGA Data Capture の HDL IP に接続できるように、それらの信号の DUT から IP コアまでの経路が HDL Coder で指定されます。

open_system('hdlcoder_led_blinking_data_capture/led_counter');

この例では、Default system リファレンス設計を使用して、データを JTAG 接続で内部メモリに取得します。さらに、Default system with data capture with external DDR4 memory access リファレンス設計を使用して、大量のデータを PS イーサネット接続で外部メモリに取得します。

次の図は、Default system with data capture with external DDR4 memory access リファレンス設計のアーキテクチャを大まかなブロック線図で示したものです。

このアーキテクチャで、HDL DUT IP は IP コアの生成ワークフローから生成された IP コアに対応します。HDL ワークフロー アドバイザーの IP コアの生成ワークフローにおいて、HDL Verifier から提供される JTAG AXI Manager ブロックと FPGA Data Capture IP ブロックがリファレンス設計に追加されます。アーキテクチャのその他のブロックは、事前定義されたリファレンス設計を表しています。ボード上で FPGA 設計を実行した後、JTAG AXI Manager IP を使用して HDL DUT IP を構成します。FPGA Data Capture IP は、HDL DUT IP の内部信号を AXI4 Master インターフェイス経由で外部メモリに取得した後、それらを MATLAB に読み戻します。

hdlcoder.ReferenceDesign クラスの addFPGADataCaptureInterface メソッドを使用して、FPGA Data Capture IP コアを AXI4 Master インターフェイスとともに独自のカスタム リファレンス設計に統合できます。

HDL IP コアの生成

モデルから HDL ワークフロー アドバイザーを起動し、IP コアの生成ワークフローを実行します。詳しい手順については、Simulink モデルからの IP コアの生成入門を参照してください。

1. 手順 1.1 で、[ターゲット ワークフロー] を IP Core Generation、[ターゲット プラットフォーム] を Xilinx Zynq UltraScale+ MPSoC ZCU102 Evaluation Kit に設定します。[このタスクを実行] をクリックします。

2. 手順 1.2 で、データを内部 BRAM メモリに取得するには、[リファレンス設計] を Default system に設定します。[Insert AXI Manager (HDL Verifier required)] と [FPGA Data Capture (HDL Verifier required)] を JTAG に設定します。[このタスクを実行] をクリックします。

大量のデータを外部 DDR メモリに取得するには、[リファレンス設計] を Default system with data capture with external DDR4 memory access に設定します。[Insert AXI Manager (HDL Verifier required)] を JTAG、[FPGA Data Capture (HDL Verifier required)] を PS Ethernet に設定します。[このタスクを実行] をクリックします。

3. 手順 1.3 で、[テスト ポイントの HDL DUT 出力端子の生成を有効にする] を選択します。

4. 手順 1.3 で、[blinkfrequency]、[blinkdirection]、[led_output]、および [count] の各端子のインターフェイスを FPGA Data Capture に設定します。[このタスクを実行] をクリックします。

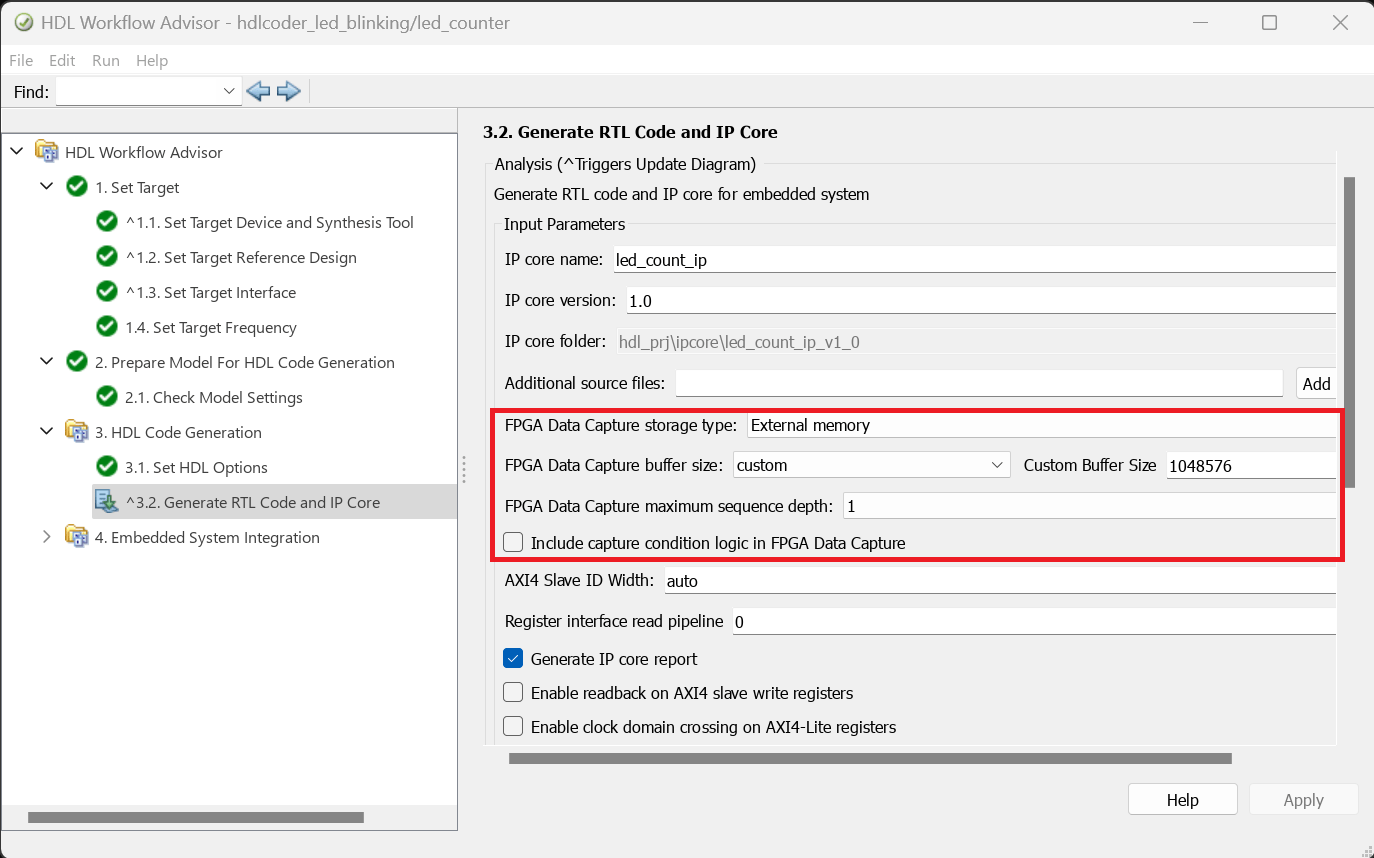

5. ワークフローの残りの手順を手順 3.1 まで進めます。手順 3.2 で、FPGA Data Capture IP のパラメーターを構成できます。[FPGA Data Capture のストレージ タイプ]、[FPGA Data Capture のバッファー サイズ]、[FPGA Data Capture のシーケンスの最大深度]、および [FPGA Data Capture に取得条件ロジックを含める] です。

デバッグ データを内部 BRAM メモリに取得するには、これらのパラメーターの既定値を使用します。

データを外部 DDR メモリに取得するには、[FPGA Data Capture のストレージ タイプ] を External memory、[FPGA Data Capture のバッファー サイズ] を 1048576 に設定します。[このタスクを実行] をクリックします。

6. ワークフローの残りの手順を進め、HDL IP を生成し、ターゲット デバイスをプログラムします。

IP コアからのデータの取得と表示

次に、Zynq UltraScale+ MPSoC ボードからデータを取得します。

FPGA Data Capture の起動スクリプトを見つけます。この例では、HDL コード生成ディレクトリにある hdl_prj/ip_core/led_count_ip_v1_0/fpga_data_capture/launchDataCaptureApp.m というスクリプトです。このスクリプトの場所はコード生成レポートでも確認できます。

MATLAB で launchDataCaptureApp スクリプトを実行します。スクリプトのディレクトリを MATLAB パスに追加するか、現在の作業フォルダーを変更します。

ブロッキング モードでのデータの取得

スクリプトを実行して "FPGA Data Capture" ツールを起動します。既定では、FPGA Data Capture はブロッキング モードで動作します。トリガー条件を設定せずに FPGA からデータを取得するには、[Capture Data] をクリックします。

あるいは、トリガー条件を使用してデータを取得できます。たとえば、トリガー条件を led_counter == 0 と設定し、トリガー位置を 32 に設定します。その後、[Capture Data] をもう一度クリックします。

ノンブロッキング モードでのデータの取得

スクリプトを実行して "FPGA Data Capture" ツールを起動し、ワークスペースで fpgadc_obj オブジェクトを作成します。MATLAB コマンド プロンプトで次のコマンドを実行して、取得モードをノンブロッキングに変更します。

fpgadc_obj.CaptureMode = 'nonblocking';

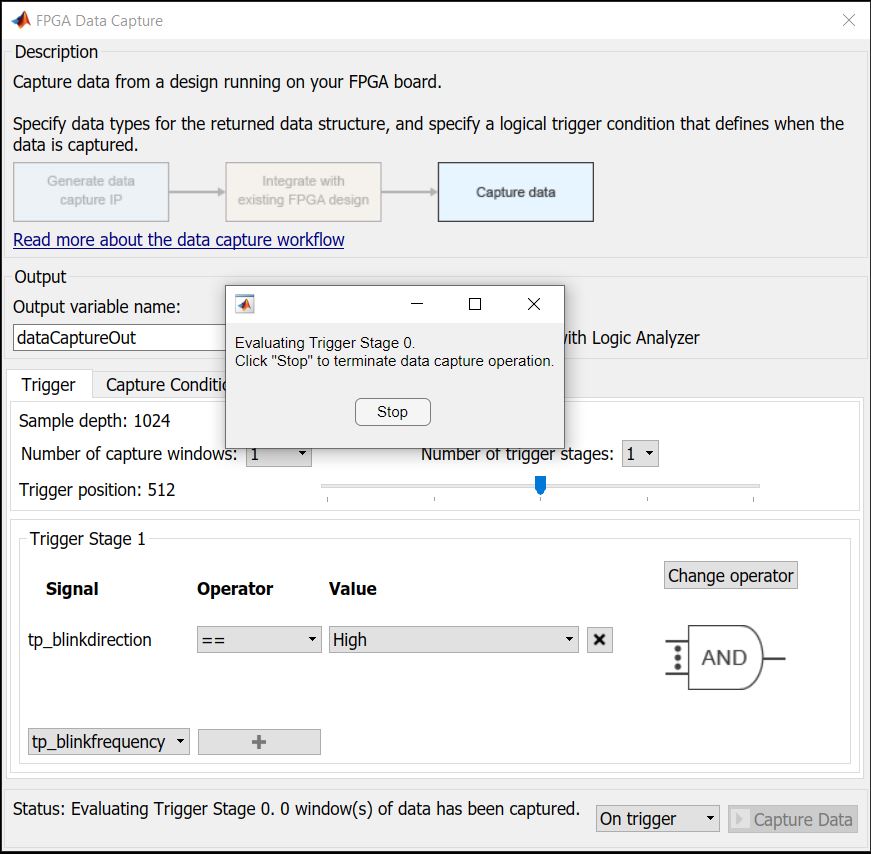

ノンブロッキング モードの FPGA Data Capture では、FPGA Data Capture と AXI Manager を同時に使用できます。詳細については、FPGAデータキャプチャとAXIマネージャの同時使用 (HDL Verifier)を参照してください。今度は、トリガー条件を tp_blinkdirection == 1 と設定し、トリガー位置を 64 に設定します。その後、[Capture Data] をクリックします。

FPGA Data Capture はトリガー条件まで待機します。FPGA Data Capture がノンブロッキング モードであるため、AXI Manager で読み取りと書き込みの処理を実行できます。

次に、FPGA Data Capture で [tp_blinkdirection] を High に設定します。その後、MATLAB で AXI Manager オブジェクトを作成します。

axi_manager_obj = aximanager('AMD');

axi_manager_obj.writememory('0x40010104',1);

FPGA Data Capture により、[ロジック アナライザー] にデータが取得されます。次の図は点滅方向の変化を示しています。

外部 DDR メモリへの大規模データの取得

この例では、大量のデータを PS イーサネット インターフェイス経由で取得します。スクリプトを実行して FPGA Data Capture ツールを起動し、ワークスペースで fpgadc_obj オブジェクトを作成します。

DeviceAddress プロパティを使用して、ハードウェア ボードのイーサネット ポートのインターネット プロトコル (IP) アドレスを指定します。

fpgadc_obj.DeviceAddress = '10.10.10.15'

データ取得 HDL IP コアのベース アドレス (CaptureBaseAddress) と外部 DDR メモリのベース アドレス (MemoryBaseAddress) を確認します。これらは、plugin_rd リファレンス設計定義ファイルのアドレスと一致していなければなりません。

トリガー条件を設定せずに FPGA からデータを取得するには、[Capture Data] をクリックします。

あるいは、トリガー条件を使用してデータを取得できます。たとえば、トリガー条件を led_counter == 0 と設定します。その後、MATLAB で AXI Manager オブジェクトを作成します。

axi_manager_obj = aximanager('AMD');

axi_manager_obj.writememory('0x40000100',uint32(15));

その後、FPGA Data Capture アプリで [データの取得] をクリックします。

メモ: [トリガー位置] パラメーターと [取得ウィンドウの数] パラメーターは、外部メモリ ストレージ タイプに対しては無効になります。

参考

トピック

- データキャプチャワークフロー (HDL Verifier)

- FPGA データ キャプチャを使用して Xilinx FPGA ボードから温度センサー データをキャプチャする (HDL Verifier)