HDL IP コアを調査して迅速にプロトタイプを作成するためのソフトウェア インターフェイス モデルの生成

SoC プラットフォーム向けのハードウェア ソフトウェア協調設計ワークフローを実行する場合、DUT アルゴリズムの HDL IP コアを生成してから、IP コアを参照設計に統合します。SoC プラットフォーム向けのハードウェア ソフトウェア協調設計ワークフローを参照してください。

HDL IP コアをターゲット ハードウェアでテストするには、ソフトウェア インターフェイス モデルを生成します。ソフトウェア インターフェイス モデルは AXI ドライバー ブロックを使用して、HDL IP コアの機能をエクスターナル モード シミュレーションでテストします。

前提条件

ZedBoard などの、ソフトウェア インターフェイス モデルを展開するターゲット プラットフォーム。

Xilinx® Vivado® などのサードパーティ製合成ツールの最新バージョン。HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアを参照してください。MATLAB® セッションでは、関数

hdlsetuptoolpathを使用して、そのインストールされた合成ツールへのパスを設定します。ソフトウェア インターフェイス モデルを生成している場合、Embedded Coder® および Simulink® Coder™ をインストールします。

ターゲット プラットフォームの HDL Coder™ サポート パッケージと Embedded Coder サポート パッケージをインストールします。MATLAB ツールストリップで、[ホーム] 、 [アドオン] 、 [アドオンの入手] ボタンをクリックします。アドオンの取得と管理を参照してください。

ソフトウェア インターフェイスの生成

IP コアの生成ワークフローを実行する場合、ホスト インターフェイス スクリプトとソフトウェア インターフェイス モデルを HDL ワークフロー アドバイザーの UI またはコマンド ラインで生成できます。

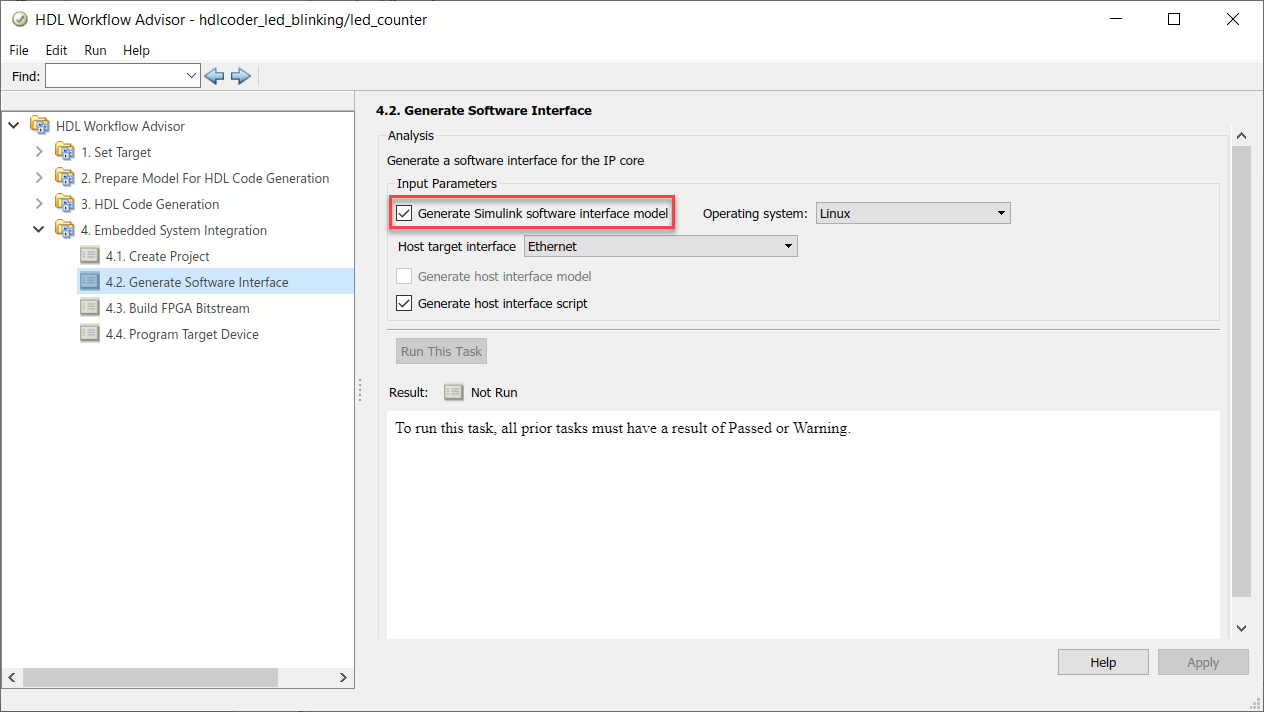

UI の [組み込みシステムの統合] 、 [ソフトウェア インターフェイスを生成] タスクから、[Simulink ソフトウェア インターフェイス モデルを生成] チェック ボックスをオンにします。

スタンドアロン FPGA ボードをターゲットにしている場合、ソフトウェア インターフェイス モデルを生成できません。代わりに、AXI Manager ドライバーを使用して、ホスト インターフェイス スクリプトを生成して IP コアをテストできます。

[ターゲットのリファレンス設計を設定] タスクで、[Insert AXI Manager (HDL Verifier required)] をホスト マシンと FPGA ボードの間の通信を行うインターフェイスに基づいて、

[JTAG]または[Ethernet]に設定します。[Ethernet] の場合、[ボード IP アドレス] パラメーターを使用して FPGA ボードの IP アドレスを指定します。メモ

既定では、

[Ethernet]オプションは Artix®-7 35T Arty ボード、Kintex®-7 KC705 ボード、および Virtex®-7 VC707 ボードでのみ使用できます。このオプションをイーサネット物理レイヤー (PHY) を備えた他の Xilinx ボードで有効にするには、HDL ワークフロー アドバイザーツールを起動する前に、addEthernetMACInterfaceメソッドを使用してplugin_boardファイルに手動でイーサネット メディア アクセス コントローラー (MAC) ハブ IP を追加します。[ソフトウェア インターフェイスを生成] タスクに対してワークフローを実行します。

[ソフトウェア インターフェイスを生成] タスクで、[ホスト インターフェイス スクリプトの生成] チェック ボックスをオンにしてこのタスクを実行します。

コマンド ラインで、HDL ワークフロー アドバイザーの設定をスクリプトにエクスポートしてから、これらのプロパティをワークフロー構成オブジェクトと共に使用します。このスクリプトは、モデルとスクリプトを生成することで、ソフトウェア インターフェイス タスクの実行を指定します。RunTaskGenerateSoftwareInterface を false に設定してこのタスクをスキップする場合、モデルとスクリプトは生成されません。Configure and Run IP Core Generation Workflow with a Scriptを参照してください。

% Export Workflow Configuration Script % ... %% Load the Model load_system('hdlcoder_led_blinking'); %% Model HDL Parameters % Set Model HDL parameters % ... hdlset_param('hdlcoder_led_blinking', 'SynthesisTool', 'Xilinx Vivado'); hdlset_param('hdlcoder_led_blinking', 'Workflow', 'IP Core Generation'); % ... % Set Workflow tasks to run hWC.RunTaskGenerateSoftwareInterface = true; hWC.GenerateSoftwareInterfaceModel = true; hWC.GenerateHostInterfaceScript = true; % ... %% Run the workflow hdlcoder.runWorkflow('hdlcoder_led_blinking/led_counter', hWC);

ソフトウェア インターフェイス モデル

SoC プラットフォームのワークフローを実行する場合は、HDL IP コア機能をテストするためにソフトウェア インターフェイス モデルが生成されます。Embedded Coder と Simulink Coder がインストールされている場合、モデルから組み込みコードを生成し、ARM® プロセッサで実行可能ファイルをビルドして実行できます。スタンドアロン FPGA ボードをターゲットにする場合、ボードに組み込み ARM プロセッサがないため、ソフトウェア インスタンス モデルを生成できません。代わりに、AXI Manager を使用して、ホスト インターフェイス スクリプトを生成して IP コアをテストします。

生成されたソフトウェア インターフェイス モデルは、ターゲット プラットフォーム インターフェイス テーブルとリファレンス設計の設定に基づいて、元のモデルの DUT アルゴリズムを AXI ドライバー ブロックに置き換えます。HDL IP コア機能をテストするには、モデルをエクスターナル モードでシミュレートして、ターゲット ハードウェア上で実行します。モデルでは、既定で同時実行が有効になっています。これは、SoC プラットフォーム搭載のプロセッサによって複数のタスクが同時に実行されることを意味します。

ソフトウェア インターフェイス モデルには、接頭辞が gm_ で接尾辞が _interface の元のモデルと同じ名前が設定されます。HDL コード生成から生成されたモデルの接頭辞は gm_ です。このモデルをソフトウェア インターフェイス モデルとして使用していることを示すには、接頭辞を sm_ に変更します。

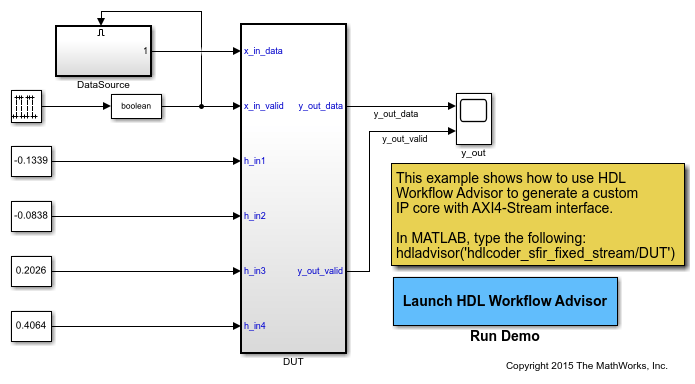

モデル hdlcoder_sfir_fixed_stream を開きます。このモデルは、Valid 信号を入力制御端子として挿入することで、sfir_fixed モデルを簡易 AXI4-Stream プロトコルにマッピングします。

openExample('hdlcoder_sfir_fixed_stream')

DUT サブシステムの HDL ワークフロー アドバイザーを開きます。[ターゲット デバイスおよび合成ツールを設定] タスクで、

[IP Core Generation]を [ターゲット ワークフロー] として指定し、[ZedBoard] を [ターゲット プラットフォーム] として指定します。[このタスクを実行] をクリックします。[ターゲットのリファレンス設計を設定] タスクで、[Default system with AXI4-Stream interface] を [ターゲットのリファレンス設計を設定] として指定します。[このタスクを実行] をクリックします。

[ターゲット インターフェイスを設定] タスクの [ターゲット プラットフォーム インターフェイス テーブル] で、DUT 端子をターゲット インターフェイスにマッピングします。[このタスクを実行] をクリックします。

[ソフトウェア インターフェイスを生成] タスクを右クリックして [選択したタスクまで実行] を選択します。ワークフローを実行して、ソフトウェア インターフェイス モデルを生成します。

生成されたソフトウェア インターフェイス モデルの名前は gm_hdlcoder_sfir_fixed_stream_interface.slx です。元のモデルはデータ端子 x_in_data と y_out_data のスカラー端子を使用するため、[ソフトウェア インターフェイスを生成] タスクにより、AXI4-Stream IIO ドライバー ブロックがソフトウェア インターフェイス モデルで自動的に生成されないという警告が表示されます。Simulink ライブラリ ブラウザーで、ターゲット プラットフォームの Embedded Coder サポート パッケージ ライブラリからドライバー ブロックを挿入するか、データ端子をベクトル信号にマッピングしてワークフローを再実行します。これに挿入されている AXI4-Stream IIO ドライバー ブロックをもつソフトウェア インターフェイス モデルを確認するには、hdlcoder_sfir_fixed_stream_sw を開きます。モデルは、データ端子の AXI4-Stream IIO Write (Embedded Coder) ブロックと AXI4-Stream IIO Read (Embedded Coder) ブロックを使用します。フィルター端子は AXI4-Lite ドライバー ブロックにマッピングされます。

メモ

DUT で AXI4 インターフェイスに半精度および単精度のデータ型を使用する場合は、生成されたソフトウェア インターフェイス モデル内の Data Type Conversion ブロックを Float Typecast ブロックに置き換える必要があります。

openExample('hdlcoder_sfir_fixed_stream_sw')

停止時間が inf のモデルを構成します。[ハードウェア] タブで、モデルに指定されているハードウェア設定を確認します。次にターゲット プラットフォームに接続し、アプリケーションをビルドして実行し、HDL IP コア機能を検証します。AXI-Stream インターフェイスを使用した IP コアの生成を参照してください。