このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

リファレンス設計の合成を高速化するための IP キャッシュ

[IP Core Generation] ワークフローを Xilinx® Vivado® でサポートするターゲット プラットフォームでは、IP キャッシュを使用できます。IP キャッシュは多数の IP モジュールを含むか、合成実行時間が長時間の IP モジュールを含むリファレンス設計の合成時間を短縮します。IP キャッシュを有効にすると、Vivado プロジェクトで Out-Of-Context (OOC) ワークフローが使用されます。このワークフローは最上位の設計のコンテキストからリファレンス設計で IP を合成します。OOC ワークフローは、合成ツールが IP キャッシュを再利用し、ワークフローの実行時に IP を再合成する必要がないため、プロジェクトの実行を高速化します。

IP キャッシュを有効にしない場合、既定の設定で Vivado プロジェクトはグローバル合成フローを使用します。このフローは最上位の設計と共にリファレンス設計で IP モジュールを合成します。後続のプロジェクト実行において、このワークフローはリファレンス設計で IP モジュールを再合成します。

IP キャッシュを使用する場合の要件

ターゲット ワークフロー:

IP コアの生成Xilinx Vivado を使用する Speedgoat ボードの

Simulink Real-Time FPGA I/O

合成ツール: Xilinx Vivado

IP キャッシュとは

IP キャッシュとは、リファレンス設計の IP モジュールに対応するサブフォルダーで構成されるフォルダーのことです。各サブフォルダーはファイル名に対応するハッシュ インデックスで整理されます。各 IP モジュールのサブフォルダーは、Xilinx Core Instance (XCI) ファイル、Design Checkpoint (DCP) ファイル、合成ログ ファイルで構成されます。DCP とは、合成されたネットリスト、ブラック ボックス HDL のスタブ ファイル、出力クロック制約が含まれるコンテナー ファイルのことです。

ワークフローの実行時に IP キャッシュを再利用するには、IP 合成が IP キャッシュのハッシュ インデックスと一致しなければなりません。一致したハッシュ インデックスは IP キャッシュのヒットに対応します。後続の実行で IP キャッシュにヒットするには、以下について同じものを使用します。

部分、言語、ターゲット プラットフォーム設定

リファレンス設計のバージョン

ターゲット周波数

IP キャッシュ作成時の

hdl_prjフォルダー

IP キャッシュの動作

IP キャッシュを有効にすると、Xilinx Vivado プロジェクトで Out-Of-Context (OOC) ワークフローが使用されます。OOC 設計フローは、次を行うボトムアップ ワークフローです。

最上位の設計とは別にリファレンス設計で IP モジュールを合成します。合成出力は Design Checkpoint (DCP) ファイルです。

最上位の設計を合成するときに、リファレンス設計で DCP で提供された HDL スタブ ファイルを使用して IP をブラック ボックスとして処理します。

IP 設計チェックポイント ファイルのネットリストを最上位のネットリストにリンクし、ターゲット デバイスに設計を実装します。

設計を変更してワークフローを実行する際に IP を再合成する必要がないため、大規模なリファレンス設計では OOC フローによって合成実行時間が短縮されます。OOC ワークフローと IP 合成オプションの詳細については、Xilinx のドキュメンテーションを参照してください。

IP キャッシュの有効化

IP キャッシュを有効にする前に、ターゲット ワークフローとして [IP Core Generation] を指定してから、ターゲット プラットフォーム設定を指定します。IP キャッシュを有効にするには、次を行います。

HDL ワークフロー アドバイザーの [プロジェクトを作成] タスクで、[IP キャッシュの有効化] チェック ボックスをオンにします。

コマンド ラインで

hdlcoder.WorkflowConfigクラスのEnableIPCachingプロパティを使用します。このプロパティを使用するには、hdlcoder.WorkflowConfigクラスのオブジェクトを作成するか、HDL ワークフロー アドバイザー設定をスクリプトにエクスポートします。hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx Vivado','TargetWorkflow','IP Core Generation'); % ... % ... hWC.EnableIPCaching = true;

HDL Coder リファレンス設計の IP キャッシュ

合成時間が長い大規模なリファレンス設計では IP キャッシュを使用します。たとえば、HDL Coder™ リファレンス設計 Default video system (requires HDMI FMC module) は IP キャッシュを使用する有力候補です。

メモ

Simulink Real-Time FPGA I/O ワークフローで使用する Speedgoat IO333-325K ボードには IP キャッシュが付属しています。ワークフローの初回実行時にコード ジェネレーターはこの IP キャッシュを再利用するため、リファレンス設計の合成時間が短縮されます。

IP キャッシュを有効にするには、HDL ワークフロー アドバイザーで [IP Core Generation] をターゲット ワークフローとして指定してから、ターゲット プラットフォーム設定を指定します。ワークフローをはじめて実行する前に、次を行います。

[プロジェクトを作成] タスクで、[IP キャッシュの有効化] チェック ボックスをオンにします。

このタスクを実行すると、ワークフローによって空の IP キャッシュ フォルダーが作成されます。

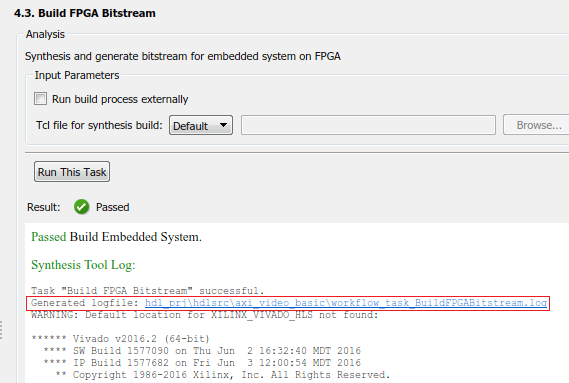

ipcacheフォルダーはhdl_prj/vivado_ip_prjパスで確認できます。[FPGA ビットストリームのビルド] タスクを実行します。

このタスクにより、合成ログと HDL IP コアに生成された設計チェックポイント ファイルやリファレンス設計のその他の IP ブロックが IP キャッシュ フォルダーに取り込まれます。このタスクが正常に実行されると、生成されたファイルを

ipcacheフォルダーで確認できます。

IP Core Generation ワークフローを 2 度目に実行すると、[FPGA ビットストリームのビルド] タスクでタスクの実行時間が短縮されたことを確認できます。ワークフローの初回実行時と同じ IP 設定と hdl_prj フォルダーを必ず使用してください。このタスクが正常に実行された際にワークフローが IP キャッシュを再利用したかどうかを確認するには、workflow_task_buildFPGABitstream.log ファイルを開きます。

このコードの抜粋には、Vivado プロジェクトがジョブの最大数を起動して設計を合成し、IP キャッシュ フォルダー内の IP モジュールを再利用したことが示されます。IP モジュールの cacheID が ipcache フォルダー内のサブフォルダーのファイル名と一致することを確認できます。

... # reset_run impl_1 # reset_run synth_1 # launch_runs -jobs 4 synth_1 ... ... ... INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_RGBtoYCbCr_0_0, cacheID = 3575924730488800 INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_YCbCrtoRGB_0_0, cacheID = e71459f41e26e141 INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_xbar_0, cacheID = d0f0971cb77bcaed INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_axis2hdmi_0_0, cacheID = 7601a322f9fd0ec4 ...

カスタム リファレンス設計の IP キャッシュ

独自のカスタム リファレンス設計を使用する場合、はじめてワークフローを実行するときに IP キャッシュでリファレンス設計の合成を高速化できます。IP キャッシュを再利用するには、IP キャッシュの zip ファイルを作成してから、リファレンス設計定義ファイルがこの zip ファイルを指していることを確認します。

IP キャッシュの zip ファイルを作成するには、次を行います。

DUT サブシステムをもつ任意の Simulink® モデルに対して HDL ワークフロー アドバイザーを開き、[RTL コードと IP コアの生成] タスクに対する [IP Core Generation] ワークフローを実行します。

[プロジェクトを作成] タスクで、[IP キャッシュの有効化] チェック ボックスをオンにしてから、[このタスクを実行] をクリックします。このタスクにより空の IP キャッシュ フォルダーが作成されます。

[FPGA ビットストリームのビルド] タスクに対するワークフローを実行します。このタスクにより HDL IP コアとリファレンス設計の IP モジュールが IP キャッシュに取り込まれます。

IP キャッシュ フォルダーで、DUT に生成された IP コア ファイルを削除します。このフォルダーの残りのファイルを 1 つの zip ファイルにして、

ipcache.zipと名前を付けてから、リファレンス設計フォルダーにファイルを保存します。

IP キャッシュを再利用するには、リファレンス設計の定義ファイル plugin_rd.m で hdlcoder.ReferenceDesign クラスの IPCacheZipFile プロパティを使用します。そのプロパティを使用し、ipcache.zip ファイルを Xilinx Vivado プロジェクトに追加します。

function hRD = plugin_rd() % Reference design definition hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); % ... % ... hRD.IPCacheZipFile = 'ipcache.zip';

参考

hdlcoder.Board | hdlcoder.ReferenceDesign