リファレンス設計のパラメーターに基づいたリファレンス設計の動的なカスタマイズ

独自のカスタム リファレンス設計を定義する場合、hdlcoder.ReferenceDesign クラスの CustomizeReferenceDesignFcn メソッドを使用してリファレンス設計を動的にカスタマイズできます。

リファレンス設計をカスタマイズする理由

インターフェイスの選択、データ幅、または I/O プラグインが異なる個別のリファレンス設計を維持するのではなく、リファレンス設計パラメーターをカスタマイズして、さまざまなインターフェイスの選択肢やデータ幅をパラメーターとしてもつ 1 つのリファレンス設計を作成します。CustomizeReferenceDesignFcn メソッドを使用して、インターフェイスまたはデータ幅のさまざまな選択肢をもつコールバック関数を参照できます。

たとえば、インターフェイスのデータ幅が異なる個別のリファレンス設計を作成するのではなく、データ幅をパラメーター化し、1 つのリファレンス設計パラメーターを作成できます。IP Core Generationワークフローを実行するときに、パラメーターを使用して、使用するデータ幅を選択できます。同様に、複数のリファレンス設計を使用せずに、AXI4-Stream マスター インターフェイスのみまたは AXI4-Stream スレーブ インターフェイスのみ、あるいは AXI4-Stream マスターと AXI4-Stream スレーブ両方のインターフェイスをもつ 1 つのリファレンス設計を作成できます。

リファレンス設計のカスタマイズ機能

コールバック関数を定義するには、次のようにします。

plugin_rdファイルで、addParameterメソッドを使用して、カスタマイズするリファレンス設計パラメーターを定義します。コールバック関数を定義する MATLAB® ファイルを作成します。コールバック関数の任意の名前を使用できます。

plugin_rd.mファイルと同じフォルダーにコールバック関数を保存します。CustomizeReferenceDesignFcnを使用して、コールバック関数の関数ハンドルをリファレンス設計定義plugin_rdファイルに登録します。

異なるリファレンス設計のカスタマイズを使用するには、次のようにします。

HDL ワークフロー アドバイザーを開きます。[ターゲット デバイスおよび合成ツールを設定] タスクで、[ターゲット ワークフロー] として

[IP Core Generation]を選択した後に、[ターゲット プラットフォーム] として独自のカスタム リファレンス設計を作成したターゲット ボードを選択します。[ターゲットのリファレンス設計を設定] タスクで、ターゲット ボード用にカスタマイズするカスタム リファレンス設計を選択すると、HDL Coder™ によってリファレンス設計パラメーターが設定されます。指定したインターフェイス タイプなど、パラメーターの選択に応じて、コールバック関数が評価されます。このタスクを実行します。

[ターゲット インターフェイスを設定] タスクを選択します。前の手順で選択したパラメーターに応じて、[ターゲット プラットフォーム インターフェイス テーブル] にターゲット インターフェイスの選択が入力されます。

カスタマイズ可能なリファレンス設計のパラメーター

コールバック関数で、これらのリファレンス設計パラメーターをカスタマイズできます。これらのパラメーターは plugin_rd ファイルで指定しないでください。

ブロック設計 Tcl ファイル

% ... % if ~isempty(ParamValue) hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'xilinx.com:zc706:part0:1.0'}; % ...

リファレンス設計インターフェイスおよびリファレンス設計インターフェイスのプロパティ

たとえば、AXI4-Stream マスター チャネルのデータ幅をパラメーター化できます。この例では、

plugin_rdファイルではなく、コールバック関数のaddAXI4StreamInterfaceメソッドを使用します。% ... % Add AXI4-Stream interface by parameterizing data width DataWidth = hRD.getParamValue(paramValue) if ~isempty(DataWidth) hRD.addAXI4StreamInterface( 'MasterChannelEnable', 'true', ... 'SlaveChannelEnable', 'true', ... 'MasterChannelConnection', 'ByPass_0.AXI4_Stream_Slave', ... 'SlaveChannelConnection', 'ByPass_0.AXI4_Stream_Master', ... 'MasterChannelDataWidth', DataWidth, ... 'SlaveChannelDataWidth', DataWidth); end % ...

IP リポジトリ

コールバック関数で、IP リポジトリを追加する場合、ブロック設計 Tcl ファイルを指定しなければなりません。

% ... %% Add IP Repository hRD.addIPRepository(... 'IPListFunction', 'mathworks.hdlcoder.vivado.hdlcoder_video_iplist', 'NotExistMessage', 'IP repository not found'); %% Add custom design files hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'em.avnet.com:zed:part0:1.0'); % ...

メモ

コールバック関数のリファレンス設計名、ボード名、サポートされるツール バージョンは変更できません。これらのパラメーターは、[ターゲットのリファレンス設計を設定] タスクでターゲットのリファレンス設計が選択されたときに、コールバック関数が評価される前に [ターゲット デバイスおよび合成ツールを設定] タスクで使用されます。

例: マスターのみまたはスレーブのみあるいはスレーブとマスター両方のリファレンス設計の作成

複数のリファレンス設計を使用せずに、AXI4-Stream マスター インターフェイスのみまたは AXI4-Stream スレーブ インターフェイスのみ、あるいは AXI4-Stream マスターと AXI4-Stream スレーブ両方のインターフェイスをもつ 1 つのリファレンス設計を作成できます。この例では、Xilinx Zynq ZC706 evaluation kit の独自のリファレンス設計をターゲットにするときに使用する AXI4-Stream インターフェイス チャネルをカスタマイズする方法を示します。

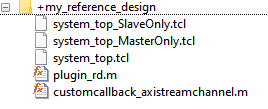

次のコードは、plugin_rd ファイルの addParameter メソッドを使用して指定されたリファレンス設計 my_reference_design のリファレンス設計パラメーターとインターフェイスの選択を示しています。CustomizeReferenceDesignFcn メソッドは、customcallback_axistreamchannel という名前のコールバック関数を参照します。

function hRD = plugin_rd() % Reference design definition % Copyright 2017-2019 The MathWorks, Inc. % Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); hRD.ReferenceDesignName = 'Vivado Custom Reference Design'; hRD.BoardName = 'Xilinx Zynq ZC706 evaluation kit'; % Tool information hRD.SupportedToolVersion = {'2019.1'}; % ... % ... % Parameter For calling AXI4 Master interface from Callback function hRD.addParameter ... ('ParameterID' , 'stream_channel', ... 'DisplayName' , 'Stream Channel', ... 'DefaultValue' , 'Both Master and Slave',... 'ParameterType' , hdlcoder.ParameterType.Dropdown, ... 'Choice' , {'Both Master and Slave','Master Only','Slave Only'}); % Reference the callback function. hRD.CustomizeReferenceDesignFcn = @my_reference_design.customcallback_axistreamchannel; % ...

コールバック関数を作成するときに、引数 infoStruct を関数に渡します。この引数には、リファレンス設計とボードに関する情報が structure 形式で含まれます。次のコードは、addAXI4StreamInterface メソッドを使用して指定された AXI4-Stream マスター チャネルまたはスレーブ チャネルもしくは両方のチャネルをもつコールバック関数 customcallback_axistreamchannel を示しています。

% Control AXI Master or Slave channel selection by using callback function function customcallback_axistreamchannel(infoStruct) %% Reference design callback run at the end of the task Set Target Reference Design % % infoStruct: information in structure format % infoStruct.ReferenceDesignObject: current reference design registration object % infoStruct.BoardObject: current board registration object % infoStruct.ParameterStruct: custom parameters of the current reference design, in struct format % infoStruct.HDLModelDutPath: the block path to the HDL DUT subsystem % infoStruct.ReferenceDesignToolVersion: Reference design Tool Version set in 1.2 Task paramStruct = infoStruct.ParameterStruct; if ~isempty(paramStruct) paramIDCell = fieldnames(paramStruct); paramValue = ''; for ii = 1:length(paramIDCell) paramID = paramIDCell(ii); if strcmp(paramID,'Both Master and Slave') paramValue = paramStruct.paramID; break; elseif strcmp(paramID,'Master Only') paramValue = paramStruct.paramID; break; elseif strcmp(paramID,'Slave Only') paramValue = paramStruct.paramID; break; end end end interface_type = str2double(paramValue); if ~isempty(interface_type) if strcmp(interface_type, 'Both Master and Slave') % add custom vivado design hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'xilinx.com:zc706:part0:1.0'); hRD.addAXI4StreamInterface( ... 'MasterChannelEnable', 'true', ... 'SlaveChannelEnable', 'true', ... 'MasterChannelConnection', 'axi_dma_s2mm/S_AXIS_S2MM', ... 'SlaveChannelConnection', 'axi_dma_mm2s/M_AXIS_MM2S', ... 'MasterChannelDataWidth', 32, ... 'SlaveChannelDataWidth', 32); elseif strcmp(interface_type, 'Master Only') % add custom vivado design hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'xilinx.com:zc706:part0:1.0'); hRD.addAXI4StreamInterface( ... 'MasterChannelEnable', true, ... 'MasterChannelConnection', 'axi_dma_s2mm/S_AXIS_S2MM', ... 'MasterChannelDataWidth', 32); % ...

plugin_rd ファイルと同じフォルダーにコールバック関数を保存します。

[ターゲット プラットフォーム] として Xilinx Zynq ZC706 evaluation kitを使用する IP Core Generationワークフローを実行すると、[ターゲットのリファレンス設計を設定] タスクに [Stream Channel] パラメーターが表示されます。

使用するリファレンス設計タイプを指定してから、ターゲット プラットフォームのインターフェイスを指定するワークフローを実行し、HDL IP コアを生成して IP コアをリファレンス設計に統合できます。

参考

hdlcoder.Board | hdlcoder.ReferenceDesign