カスタム リファレンス設計のためのカスタム パラメーターおよびコールバック関数の定義

カスタム リファレンス設計を定義する場合、オプションで hdlcoder.ReferenceDesign オブジェクトのプロパティを使用してカスタム パラメーターおよびコールバック関数を定義します。

カスタム パラメーターの定義およびコールバック関数ハンドルの登録

この MATLAB® コードは、カスタム パラメーターの登録方法およびリファレンス設計定義関数内にあるカスタム コールバック関数の関数ハンドルの登録方法を示します。

function hRD = plugin_rd() % Reference design definition % Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); hRD.ReferenceDesignName = 'My Reference Design'; hRD.BoardName = 'ZedBoard'; % Tool information hRD.SupportedToolVersion = {'2020.2'}; %% Add custom design files % ... % ... %% Add optional custom parameters by using addParameter property. % Specify custom 'DUT path' and 'Channel Mapping' parameters. % The parameters get populated in the 'Set Target Reference Design' % task of the HDL Workflow Advisor. hRD.addParameter( ... 'ParameterID', 'DutPath', ... 'DisplayName', 'Dut Path', ... 'DefaultValue', 'Rx', ... 'ParameterType', hdlcoder.ParameterType.Dropdown, ... 'Choice', {'Rx', 'Tx'}); hRD.addParameter( ... 'ParameterID', 'ChannelMapping', ... 'DisplayName', 'Channel Mapping', ... 'DefaultValue', '1'); %% Enable AXI manager IP insertion for the JTAG connection. The IP % insertion setting is visible in the 'Set Target Reference Design' % task of the HDL Workflow Advisor. By default, the % AddMATLABAXIManagerParameter property is set to 'true'. hRD.AddMATLABAXIManagerParameter = 'true'; hRD.MATLABAXIManagerDefaultValue = 'JTAG'; %% Enable AXI manager IP insertion for the PL Ethernet connection. The IP % insertion setting is visible in the 'Set Target Reference Design' % task of the HDL Workflow Advisor. By default, the PL Ethernet option % for the AXI manager IP insertion setting is available for the % Artix-7 35T Arty, Kintex-7 KC705, and Virtex-7 VC707 boards. % Enable this option for other Xilinx boards that have the Ethernet % physical layer (PHY) by adding the Ethernet media access % controller (MAC) Hub IP in the plugin_board file before launching % the HDL Workflow Advisor. To add the Ethernet MAC Hub IP, use % the addEthernetMACInterface method. hRD.AddMATLABAXIManagerParameter = 'true'; hRD.MATLABAXIManagerDefaultValue = 'PL Ethernet'; %% Add custom callback functions. These are optional. % With the callback functions, you can enable custom % validations, customize the project creation, software % interface model generation, and the bistream build. % Register the function handle of these callback functions. % Specify an optional callback for 'Set Target Reference Design' % task in Workflow Advisor. Use property name % 'PostTargetReferenceDesignFcn'. hRD.PostTargetReferenceDesignFcn = ... @my_reference_design.callback_PostTargetReferenceDesign; % Specify an optional callback for 'Set Target Interface' task in Workflow Advisor. % Use the property name 'PostTargetInterfaceFcn'. hRD.PostTargetInterfaceFcn = ... @my_reference_design.callback_PostTargetInterface; % Specify an optional callback for 'Generate IP Core' task hRD.PostGenerateIPCoreFcn =... @my_reference_design.callback_PostGenerateIPCoreFcn; % Specify an optional callback for 'Create Project' task % Use the property name 'PostCreateProjectFcn' for the ref design object. hRD.PostCreateProjectFcn = ... @my_reference_design.callback_PostCreateProject; % Specify an optional callback for 'Generate Software Interface Model' task % Use the property name 'PostSWInterfaceFcn' for the ref design object. hRD.PostSWInterfaceFcn = ... @my_reference_design.callback_PostSWInterface; % Specify an optional callback for 'Build FPGA Bitstream' task % Use the property name 'PostBuildBitstreamFcn' for the ref design object. hRD.PostBuildBitstreamFcn = ... @my_reference_design.callback_PostBuildBitstream; % Specify an optional callback for 'Program Target Device' % task to use a custom programming method. hRD.CallbackCustomProgrammingMethod = ... @my_reference_design.callback_CustomProgrammingMethod; %% Add interfaces % ... % ...

カスタム パラメーターの定義

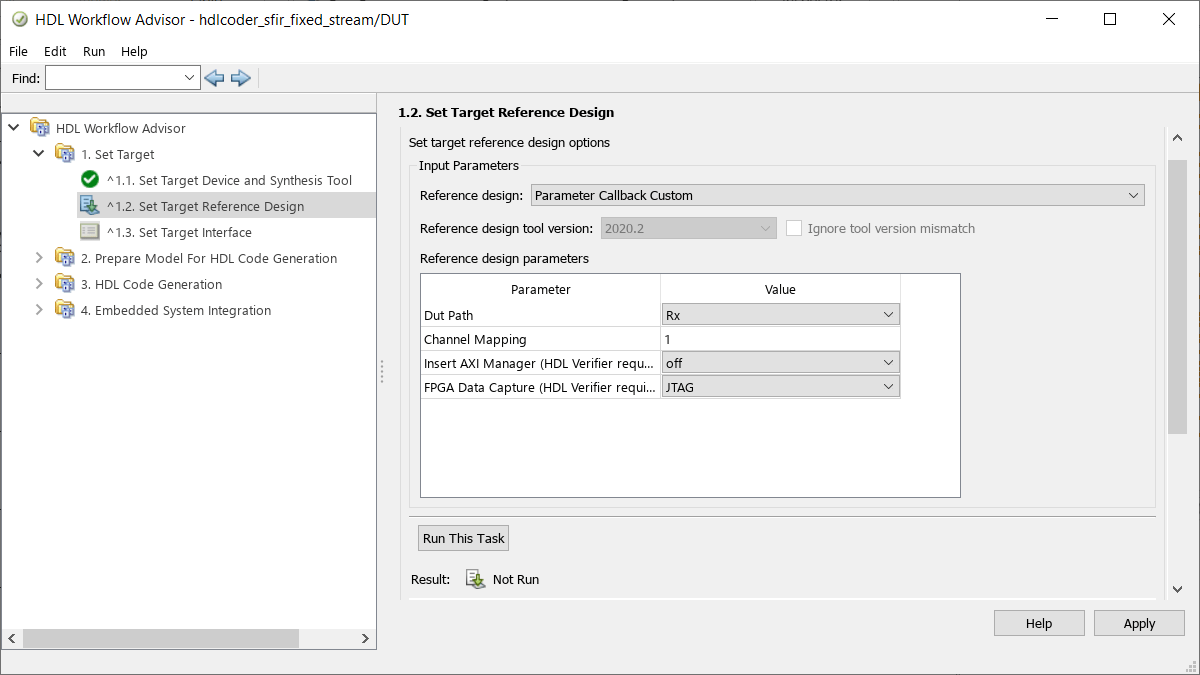

hdlcoder.ReferenceDesign クラスの addParameter メソッドを使用して、カスタム パラメーターを定義できます。前述のコード例では、リファレンス設計は 2 つのカスタム パラメーター DUT Path および Channel Mapping を定義します。addParameter メソッドの詳細については、addParameterを参照してください。

AXI Manager IP の挿入の指定

既定では、HDL Coder™ によって [Insert AXI Manager (HDL Verifier required)] パラメーターがすべてのリファレンス設計に追加されます。このパラメーターを [JTAG] に設定すると、コード ジェネレーターによって JTAG AXI Manager IP がリファレンス設計に挿入されます。このパラメーターを [PL Ethernet] に設定すると、コード ジェネレーターによって UDP AXI Manager IP がリファレンス設計に挿入されます。

メモ

既定では、PL イーサネット接続は Artix®-7 35T Arty ボード、Kintex®-7 KC705 ボード、および Virtex®-7 VC707 ボードでのみ使用できます。この接続をイーサネット物理レイヤー (PHY) を備えた他の Xilinx® ボードで有効にするには、HDL ワークフロー アドバイザー ツールを起動する前に、addEthernetMACInterface メソッドを使用して plugin_board ファイルに手動でイーサネット メディア アクセス コントローラー (MAC) ハブ IP を追加します。

AXI Manager IP を使用すると、ハードウェア ボードで生成された DUT IP コアの AXI レジスタに、JTAG またはイーサネット接続を通じて MATLAB または Simulink® から簡単にアクセスできます。AXI Manager のセットアップ (HDL Verifier)も参照してください。

この機能を使用するには、HDL Verifier™ ハードウェアのサポート パッケージがインストールされ、ダウンロードされていなければなりません。FPGAボードサポートパッケージをダウンロード (HDL Verifier)を参照してください。

コード ジェネレーターは、AXI Manager IP 接続に対応するように [AXI4 下位 ID の幅] を調整します。HDL IP コアを生成してリファレンス設計プロジェクトを作成すると、Vivado® ブロック設計を開いてリファレンス設計に挿入されている AXI Manager IP を表示できます。

前述のコード例では、リファレンス設計により hdlcoder.ReferenceDesign クラスの AddMATLABAXIManagerParameter プロパティと MATLABAXIManagerDefaultValue プロパティが定義されます。これらのプロパティは、HDL ワークフロー アドバイザーの [ターゲットのリファレンス設計を設定] タスクで [Insert AXI Manager (HDL Verifier required)] 設定の既定の動作を制御します。hdlcoder.ReferenceDesign クラスでこれらのプロパティのいずれも指定しない場合、[Insert AXI Manager (HDL Verifier required)] パラメーターは [ターゲットのリファレンス設計を設定] タスクに表示され、値は [off] に設定されます。このコード例は、既定の動作を説明しています。

このプロパティは、HDL ワークフロー アドバイザーの [ターゲットのリファレンス設計を設定] タスクで [Insert AXI Manager (HDL Verifier required)] パラメーターの可視性を制御します。既定では、このプロパティの値は 'true' です。これは、タスクでパラメーターが表示されることを意味します。このパラメーターを無効にするには、この値を 'false' に設定します。

hRD.AddMATLABAXIManagerParameter = 'true';このプロパティは、[ターゲットのリファレンス設計を設定] タスクで [Insert AXI Manager (HDL Verifier required)] パラメーターの値を制御します。既定では、このプロパティの値は 'off' です。これは、パラメーターがタスクで表示され、値が [off] であることを意味します。リファレンス設計で AXI Manager IP の自動挿入を有効にするには、この値を 'JTAG' または 'PL Ethernet' に設定します。このケースでは、AddMATLABAXIManagerParameter を 'true' に設定しなければなりません。

hRD.MATLABAXIManagerDefaultValue = 'off';

以下の例を参照してください。

IP コアの生成ワークフローの実行

HDL ワークフロー アドバイザーを開くと、HDL Coder により [ターゲットのリファレンス設計を設定] タスクにリファレンス設計名、ツール バージョン、指定したカスタム パラメーターが入力され、[Insert AXI Manager (HDL Verifier required)] オプションが [JTAG] に設定されます。

HDL Coder は次に、これらのパラメーター値をコールバック関数の入力構造体に渡します。

合成ツールが Xilinx Vivado である場合、HDL Coder はリファレンス設計のパラメーター値を変数に設定します。変数は、ブロック設計の Tcl ファイルの入力となります。このコードの抜粋は、リファレンス設計プロジェクト作成の Tcl ファイルの例です。

update_ip_catalog

set DutPath {Rx}

set ChannelMapping {1}

source vivado_custom_block_design.tcl

コードは、HDL Coder がカスタム ブロック設計の Tcl ファイルに値を設定する前に、リファレンス設計パラメーターを設定する方法を示します。

コールバック関数ハンドルの登録

リファレンス設計定義では、カスタム コールバック関数を参照するために関数ハンドルを登録できます。次を行うことができます。

カスタム検証を有効にする。

リファレンス設計を動的にカスタマイズします。

リファレンス設計プロジェクト作成の設定をカスタマイズ。

生成されたソフトウェア インターフェイス モデルを変更。

FPGA ビットストリームのビルド プロセスをカスタマイズ。

カスタム FPGA プログラミング方法を指定。

hdlcoder.ReferenceDesign クラスを使用して、コールバックのプロパティ名を定義できます。コールバック プロパティには命名規則があります。コールバック関数には任意の名前を指定できます。HDL ワークフロー アドバイザーでは、コールバック関数を定義して次のタスクをカスタマイズできます。

| ワークフロー アドバイザーのタスク | コールバックのプロパティ名 | 機能 |

|---|---|---|

ターゲットのリファレンス設計を設定 |

|

|

ターゲット インターフェイスを設定 | PostTargetInterfaceFcn | カスタム検証を有効にする。特定のカスタム パラメーター設定向けに特定のインターフェイスを選択していないことを確認する方法を示す例については、 |

IP コアを生成 | PostGenerateIPCoreFcn | HDL Coder で IP コアが生成された後に実行するカスタム タスクを指定します。例については、 |

プロジェクトを作成 | PostCreateProjectFcn | HDL Coder がプロジェクトを作成するときにカスタム設定を指定します。例については、 |

ソフトウェア インターフェイスの生成 | PostSWInterfaceFcn | 生成されたソフトウェア インターフェイス モデルを変更。例については、 |

FPGA ビットストリームのビルド | PostBuildBitstreamFcn | FPGA ビットストリームを作成するときにカスタム設定を指定します。この関数を使用する場合、ビルド プロセスを外部で実行することはできません。[FPGA ビットストリームのビルド] タスクの [ビルド プロセスを外部で実行] チェック ボックスをオフにして、ビルド プロセスを HDL ワークフロー アドバイザー内で実行しなければなりません。例については、 |

ターゲット デバイスをプログラム | CallbackCustomProgrammingMethod | カスタムの FPGA プログラミング メソッドを指定します。例については、 |

カスタムのコールバック関数の定義

HDL Coder がタスクの実行後に実行する各コールバック関数について、任意の名前をもつ MATLAB 関数を定義するファイルを作成します。

コールバック関数には、ドキュメンテーションにある入力引数と出力引数があることを確認します。

MATLAB パスから関数にアクセスできることを確認します。

コールバック関数の関数ハンドルをリファレンス設計定義関数に登録します。

コールバックのプロパティ名の命名規則に従います。

これらのコールバック関数の詳細については、hdlcoder.ReferenceDesign を参照してください。

参考

hdlcoder.Board | hdlcoder.ReferenceDesign