このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

DUT AXI4 スレーブ インターフェイスにアクセスするためのリファレンス設計での複数の AXI Master インターフェイスの定義

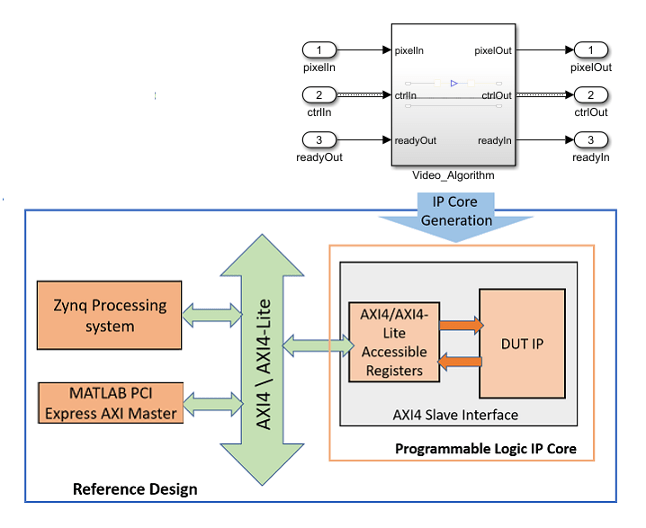

カスタム リファレンス設計で複数の AXI Master インターフェイスを定義して、DUT 向けに生成された HDL DUT IP コアで AXI4 スレーブ インターフェイスにアクセスできます。この機能により、Zynq® プロセッシング システムの HDL Verifier™ JTAG AXI Manager IP および ARM® プロセッサなどのリファレンス設計で HDL DUT IP コアを 2 つ以上の AXI Master IP に同時に接続できます。

Vivado ベースのリファレンス設計

複数の AXI Master インターフェイスを定義するには、各 AXI Master インスタンスについて BaseAddressSpace および MasterAddressSpace を指定します。設計によっては、IDWidth プロパティの指定も必要な場合があります。ID の幅の詳細については、IDWidthを参照してください。

このコードは、Vivado® ベースのリファレンス設計で複数の AXI Master インターフェイスを指定する際の MasterAddressSpace フィールドの構文です。

'MasterAddressSpace', ...

{'AXI Master Instance Name1/Address Space of Instance Name1', ...

'AXI Master Instance Name2/Address_Space of Instance Name2',...};たとえば、このコードは plugin_rd ファイルを変更して 2 つの AXI Master インターフェイスを定義する方法を示しています。

% ... %% Add custom design files % add custom Vivado design hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'xilinx.com:zc706:part0:1.0'); % ... % ... % The DUT IP core in this reference design is connected % to both Zynq Processing System and the AXI Manager IP. hRD.addAXI4SlaveInterface( ... 'InterfaceConnection', 'axi_interconnect_0/M00_AXI', ... 'BaseAddress', {'0x40010000', '0x40010000'}, ... 'MasterAddressSpace', {'processing_system7_0/Data', 'hdlverifier_axi_manager_0/axi4m'}, ... ); % ...

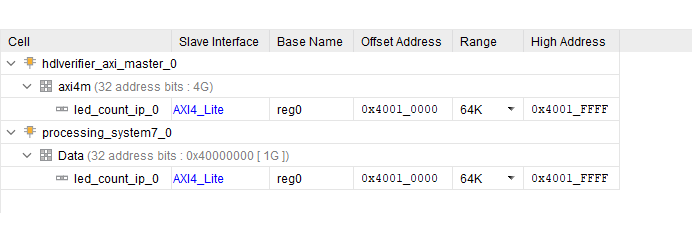

この例では、2 つの AXI Master IP は、HDL Verifier の AXI Manager IP と ARM プロセッサです。MasterAddressSpace の構文に基づき、HDL Verifier の AXI Manager IP は、AXI Master Instance Name が hdlverifier_axi_manager_0、Address_Space of Instance Name が axi4m です。

HDL DUT IP コアの AXI4 スレーブ インターフェイスは addAXI4SlaveInterface メソッドの InterfaceConnection プロパティで定義される Xilinx® AXI Interconnect IP に接続します。AXI4 スレーブ インターフェイスには BaseAddress があります。この BaseAddress は 2 つの AXI Master IP の MasterAddressSpace にマッピングしなければなりません。これは文字ベクトルの cell 配列として指定されます。

AXI Master IP は既に Vivado リファレンス設計プロジェクトに含まれていることを確認しなければなりません。system_top.tcl は addCustomVivadoDesign メソッドの CustomBlockDesignTcl プロパティで定義される TCL ファイルです。この TCL ファイルで、2 つの AXI Master IP が同じ Xilinx AXI Interconnect IP に接続されていることを確認しなければなりません。この相互接続で、AXI Master IP が HDL IP コアの AXI4 スレーブ インターフェイスに接続されます。

IP Core Generation ワークフローを実行して Vivado プロジェクトを作成した後、プロジェクトを開きます。Vivado プロジェクトで、ブロック設計を開くと、2 つの AXI Master IP が HDL DUT IP コアに接続されていることが確認できます。[Address Editor] タブを選択すると、AXI Master のインスタンス名と対応するアドレス空間を確認できます。

Qsys ベースのリファレンス設計

複数の AXI Master インターフェイスを定義するには、各 AXI Master インスタンスについて BaseAddressSpace および MasterAddressSpace を指定します。設計によっては、IDWidth プロパティの指定も必要な場合があります。ID の幅の詳細については、IDWidthを参照してください。

このコードは、Qsys™ ベースのリファレンス設計で複数の AXI Master インターフェイスを指定する際の InterfaceConnection フィールドの構文です。

'InterfaceConnection', ...

{'AXI Master Instance Name1/Port name of Instance Name1', ...

'AXI Master Instance Name2/Port name of Instance Name1', ...};たとえば、このコードは plugin_rd ファイルを変更して 3 つの AXI Master インターフェイスを定義する方法を示しています。

% ... %% Add custom design files % add custom Qsys design hRD.addCustomQsysDesign('CustomQsysPrjFile', 'system_soc.qsys'); hRD.CustomConstraints = {'system_soc.sdc','system_setup.tcl'}; % ... % add AXI4 slave interfaces hRD.addAXI4SlaveInterface( ... 'InterfaceConnection', {'hps_0.h2f_axi_master','master_0.master','AXI_Manager_0.axm_m0'}, ... 'BaseAddress', {'0x0000_0000','0x0000_0000','0x0000_0000'},... 'InterfaceType', 'AXI4'); % ...

InterfaceConnection オプションの構文に基づき、HDL Verifier の AXI Manager IP は、AXI Master Instance Name が AXI_Manager_0、Port name が axm_m0 です。各 AXI Master IP は、HDL IP コアの BaseAddress と InterfaceConnection で、文字ベクトルの cell 配列として指定しなければなりません。

AXI Master IP は既に Qsys リファレンス設計プロジェクトに含まれていることを確認しなければなりません。system_soc.qsys は addCustomQsysDesign メソッドの CustomQsysPrjFile プロパティで定義されるファイルです。このファイルで、2 つの AXI Master IP が同じ Qsys AXI Interconnect IP に接続されていることを確認しなければなりません。

この相互接続で、AXI Master IP が HDL IP コアの AXI4 スレーブ インターフェイスに接続されます。

IP Core Generation ワークフローを実行して Quartus® プロジェクトを作成した後、プロジェクトを開きます。Quartus プロジェクトで、3 つの AXI Master IP と AXI Master インターフェイスが DUT の HDL IP コアに接続されていることが確認できます。[Address Map] タブを選択すると、AXI Master のインスタンス名、端子名、および対応するアドレス空間を確認できます。

参考

hdlcoder.Board | hdlcoder.ReferenceDesign